文章來源:老虎說芯

原文作者:老虎說芯

本文介紹了在集成電路制造工藝中的High-K材料的特點、重要性、優(yōu)勢,以及工藝流程和面臨的挑戰(zhàn)。

DRAM(動態(tài)隨機存取存儲器)是一種常見的內存芯片,就像我們家里的儲藏室,用來短暫存放數據(“0”或“1”)。DRAM最基本的結構就是由一個晶體管(相當于開關)和一個電容(相當于儲藏室)組成的“1T1C”單元。

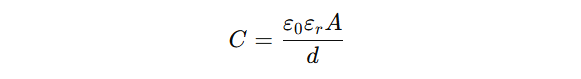

隨著芯片尺寸不斷縮小(從28納米縮小到10納米以下),電容這個“小儲藏室”的面積(A)急劇減小,但存儲能力(電容值C)卻不能降低。按照公式:

面積變小了,要維持容量,就只能減薄介質層厚度(d)。但傳統硅氧化物(SiO?,介電常數ε_r≈3.9)一旦變得極薄(例如1納米左右),漏電流就會指數級增加,導致電荷快速流失,數據無法穩(wěn)定保存。

核心原理篇:High-K材料如何破解難題?

High-K(高介電常數)材料,就是指介電常數(ε_r)比傳統SiO?高數倍甚至十幾倍的新材料,如氧化鉿(HfO?,ε_r≈25)、氧化鋯(ZrO?,ε_r≈30)等。

通俗地講,如果將電容比作“蓄水池”,則介電常數越高,就好比蓄水池內壁更加厚實,不容易“滲漏”,即便把“蓄水池”面積造得更小,也仍能保持足夠水量,不必犧牲內壁厚度。

工藝流程篇:如何將High-K材料引入芯片制造?

引入High-K材料主要有以下關鍵工藝:

1.選材與沉積工藝(ALD)

通過原子層沉積技術(Atomic Layer Deposition, ALD)精確沉積極薄均勻的高K薄膜。這就像用3D打印機逐層鋪設墻磚,每一層都精準一致,從而確保膜厚度均勻可靠。

2.界面優(yōu)化工程

High-K材料與硅晶圓表面直接接觸會產生缺陷(就像新粉刷的墻面不光滑),需用特殊處理工藝(例如氮化處理或加入極薄SiO?過渡層)修復這些缺陷,確保“墻面”光滑、平整,提高芯片性能與可靠性。

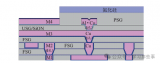

3.結合3D電容結構

此外,芯片設計師還將High-K材料與立體的圓柱或溝槽結構電容結合。類比為在原本平面的停車場上搭建多層停車庫,大幅提升有效面積,使電容值進一步增強。

優(yōu)勢篇:High-K材料的三大技術紅利

1.性能提升

因為High-K材料厚度更厚,電子“漏出”概率大幅降低,這有效延長了數據保存時間。同時,由于電容充放電效率更高,芯片數據讀寫速度也提升顯著,可適用于更高頻的DDR5、LPDDR5甚至未來的DDR6標準。

2.功耗降低

漏電減少,意味著不需要頻繁刷新數據,直接降低芯片的動態(tài)功耗。同時,厚度增加意味著電場強度減小,也能有效降低靜態(tài)功耗。

3.工藝兼容性強

現有芯片產線可較平穩(wěn)地導入ALD沉積High-K材料的步驟,這對于先進制程(如10納米以下)至關重要。

技術難點篇:實現High-K材料的挑戰(zhàn)有哪些?

盡管優(yōu)勢突出,但High-K技術面臨三大關鍵挑戰(zhàn):

1.工藝復雜、成本高昂

ALD設備價格高昂、沉積工藝精細化,直接導致芯片生產成本上升;同時,鉿(Hf)、鋯(Zr)等稀有元素本身成本也較高。

2.界面缺陷控制難度大

High-K材料與硅表面接觸容易形成界面缺陷,嚴重時將影響芯片穩(wěn)定性。這對晶圓制造廠商的技術積累和品控能力提出極高要求。

3.長期可靠性與壽命問題

長期工作下High-K材料可能發(fā)生“氧空位遷移”,導致芯片性能(如閾值電壓)漂移,可靠性降低。針對該問題,需要引入特殊摻雜工藝,如摻入鑭(La)或硅(Si),或構建多層復合結構以抑制氧空位遷移。

未來展望篇:下一個十年High-K技術往哪里去?

技術進步永不止步,未來High-K材料仍有巨大創(chuàng)新空間:

1.新材料探索

鐵電氧化鉿(Fe-HfO?)材料兼具鐵電性和高介電常數,有望進一步增強電容特性,適合更高速、更高容量的下一代內存技術。

2.二維材料異質集成

與二維半導體材料(如二硫化鉬MoS?)結合,有望打破傳統硅材料和3D結構的物理極限,創(chuàng)造性能更佳的內存芯片。

3.人工智能輔助新材料開發(fā)

通過AI和機器學習快速篩選和優(yōu)化High-K材料及配方,加速工藝創(chuàng)新進程,顯著降低研發(fā)周期和成本。

總結篇:芯片制造離不開的關鍵技術

High-K介質就如同芯片產業(yè)的“隱形英雄”,它巧妙地平衡了芯片尺寸縮小和性能保持之間的根本矛盾。

-

芯片

+關注

關注

459文章

52350瀏覽量

438624 -

集成電路

+關注

關注

5420文章

12012瀏覽量

367793 -

制造工藝

+關注

關注

2文章

203瀏覽量

20312 -

芯片制造

+關注

關注

10文章

681瀏覽量

29626

原文標題:芯片制造為什么需要High-K材料

文章出處:【微信號:bdtdsj,微信公眾號:中科院半導體所】歡迎添加關注!文章轉載請注明出處。

發(fā)布評論請先 登錄

集成電路制造工藝中的High-K材料介紹

集成電路制造工藝中的High-K材料介紹

評論