文章來源:半導體與物理

原文作者:jjfly686

本文介紹了High-K材料的物理性質(zhì)、制備方法及其應用。

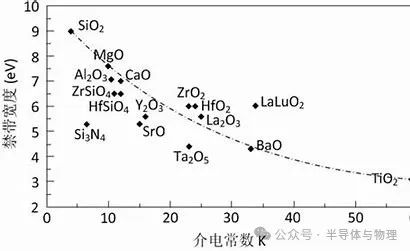

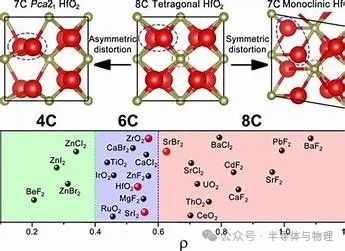

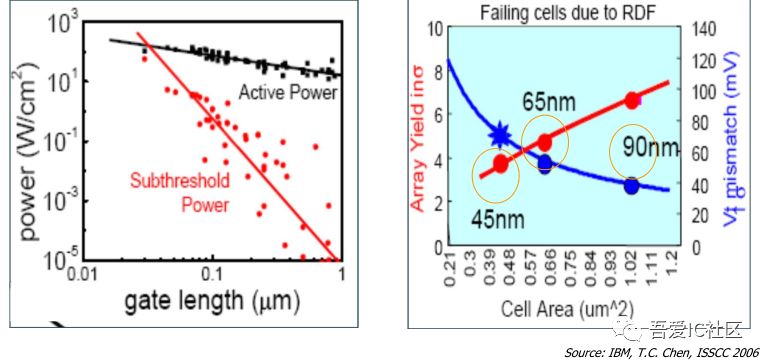

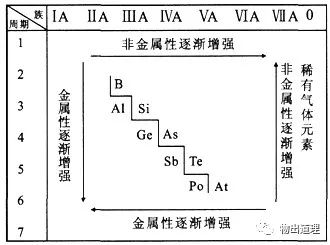

High-K材料(高介電常數(shù)材料)是介電常數(shù)顯著高于傳統(tǒng)二氧化硅(SiO?,k=3.9)的絕緣材料,主要用于替代柵極介質(zhì)層和電容介質(zhì)層。隨著芯片制程進入納米級,傳統(tǒng)SiO?因厚度過薄(<2 nm)引發(fā)嚴重的量子隧穿效應,導致漏電流激增和功耗失控。High-K材料的引入,可在相同電容下增加物理厚度(如HfO?的k=25,厚度可達SiO?的3-6倍),從而抑制漏電流并提升器件可靠性。

常見High-K材料及其物理性質(zhì)

| 材料 | 介電常數(shù)(k) | 熱穩(wěn)定性 | 應用場景 |

|---|---|---|---|

| HfO? | 20-25 | 易結晶 | 邏輯器件柵介質(zhì)、DRAM電容 |

| ZrO? | 25-30 | 易結晶 | DRAM電容、存儲介質(zhì) |

| TiO? | 30-80 | 易結晶 | 實驗性柵介質(zhì) |

| HfSiON | 15-20 | >1000℃ | 高溫兼容的柵介質(zhì)層 |

| HfO?-ZrO?復合 | 30-50 | 高 | DRAM電容 |

HfO?因兼具高k值和熱穩(wěn)定性,成為主流選擇;HfSiON(氮氧化鉿硅)通過摻氮優(yōu)化界面態(tài)密度,常用于高溫工藝。

ALD工藝合成HfO?與HfSiON

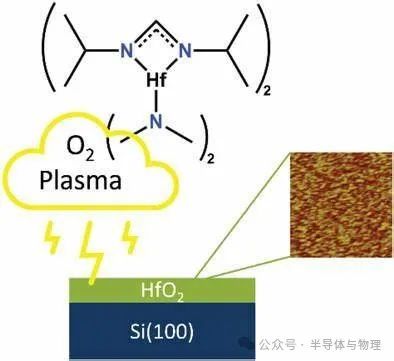

原子層沉積(ALD)是制備High-K薄膜的核心技術,可實現(xiàn)原子級厚度控制與三維結構保形性。

HfO?的ALD合成

前驅體:四(乙基甲基胺基)鉿(TEMAHf)或HfCl?作為鉿源,去離子水(H?O)或臭氧(O?)為氧源。

TEMAHf+H2O→HfO2+副產(chǎn)物氣體(如NH3)

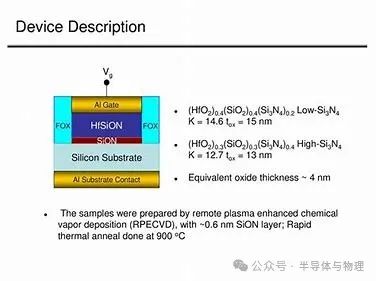

HfSiON的ALD合成

交替使用Hf前驅體(如TEMAHf)、硅源(如SiH?或硅烷衍生物)及氮源(NH?等離子體)。通過調(diào)節(jié)硅/氮的沉積比例,優(yōu)化薄膜的k值和界面特性。例如,摻氮可減少氧空位缺陷,提升熱穩(wěn)定性。

High-K材料在芯片制造中的應用

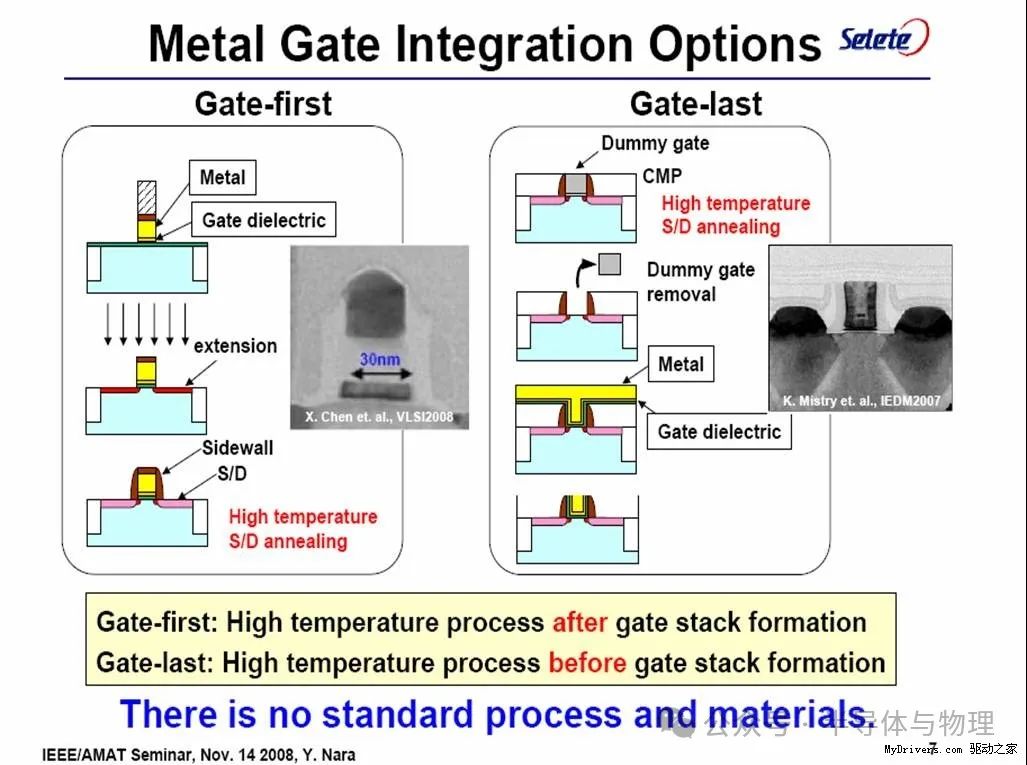

先柵HKMG工藝中的HfSiON

柵極在源漏注入前形成,需耐受高溫退火(>1000℃)。HfSiON因高熱穩(wěn)定性與Si襯底兼容,常與多晶硅柵結合,用于45 nm及以上制程。降低等效氧化層厚度(EOT),同時抑制硼穿透(PMOS中常見問題)。

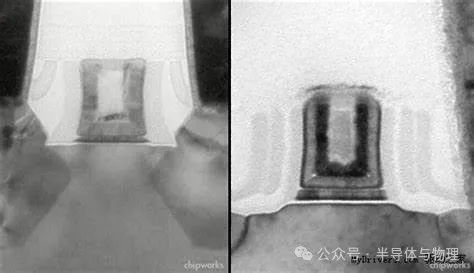

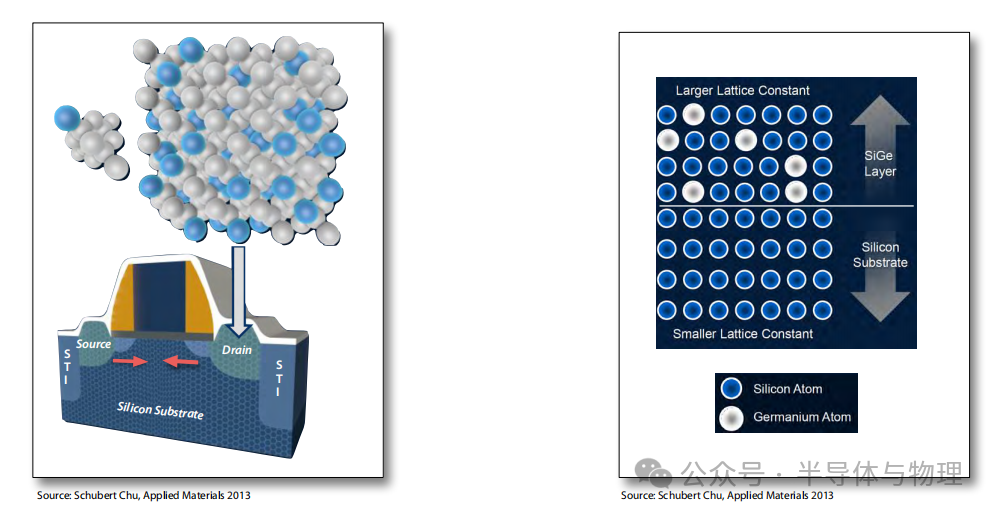

后柵HKMG工藝中的HfO?

先形成多晶硅偽柵,完成高溫工藝后替換為金屬柵(如TiN)。HfO?與金屬柵(如TiN/Al)結合,用于22 nm以下FinFET制程。避免高溫對金屬柵的損傷,實現(xiàn)更薄EOT(<1 nm)和更低漏電流。

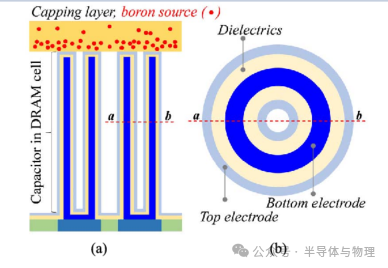

DRAM電容中的HfO?與ZrO?

在DRAM單元電容中,High-K材料(如HfO?/ZrO?堆疊)可大幅提升電容容量。

-

工藝

+關注

關注

4文章

671瀏覽量

29254 -

材料

+關注

關注

3文章

1320瀏覽量

27727 -

芯片制造

+關注

關注

10文章

676瀏覽量

29525 -

芯片制程

+關注

關注

0文章

53瀏覽量

4922

原文標題:芯片制造中的High-K材料

文章出處:【微信號:bdtdsj,微信公眾號:中科院半導體所】歡迎添加關注!文章轉載請注明出處。

發(fā)布評論請先 登錄

科普一下先進工藝22nm FDSOI和FinFET的基礎知識

【存儲器】IC芯片制造流程介紹

什么是本體偏壓/次臨界漏電 (ISUBTH)/High-k

專訪格羅方德Subramani Kengeri:28nm量產(chǎn)致勝關鍵在于HKMG

集成電路制造工藝升級的過程中,晶體管微縮會終結嗎?

芯片制造中的幾種關鍵材料及其代表企業(yè)盤點

高K介質(zhì)(High-k Dielectric)和替代金屬柵(RMG)工藝介紹

高K金屬柵極的結構、材料、優(yōu)勢以及工藝流程

High-k柵極堆疊技術的介紹

芯片制造中的半導體材料介紹

芯片制造中的High-K材料介紹

芯片制造中的High-K材料介紹

評論