文章來源:半導體與物理

原文作者:jjfly686

本文介紹了芯片制造中的Low-K材料。

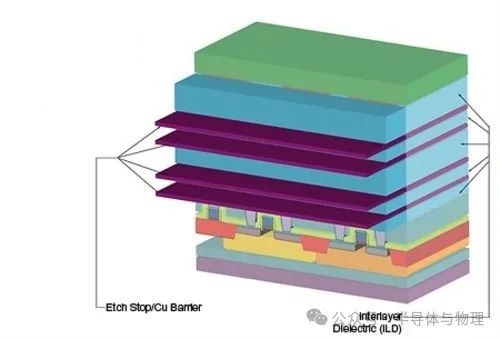

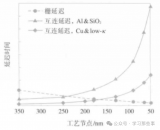

Low-K材料是介電常數顯著低于傳統二氧化硅(SiO?,k=3.9–4.2)的絕緣材料,主要用于芯片制造中的層間電介質(ILD)。其核心目標是通過降低金屬互連線間的寄生電容,解決RC延遲(電阻-電容延遲)和信號串擾問題,從而提升芯片性能和集成度。

Low-K材料在芯片中的作用

1. 降低RC延遲

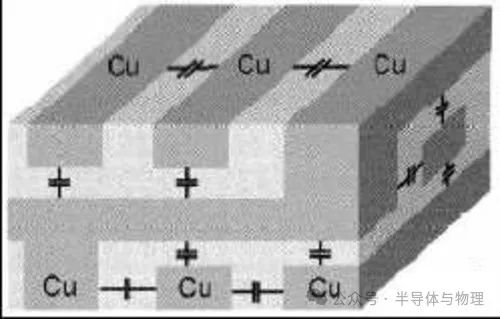

隨著芯片制程微縮,金屬互連線間距縮小,傳統SiO?的電容效應導致信號延遲和功耗增加。Low-K材料通過減少互連線間的寄生電容,使RC延遲降低并顯著提升芯片速度。

2. 抑制信號串擾

互連線間的耦合電容與k值成正比。Low-K材料通過降低k值,減少電容耦合效應,使相鄰線路的串擾噪聲降低,允許更密集的布線設計。

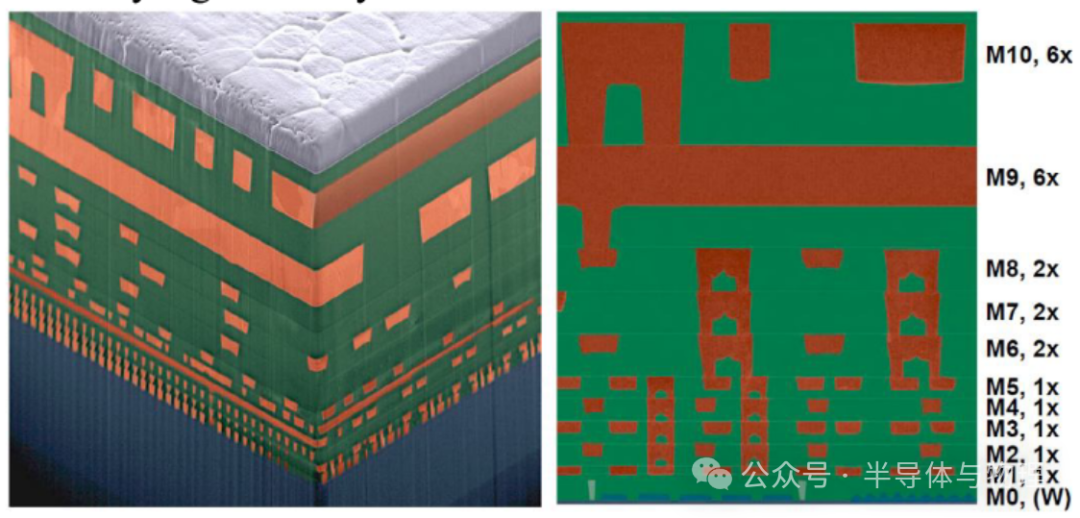

3. 支持多層互連結構

現代芯片采用10層以上的金屬互連,Low-K材料的高絕緣性和低熱膨脹系數可避免層間應力開裂,保障結構穩定性。

Low-K材料的分類與合成原料

Low-K材料根據成分可分為三大類,其合成工藝和原料差異顯著:

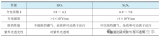

| 類型 | 典型材料 | 合成原料與工藝 | k值范圍 |

|---|---|---|---|

| 無機多孔材料 | 多孔氧化硅 | 溶膠-凝膠法,前驅體為TEOS | 2–2.5 |

| 有機高分子材料 | 聚酰亞胺、含氟聚合物 | 旋涂法,前驅體為聚酰亞胺單體或PTFE | 1.5–2.7 |

| 有機/無機復合材料 | 甲基倍半硅氧烷(MSQ) | CVD或旋涂,前驅體為硅氧烷衍生物 | 2.2–2.8 |

LOW-K材料工藝:

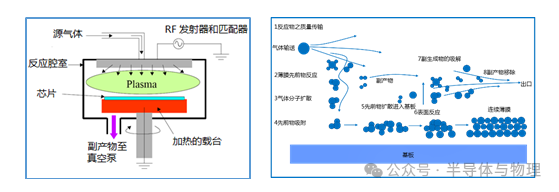

化學氣相沉積(CVD)

:用于沉積MSQ等材料,需使用含碳/氟前驅體(如SiCOH),通過PECVD提升薄膜致密度。

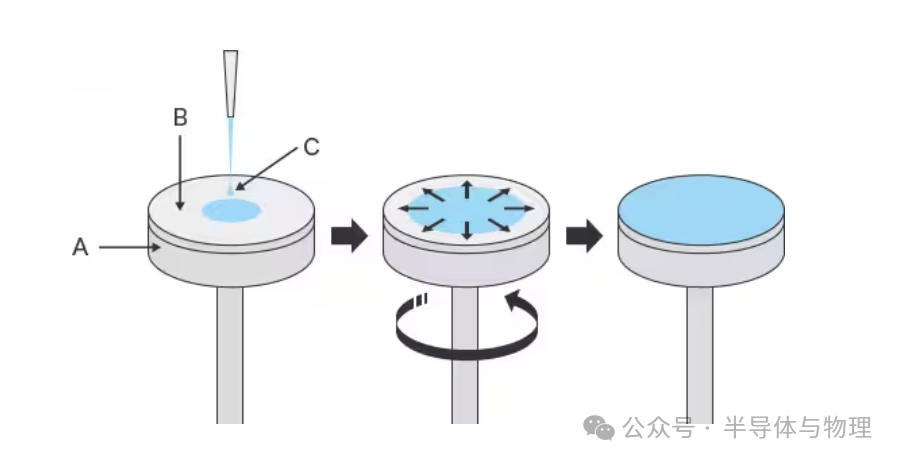

旋涂法

:適用于有機材料,需優化溶劑揮發速度以避免薄膜裂紋。

Low-K材料的制造工藝挑戰

1. 機械強度與熱穩定性

多孔材料易脆裂,需通過摻雜納米顆粒如SiO?納米球提升硬度。例如,摻入10% SiO?可使多孔Low-K薄膜的楊氏模量從3 GPa提升至8 GPa。

2. 銅擴散阻擋

Low-K材料的孔隙可能被銅原子滲透,需集成超薄阻擋層(如2nm的TiN)以防止互聯金屬銅擴散導致漏電。

3. CMP兼容性

材料疏松易導致拋光不均勻,需要使用壓力拋光液(如含二氧化鈰磨料)。

-

材料

+關注

關注

3文章

1342瀏覽量

27865 -

芯片制造

+關注

關注

10文章

685瀏覽量

29680 -

寄生電容

+關注

關注

1文章

299瀏覽量

19762

原文標題:芯片制造中的Low-K材料

文章出處:【微信號:bdtdsj,微信公眾號:中科院半導體所】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

藍牙芯片中的晶振:內部集成與功能解析

hmc704 BIAS引腳影響相噪請問這個引腳在芯片中起什么作用?

Scratch Testing of Low-k Diele

鎖相環是什么?在dsp芯片中有什么作用

金在芯片中有什么用途呢?金在芯片中的應用和優勢介紹

誤差放大器在LDO芯片中的作用

FIB制備Low-K材料的TEM樣品面臨難點

為什么芯片需要低介電常數材料

電子束對Low-K材料有什么影響

Low-K材料在芯片中的作用

Low-K材料在芯片中的作用

評論