本文介紹了芯片里的介質(zhì)及其性能。

介電常數(shù)k概述

在介質(zhì)薄膜的沉積過程中,除了薄膜質(zhì)量如均勻性、致密性、間隙填充及臺階覆蓋能力備受關(guān)注外,介質(zhì)材料的介電常數(shù)k也成為了焦點,因其直接關(guān)聯(lián)到芯片的性能表現(xiàn)。下面將深入探討介電常數(shù)k的重要性,并逐一闡述低k、超低k及高k材料的發(fā)展與應(yīng)用。

導(dǎo)電材料的介電常數(shù),是衡量材料在電場作用下存儲電能效率的關(guān)鍵指標,它反映了材料作為電容隔離層的效能。在集成電路制造領(lǐng)域,介電常數(shù)通常以k值表示,其中空氣的k值最低,為1。不同制備工藝得到的絕緣薄膜,其k值會有輕微差異,例如熱生長二氧化硅的k值約為3.9,而等離子體增強化學(xué)氣相沉積(PECVD)二氧化硅的k值則在4.1至4.3之間。

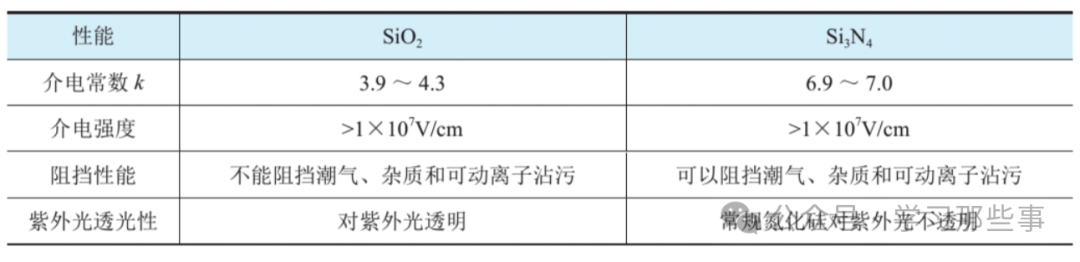

相較于二氧化硅,另一種常見絕緣介質(zhì)氮化硅的介電常數(shù)較高。盡管氮化硅在阻擋可動離子污染及防止硼磷硅酸鹽玻璃(BPSG)中的硼、磷擴散至晶體管源、漏區(qū)方面表現(xiàn)出色,但由于其較高的介電常數(shù)(6.9至7.0),會增加RC延遲,從而降低芯片速度。因此,在實際應(yīng)用中,常采用折中方案:先沉積一層較薄的氮化硅,主體介質(zhì)材料仍以二氧化硅為主。

二氧化硅與氮化硅的性能對比參見下表。芯片性能的一個重要衡量標準是信號傳輸速度。隨著芯片微型化需求的增長,金屬互連的線寬不斷縮小,導(dǎo)致傳輸信號導(dǎo)線的電阻R增大。同時,導(dǎo)線間距的減小也引發(fā)了寄生電容C的增加,進而加劇了RC信號延遲,降低了芯片速度。RC信號延遲,亦稱互連延遲,已成為制約芯片性能的關(guān)鍵因素之一。

從本質(zhì)上看,互連尺寸的減小帶來了寄生電阻和電容效應(yīng)的增強,從而導(dǎo)致了信號延遲的增加。然而,這與晶體管的發(fā)展趨勢相悖。隨著柵長的縮短,晶體管的延遲減小,速度提升。因此,我們不能僅憑互連延遲的增加就反對線寬的減小。因為線寬的減小不僅意味著晶體管速度的提升,還使得芯片更加輕便,便于攜帶。

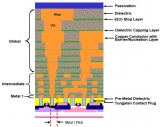

既然線寬的減小是必然趨勢,那么如何抵消RC信號延遲的增加呢?一方面,采用電阻率更低的銅替代傳統(tǒng)的鋁材料,以降低導(dǎo)線電阻R。另一方面,由于電容C與絕緣介質(zhì)的k值成正比,因此尋找低k材料以降低寄生電容C成為了關(guān)鍵。低k絕緣介質(zhì)的應(yīng)用有助于減小芯片的總互連電容,降低RC信號延遲,從而提升芯片性能。

低k材料

降低絕緣介質(zhì)的介電常數(shù)k值,能有效減少相鄰導(dǎo)線間的電耦合損耗。這是因為低k介質(zhì)存儲電荷較少,且充電時間更短,從而提升了金屬導(dǎo)線的傳導(dǎo)效率。特別是在現(xiàn)代晶體管中,金屬線間距極小的納米器件中,低k(low-k)材料作為層間介質(zhì)(ILD)顯得尤為關(guān)鍵。

傳統(tǒng)的二氧化硅絕緣體介電常數(shù)在3.9至4.3之間。而新型絕緣體則擁有更低的介電常數(shù),它們通過減少互連電容并防止高性能邏輯電路中金屬線之間的串擾,顯著提升了芯片的運行速度。通常,我們將k值低于3.9的材料定義為低k材料。采用低k材料替代傳統(tǒng)的二氧化硅,已成為集成電路工藝發(fā)展的必然趨勢。

對低k材料的性能要求涵蓋多個方面:

①電學(xué)性能:要求具有低介電常數(shù)、低介電損耗、低漏電流以及高可靠性。

②機械性能:需具備低應(yīng)力、良好的黏附性、低收縮性、優(yōu)異的硬度以及抗開裂能力。

③ 工藝性能:應(yīng)易于圖形制作,具備良好的間隙填充能力、低針孔密度、少顆粒污染以及易于平坦化。

④ 熱學(xué)性能:要求具有高導(dǎo)熱性、良好的熱穩(wěn)定性以及低的熱擴散系數(shù)。

⑤ 化學(xué)性能:需具備低雜質(zhì)含量、低濕氣吸收性、易于干法刻蝕、耐酸堿腐蝕、無侵蝕性以及可接受的存儲壽命。

⑥ 金屬化搭配性能:要求具有低的接觸電阻、低應(yīng)力、低電子遷移率、表面光滑以及與金屬材料的良好兼容性。

在特大規(guī)模集成電路(ULSI)互連中,曾考慮的低k值ILD材料包括氟硅玻璃(FSG,k值為3.4至4.1)、納米多孔硅(k值為1.3至2.5)、氫硅倍半環(huán)氧乙烷(HSO,k值為2.9)、非晶氟化碳(a-C:F,k值為2.8)以及聚Z醚(PAE,k值為2.6至2.8)等。其中,F(xiàn)SG作為典型代表,被廣泛應(yīng)用于深亞微米CMOS集成電路互連線間的介質(zhì)隔離。

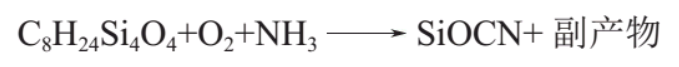

業(yè)界廣泛采用的黑金剛石(black diamond,SiCON)材料,其k值范圍在2.7至3.0之間,能夠滿足45nm節(jié)點的技術(shù)要求。八甲基環(huán)四硅氧烷(OMCTS)是沉積SiCON的前驅(qū)體,其分子式為CH3SiO,常溫下呈液態(tài),沸點約為175℃。通過載氣He將OMCTS輸入反應(yīng)腔中,在等離子體作用下發(fā)生化學(xué)反應(yīng),生成SiCON。該反應(yīng)過程可簡要表示為:

超低k材料

隨著集成電路特征尺寸的持續(xù)縮減,為了更有效地降低金屬間的寄生電容C并減少RC延遲,超低k材料(ultralow-k, ULK)的研發(fā)成為了業(yè)界關(guān)注的熱點。然而,超低k材料的研發(fā)工作給化學(xué)家、物理學(xué)家、材料科學(xué)家以及集成電路工程師們帶來了前所未有的挑戰(zhàn)。因為當材料的k值降低時,其力學(xué)性能和熱穩(wěn)定性往往會受到影響。在此背景下,多孔超低k介質(zhì)成為了主流的研究方向。

多孔介質(zhì)是一種內(nèi)部含有空氣間隙的介質(zhì)材料,其沉積方法主要包括旋涂技術(shù)和化學(xué)氣相沉積技術(shù)。通常,我們將介電常數(shù)小于或等于2.5的材料定義為超低k材料。目前,業(yè)界廣泛采用的多孔SiCOH超低k材料是通過等離子體增強化學(xué)氣相沉積(PECVD)技術(shù)制備的,由硅、碳、氧、氫等元素組成的摻碳非晶玻璃材料。在特定的等離子體條件下,科研實驗室已成功制備出平均孔徑小于2.5納米、孔隙率高達30%、k值低至1.95的超低k納米多孔介質(zhì)薄膜。

除了具有極低的介電常數(shù)外,SiCOH薄膜還展現(xiàn)出了卓越的電學(xué)性能,其漏電流極低且耐壓性能優(yōu)異。此外,SiCOH薄膜在力學(xué)性能方面也表現(xiàn)出色,具有可接受的硬度和彈性模量,并具有良好的防開裂性能。更重要的是,SiCOH薄膜的熱膨脹系數(shù)較低,且與銅的熱膨脹系數(shù)相近,這有助于實現(xiàn)與銅的良好集成。

目前,產(chǎn)業(yè)界量產(chǎn)的SiCOH薄膜其k值大約在2.47左右。其制備工藝流程大致如下:首先,利用二甲基乙氧基硅烷(DEMS)和氧化環(huán)己烯(CHO)在等離子體作用下沉積一層有機硅玻璃薄膜;隨后,通過紫外光輻照處理,排除有機氣體;最后,在晶圓表面形成多孔的SiCOH介質(zhì)薄膜。

高k材料

在探索特殊k值材料的征程中,另一個極具挑戰(zhàn)性的方向,便是研發(fā)高k材料,以此來取代MOS結(jié)構(gòu)中的柵氧材料——二氧化硅 。

在集成電路技術(shù)持續(xù)演進的歷程中,工藝層面的每一次革新都蘊含著深刻的意義與挑戰(zhàn)。隨著時代的發(fā)展,對于集成電路性能的要求愈發(fā)嚴苛,為了實現(xiàn)更高的集成度,在有限的芯片空間內(nèi)容納更多的晶體管,同時達成降低器件功耗以及提升整體性能的目標,一系列關(guān)鍵參數(shù)的調(diào)整成為必然趨勢。其中,集成電路的特征尺寸不斷按照一定比例縮小,工作電壓也隨之持續(xù)降低。在這一復(fù)雜的變革過程中,抑制短溝道效應(yīng)成為了一項至關(guān)重要的任務(wù)。為了有效達成這一目標,除了逐步增加溝道摻雜濃度,降低源漏的結(jié)深之外,柵氧厚度的不斷降低也成為了關(guān)鍵舉措。這是因為柵氧厚度的減小,能夠在微觀層面上提高柵極電容,進而增強柵極對溝道的精準控制能力,就如同為電路的運行提供了更為精細的調(diào)控閥門。

當柵氧化硅層的厚度大于4nm時,它在集成電路的運行環(huán)境中堪稱理想的絕緣體。尤其是與多晶硅柵搭配使用時,二者相互協(xié)作,能夠保障電路的穩(wěn)定運行,為早期集成電路的發(fā)展奠定了堅實的基礎(chǔ)。然而,隨著技術(shù)的不斷進步,當柵氧厚度持續(xù)降低,一旦小于3nm,情況便發(fā)生了顯著的變化。此時,在微觀世界中,量子隧穿效應(yīng)開始在柵極與襯底間嶄露頭角。具體來說,襯底硅中的電子會以一種奇妙的量子形式,穿越原本被視為阻隔的柵氧,進入到柵極之中,這一過程直接導(dǎo)致了柵極漏電流的形成。更為棘手的是,這個漏電流會隨著柵氧厚度的減小呈現(xiàn)出指數(shù)級增長的態(tài)勢。經(jīng)研究發(fā)現(xiàn),柵氧每減小0.2nm,隧穿電流就會增大10倍。柵極漏電流的大幅增加,不僅會造成集成電路功耗的顯著上升,浪費寶貴的能源資源,還會引發(fā)器件發(fā)熱的問題,進而對器件的可靠性產(chǎn)生嚴重影響,如同在精密的電路系統(tǒng)中埋下了一顆不穩(wěn)定的“炸彈”。

當晶體管內(nèi)部的特征尺寸邁入0.18um節(jié)點時,柵的厚度已經(jīng)小于3nm,這一關(guān)鍵參數(shù)的變化促使集成電路制造企業(yè)不得不尋求新的解決方案。在這一背景下,氮氧化硅(SiON)開始進入人們的視野,并逐漸被采用來代替純SiO?作為柵介質(zhì)層。這種替代方法巧妙地利用了SiO?作為主要柵介質(zhì)的基礎(chǔ)優(yōu)勢,通過在SiO?膜中精確摻入適量的氮,使其轉(zhuǎn)變?yōu)榻Y(jié)構(gòu)更為致密的SiON,從而成功提高了柵介質(zhì)的介電常數(shù)。從數(shù)據(jù)對比來看,傳統(tǒng)柵介質(zhì)SiO?的k值為3.9,而純SiN的k值則可達到7。基于這一特性,通過精準地改變摻雜氮的比例,就能夠?qū)崿F(xiàn)對SiON柵介質(zhì)介電常數(shù)的有效調(diào)控。同時,該方法仍然將SiO?作為柵介質(zhì)的主體,這使得它與前期的集成電路技術(shù)之間保持了良好的連續(xù)性和兼容性。在實際應(yīng)用中,這種兼容性能夠有效降低技術(shù)升級的成本和風險,使得新工藝能夠較為順利地融入到已有的生產(chǎn)體系中。因此,在這一特定的技術(shù)發(fā)展階段,SiON受到了廣泛的歡迎和應(yīng)用。其受歡迎的原因主要體現(xiàn)在以下幾個關(guān)鍵方面:首先,SiON具有較高的k值,這一特性使得在相同等效柵電容的情況下,允許有更厚的物理氧化層存在。更厚的物理氧化層能夠在一定程度上增強電路的穩(wěn)定性和可靠性,為電路的正常運行提供更為堅實的保障;其次,SiON具備較高的電子絕緣特性,在相同厚度的情況下,它的柵極漏電流大大降低。這對于降低集成電路的功耗、提高能源利用效率具有重要意義;最后,SiON中氮原子的摻入還能有效地抑制PMOS中多晶硅柵極摻雜的硼離子在柵介質(zhì)中的擴散。硼離子的擴散問題如果得不到有效控制,將會穿過介質(zhì)層到達襯底,進而影響器件的閾值電壓,而SiON的這一特性成功地避免了這一潛在風險。

隨著技術(shù)的不斷推進,特征尺寸進一步縮小到90nm及以下,此時柵氧的厚度也減小到2nm左右。在這一更為精細的尺度下,柵極漏電流和硼離子擴散的問題變得愈發(fā)嚴重,如同技術(shù)發(fā)展道路上的兩座險峻高山,阻礙著集成電路性能的進一步提升。為了克服這些難題,就要求SiON中氮的含量不斷提高。而要實現(xiàn)這一目標,就需要采用更先進的等離子氮化工藝來沉積SiON材料。這種先進工藝不僅能夠提高柵氧中氮的含量,還能夠?qū)Φ姆植歼M行精確控制,使氮主要分布在柵介質(zhì)的上表面,遠離SiO?和溝道界面。這樣的分布方式有助于改善SiO?和Si襯底的界面特性,就像在兩個關(guān)鍵部件之間搭建了一座穩(wěn)固且高效的橋梁,保障了電子在其中的順暢傳輸。

當特征尺寸進入到45nm節(jié)點以后,柵的厚度已經(jīng)小于2nm,此時由SiON和多晶硅柵組成的搭檔在應(yīng)對極高的柵極漏電流、急劇增加的功耗以及柵介質(zhì)層完整性和可靠性問題時,已經(jīng)顯得力不從心。在這種技術(shù)困境下,2007年,Intel公司宣布在45nm節(jié)點采用全新的高k柵介質(zhì)氧化鉿(HfO?)來替代傳統(tǒng)的SiO?,同時利用金屬柵代替多晶硅柵,這一創(chuàng)新性的工藝被稱為HKMG(High - k,Metal Gate)工藝。這一工藝的出現(xiàn),如同在黑暗中點亮了一盞明燈,為集成電路技術(shù)的發(fā)展開辟了新的道路。

實際上,在高k材料領(lǐng)域,研究人員長期以來一直在進行深入的基礎(chǔ)研究。在這一漫長而艱辛的探索過程中,他們發(fā)現(xiàn)了眾多具有高k值的材料,如SiN、Al?O?、Ta?O?、TiO?、TaO、HfO?等。然而,這些材料在實際應(yīng)用中總是存在各種各樣的局限性。它們往往只能滿足某一方面的特定要求,例如在介電常數(shù)、絕緣性能或者熱穩(wěn)定性等方面表現(xiàn)出色,但在其他關(guān)鍵性能指標上卻存在不足。或者,這些材料在與其他工藝的兼容性方面存在嚴重問題,無法順利地融入到現(xiàn)有的集成電路制造體系中。正是由于這些原因,盡管這些材料在理論研究中展現(xiàn)出了一定的潛力,但在實際應(yīng)用中卻面臨著重重困難。直到工藝發(fā)展到特定階段,傳統(tǒng)的以氧化硅為主的介質(zhì)材料在面對日益嚴苛的技術(shù)要求時,已經(jīng)無法滿足集成電路進一步發(fā)展的需求,人們才不得不將目光投向那些曾經(jīng)被視為存在諸多問題的高k材料。

HfO?作為一種備受關(guān)注的高k材料,其介電常數(shù)可達25左右,這一數(shù)值相較于傳統(tǒng)的柵介質(zhì)材料具有明顯的優(yōu)勢。然而,它也并非完美無缺,其結(jié)晶溫度較低,低于600℃。這一特性在實際應(yīng)用中帶來了一個嚴重的問題,即后續(xù)的高溫工藝會使其結(jié)晶化,一旦發(fā)生結(jié)晶化,柵極漏電流就會急劇增加,從而對集成電路的性能產(chǎn)生負面影響。幸運的是,研究人員通過不斷的實驗和探索,發(fā)現(xiàn)可以通過向HfO?中摻入Si、N的方法來提高其結(jié)晶溫度。經(jīng)過這種摻雜處理后,HfO?的結(jié)晶溫度能夠提高到1000℃,這在很大程度上解決了其在高溫工藝中的穩(wěn)定性問題。但令人遺憾的是,摻雜也帶來了另一個問題,即HfO?摻雜后得到的HfSiON介電常數(shù)會降低。雖然HfSiON的介電常數(shù)會隨著N含量的增加而增大,但即便在N含量達到最大值時,其介電常數(shù)也只能達到16,這與未摻雜的HfO?相比,存在一定的差距。

為了使HfO?和HfSiON能夠更好地與當前的硅工藝相兼容,研究人員通過改變工藝流程和改用金屬柵極等一系列創(chuàng)新舉措,成功地解決了這一難題。目前,HfO?和HfSiON已經(jīng)憑借其出色的性能,成為了最合適的柵極高k介質(zhì)材料。它們之所以能夠脫穎而出,主要基于以下兩點關(guān)鍵優(yōu)勢:其一,HfO?和HfSiON具有很高的電子絕緣特性,這一特性使得它們能夠有效地阻止電子的泄漏,保障了集成電路的正常運行;其二,HfO?和HfSiON的k值范圍是15 - 25,比SiON的k值4 - 7要大得多。在相同等效氧化層厚度下,HfO?和HfSiON的厚度可以是SiON的3 - 6倍多。這一顯著的差異將顯著減小量子隧穿效應(yīng),從而有效改善柵極漏電流及其引起的功耗問題,為集成電路的高性能運行提供了有力的支持。

在金屬柵極(metal gate)制備時,根據(jù)不同的MOS類型,可以采用不同的金屬材料。對于NMOS而言,其金屬柵極材料可選用Ta - AlN,這種材料能夠在NMOS的工作環(huán)境中發(fā)揮出良好的性能;而對于PMOS,其金屬柵極材料則可選用TaN,TaN在PMOS中能夠有效地實現(xiàn)其功能,滿足電路對PMOS的性能要求。

高k介電材料的應(yīng)用領(lǐng)域并不僅限于取代超薄柵氧化硅,它在半導(dǎo)體存儲器領(lǐng)域也有著重要的應(yīng)用價值。以動態(tài)隨機存儲器(DRAM)為例,高k介電材料作為其中電容的介質(zhì)材料,承擔著存儲信息的關(guān)鍵任務(wù)。對于DRAM器件而言,要確保存儲信息的電荷在刷新時能夠正常恢復(fù),就必須要有一定的電容容量作為保障。為了提高DRAM的容量,不斷減小器件的特征尺寸成為了必然選擇。然而,特征尺寸的減小意味著電容面積也會隨之減小。在電介質(zhì)厚度不變的情況下,根據(jù)電容公式,為了保持同樣的電容大小,就必須提高介質(zhì)的介電常數(shù),以此來抵消面積減小帶來的影響。例如,可以采用基于二氧化鋯的高k材料,其介電常數(shù)在26左右,具有較高的性能優(yōu)勢。在制備這種材料時,可采用原子層沉積(atomic layer deposition,ALD)方法。ALD也被稱為原子層化學(xué)氣相沉積(ALCVD)。原子層沉積是一種將物質(zhì)以單原子膜形式一層一層地鍍在襯底表面的獨特工藝。它與普通CVD雖然有相似之處,但在ALD中,新一層原子膜的化學(xué)反應(yīng)是直接與之前一層相關(guān)聯(lián)的。這種獨特的工藝特點使得每次反應(yīng)只沉積一層原子,從而能夠?qū)崿F(xiàn)對材料生長的精確控制,為制備高質(zhì)量的高k介電材料提供了有力的技術(shù)支持。

-

芯片

+關(guān)注

關(guān)注

459文章

52360瀏覽量

438862 -

介質(zhì)

+關(guān)注

關(guān)注

0文章

142瀏覽量

18822

原文標題:芯片里的介質(zhì)及其性能介紹

文章出處:【微信號:bdtdsj,微信公眾號:中科院半導(dǎo)體所】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

半導(dǎo)體芯片中的互連層次

CI24R1超低成本高性能2.4GHz GFSK無線收發(fā)芯片中文手冊

芯知識|WT588系列語音芯片BUSY引腳功能解析與設(shè)計指南

芯知識|WT3000T8語音合成芯片:功能解析與應(yīng)用指南

玻璃中介層:顛覆傳統(tǒng)封裝,解鎖高性能芯片 “新密碼”

FU6832高性能電機驅(qū)動專用芯片中文手冊

芯片制造的關(guān)鍵一環(huán):介質(zhì)層制備工藝全解析

單片機語音芯片中的SPI Flash探秘及其分類詳解

詳解金屬互連中介質(zhì)層

芯片中介質(zhì)及其性能解析

芯片中介質(zhì)及其性能解析

評論