在芯片這一高度集成化和精密化的電子元件中,介質層扮演著至關重要的角色。它不僅在芯片中提供了必要的電氣隔離,還在多層互連結構中實現(xiàn)了信號的高效傳輸。隨著芯片技術的不斷發(fā)展,介質層材料的選擇、性能以及制備工藝都成為了影響芯片性能的關鍵因素。本文將深入探討芯片里的介質及其性能,為讀者揭示這一領域的奧秘。

一、介質層的基本概念與功能

介質層,顧名思義,是一種不導電的薄膜材料。在芯片制造中,介質層被廣泛應用于電氣隔離、表面保護以及作為刻蝕、擴散等工藝的掩模。具體來說,介質層的功能主要體現(xiàn)在以下幾個方面:

- 電氣隔離:介質層能夠在芯片的不同部分之間形成電氣屏障,有效隔離電路元件,防止電流短路,確保電路元件之間的獨立工作。

- 表面保護:沉積在芯片表面的介質層能夠有效抵御機械損傷、化學腐蝕及環(huán)境侵蝕,從而延長芯片的使用壽命。

- 掩模作用:在芯片制造過程中,介質層還充當刻蝕、擴散等工藝的掩模,確保圖形的精確轉移。

二、介質層的種類與性能

根據(jù)介電常數(shù)的不同,介質層材料可以大致分為低k材料和高k材料兩大類。介電常數(shù),特別是相對介電常數(shù),是衡量材料電介質性質的重要參數(shù),它反映了材料在電場中的電荷存儲能力。

1. 低k材料

低k材料,其介電常數(shù)通常小于4.0。這類材料在芯片制造中主要用于降低寄生電容,進而提升信號傳輸速度和降低功耗。寄生電容是芯片中相鄰導線之間由于電場作用而產(chǎn)生的電容效應,它會增加信號的傳輸延遲和功耗。而低k材料由于具有較低的介電常數(shù),能夠有效減少相鄰導線間的電耦合損耗,提高信號的傳輸效率。

常見的低k材料包括有機硅、氟化硅、聚酰亞胺等。這些材料不僅具有較低的介電常數(shù),還具備良好的加工性能和熱穩(wěn)定性。例如,有機硅的介電常數(shù)通常在2.65左右,而氟化硅的介電常數(shù)則在2.5至3.5之間。聚酰亞胺則以其良好的柔韌性和耐高溫性能在芯片制造中得到了廣泛應用。

除了傳統(tǒng)的低k材料外,隨著芯片技術的不斷發(fā)展,超低k材料(ultralow-k, ULK)的研發(fā)也成為了業(yè)界關注的熱點。超低k材料的介電常數(shù)通常小于或等于2.5,具有更低的寄生電容和更高的信號傳輸速度。然而,超低k材料的研發(fā)工作也面臨著諸多挑戰(zhàn),如力學性能和熱穩(wěn)定性較差等。為了克服這些問題,研究人員正在積極探索多孔介質等新型超低k材料。

2. 高k材料

高k材料,其介電常數(shù)明顯大于4.0,有時甚至接近或超過20。這類材料在芯片制造中主要用于需要高電容密度以及減少泄漏電流的場合。例如,在金屬柵氧化物半導體場效應晶體管(MOSFET)中,傳統(tǒng)的二氧化硅柵介質由于過薄而容易導致門泄漏電流增加。而高k材料則可以在較厚的情況下提供與薄的二氧化硅相當?shù)碾妶鲂瑥亩鴾p少門泄漏電流。

常見的高k材料包括氧化鉿(HfO2)、氧化鈦(TiO2)、氧化鋯(ZrO2)等。這些材料不僅具有較高的介電常數(shù),還具備良好的熱穩(wěn)定性和化學穩(wěn)定性。在芯片制造中,高k材料通常通過原子層沉積(ALD)、化學氣相沉積(CVD)等高精度薄膜沉積技術制備而成。

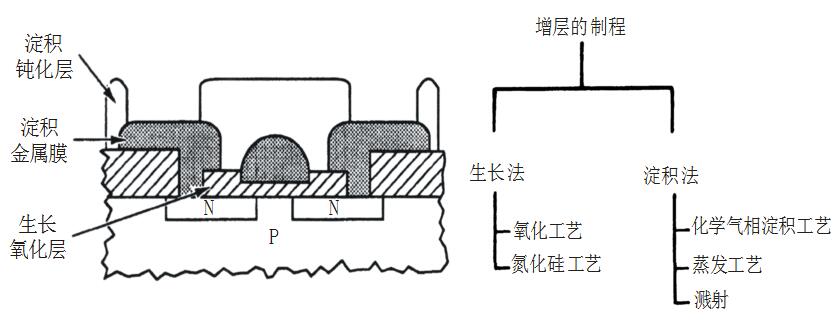

三、介質層的制備工藝

介質層的制備工藝是芯片制造中的關鍵環(huán)節(jié)之一。不同的介質層材料需要采用不同的制備工藝。目前,常用的介質層制備工藝主要包括物理氣相沉積(PVD)、化學氣相沉積(CVD)以及旋涂法(SOD, Spin-On Dielectric)等。

1. 物理氣相沉積(PVD)

PVD是一種通過物理方法將材料從固態(tài)源轉移到基底表面形成薄膜的技術。常見的PVD方法包括蒸發(fā)和濺射等。PVD技術具有沉積速率快、薄膜純度高以及附著力強等特點,特別適用于制備金屬和合金等導電材料的薄膜。然而,在介質層制備方面,PVD技術的應用相對較少。

2. 化學氣相沉積(CVD)

CVD是一種在氣態(tài)環(huán)境中通過化學反應生成并沉積所需材料的技術。CVD技術能夠精確控制薄膜的成分、厚度和均勻性,是制備高純度、高性能介質層材料的主要手段之一。特別是對于復雜結構的介質層,如多層堆疊或摻雜結構,CVD技術展現(xiàn)出其獨特的優(yōu)勢。在芯片制造中,CVD技術被廣泛應用于氧化硅、氮化硅以及高k材料等介質層的制備。

3. 旋涂法(SOD)

SOD是一種經(jīng)濟高效的介質層制備方法。它通過將液態(tài)絕緣材料均勻涂布在晶圓上,然后通過旋轉晶圓形成均勻薄膜,并經(jīng)烘烤固化而成。這種方法具有工藝簡單、成本低廉且適用于大面積沉積等優(yōu)點。然而,SOD方法可能面臨薄膜均勻性和致密度控制方面的挑戰(zhàn)。因此,在芯片制造中,SOD方法通常用于制備一些對薄膜質量要求不是特別高的低k材料。

四、介質層對芯片性能的影響

介質層作為芯片結構的關鍵組成部分,其性能對芯片的整體性能有著重要影響。具體來說,介質層對芯片性能的影響主要體現(xiàn)在以下幾個方面:

信號傳輸速度:介質層的介電常數(shù)直接影響芯片中信號的傳輸速度。低k材料由于具有較低的介電常數(shù),能夠有效減少相鄰導線間的電耦合損耗,提高信號的傳輸效率。而高k材料則可以在較厚的情況下提供與薄的二氧化硅相當?shù)碾妶鲂瑥亩鴾p少門泄漏電流,提高信號的傳輸速度。

功耗:介質層的介電常數(shù)還與芯片的功耗密切相關。低k材料由于具有較低的介電常數(shù),能夠有效降低芯片的總互連電容,從而減少信號的傳輸延遲和功耗。而高k材料則可以在保持電場效應的同時減少門泄漏電流,進一步降低芯片的功耗。

可靠性:介質層的可靠性對芯片的穩(wěn)定運行至關重要。良好的介質層材料應具備優(yōu)異的熱穩(wěn)定性、化學穩(wěn)定性和機械性能,以確保芯片在長時間使用過程中不會出現(xiàn)性能下降或失效等問題。

五、介質層材料的發(fā)展趨勢

隨著芯片技術的不斷發(fā)展,介質層材料也在不斷創(chuàng)新和發(fā)展。未來介質層材料的發(fā)展趨勢將主要體現(xiàn)在以下幾個方面:

多功能化:未來介質層將向多功能化方向發(fā)展,如同時具備低k、高k以及阻擋層等多重功能的復合介質層將成為研究熱點。這種復合介質層可以在保證信號傳輸速度和功耗的同時,提高芯片的可靠性和穩(wěn)定性。

新材料研發(fā):隨著材料科學的不斷進步,越來越多的新型介質層材料將被開發(fā)出來。這些新材料可能具有更低的介電常數(shù)、更高的熱穩(wěn)定性和化學穩(wěn)定性等優(yōu)異性能,為芯片制造提供更多選擇。

綠色制造:環(huán)保和可持續(xù)發(fā)展已成為全球共識。未來介質層材料的研發(fā)和應用將更加注重綠色制造和環(huán)保性能。例如,采用無毒、可回收的介質層材料將成為未來的發(fā)展趨勢之一。

六、結語

芯片里的介質層雖然看似微不足道,但其性能卻對芯片的整體性能有著重要影響。通過深入了解介質層的種類、性能以及制備工藝等方面的知識,我們可以更好地把握芯片技術的發(fā)展方向和應用前景。未來,隨著材料科學和芯片技術的不斷進步,我們有理由相信介質層材料將在芯片制造中發(fā)揮更加重要的作用。同時,我們也期待更多新型介質層材料的涌現(xiàn),為芯片技術的發(fā)展注入新的活力和動力。

-

電子元件

+關注

關注

94文章

1427瀏覽量

57772 -

芯片制造

+關注

關注

10文章

682瀏覽量

29638 -

半導體封裝

+關注

關注

4文章

292瀏覽量

14401

發(fā)布評論請先 登錄

晶圓制備工藝與清洗工藝介紹

【「大話芯片制造」閱讀體驗】+ 芯片制造過程和生產(chǎn)工藝

五環(huán)電阻第一環(huán)識別的方法

無人車最關鍵的一環(huán)是高精地圖

芯片技術中就有了“層”的概念是什么?

淺談GaN芯片的制備工藝(GaN HEMT工藝為例)

SMT技術:手機生產(chǎn)中不可或缺的一環(huán),你了解嗎?

芯片制造的關鍵一環(huán):介質層制備工藝全解析

芯片制造的關鍵一環(huán):介質層制備工藝全解析

評論