作者|北灣南巷

出品|芯片技術與工藝

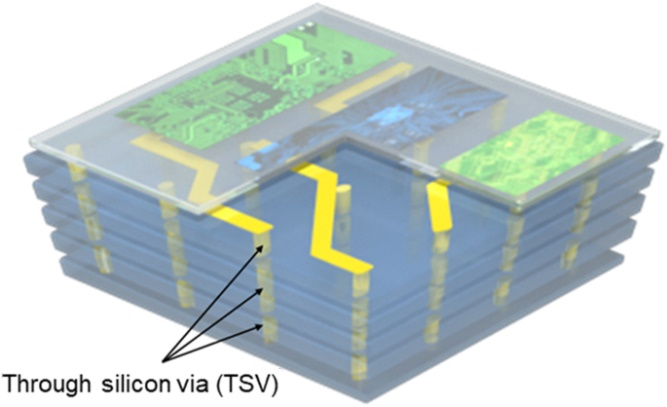

在現代半導體封裝技術不斷邁向高性能、小型化與多功能異構集成的背景下,硅通孔(TSV, Through-Silicon Via)工藝作為實現芯片垂直互連與三維集成(3D IC)的核心技術,正日益成為先進封裝領域的關鍵工藝之一。相較于傳統的封裝互連方式,TSV能夠顯著縮短互連路徑、降低功耗、提升帶寬,并為邏輯芯片與存儲器、MEMS器件、圖像傳感器等多種異構器件提供高密度垂直連接解決方案。

而在TSV工藝流程中,“硅通孔的刻蝕”環節是實現高深寬比通孔結構的關鍵步驟,對刻蝕深度、垂直度、側壁形貌以及工藝一致性要求極高。為滿足這一要求,工業界普遍采用的刻蝕技術便是博世工藝(Bosch Process)——一種基于等離子體深反應離子刻蝕(DRIE)的循環式刻蝕技術。該技術最早由德國博世公司開發,因其具備高縱向各向異性、深寬比大、刻蝕速率高等優勢,已成為深硅刻蝕領域的主流工藝,特別適用于TSV、MEMS和微流控器件等領域的大規模制造。

#01

TSV工藝

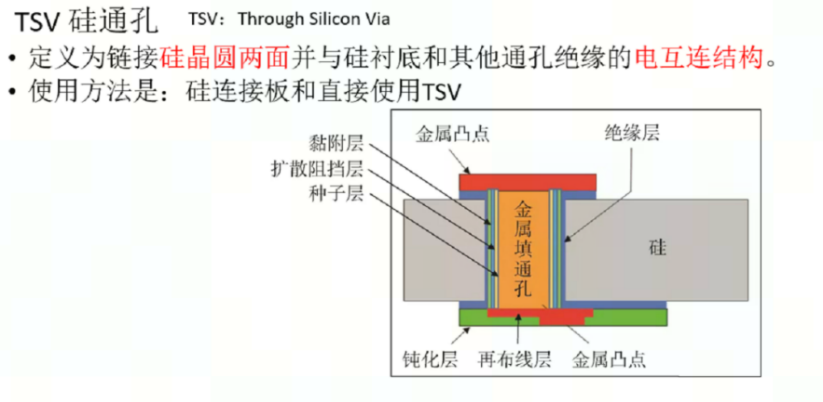

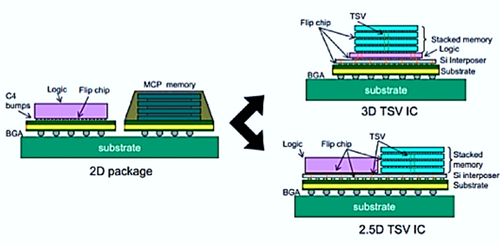

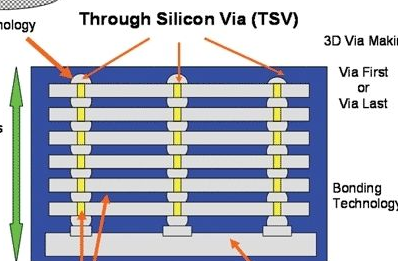

通過硅通孔Through Silicon Via(TSV)技術是在制造三維集成電路(3D IC)中出現的,作為克服傳統二維集成電路(2D IC)限制的解決方案。通過硅通孔(TSV)是一種在IC封裝技術中使用的VIA(垂直互連接入)連接類型,它在硅晶圓或晶圓之間創建垂直的電氣連接。這些垂直連接可以用來互連多個芯片、存儲器、傳感器和其他模塊,以創建更小、更快、更節能的設備。

這項技術被用作替代引線鍵合和倒裝芯片(在2D IC封裝技術中基本使用)以創建2.5D和3D封裝以及3D集成電路。TSV技術的主要優點之一是其能夠提高芯片的數據傳輸速率。在2D IC的傳統互連中,數據信號通過硅襯底橫向傳輸,導致較長的信號傳播延遲。

1.1TSV工藝流程

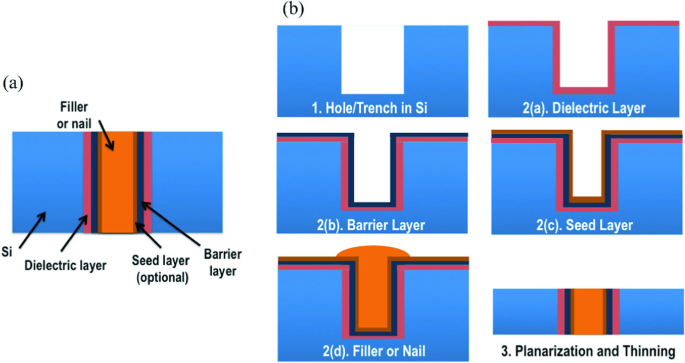

TSV工藝一般包含孔的形成、絕緣層沉積、種子層沉積、金屬填充、回蝕與研磨等步驟,典型工藝流程如下:

TSV孔形成(Etching)

使用深反應離子刻蝕(DRIE,Deep Reactive Ion Etching),通常采用博世工藝(Bosch process),在硅片中刻蝕出高深寬比(高Aspect Ratio)的通孔。

通孔尺寸從幾微米到幾十微米,深度可達幾十到幾百微米。

絕緣層沉積(Liner Deposition)

為避免金屬與硅之間的電化學反應,需要在孔壁沉積絕緣材料,常用材料有SiO?、Si?N?等,采用LPCVD、PECVD等方式沉積。

堵孔種子層(Barrier & Seed Layer)

在絕緣層表面沉積金屬阻擋層(如Ti/TiN)防止金屬擴散。

再沉積金屬種子層(如銅Cu),為后續的電鍍提供基礎層。

金屬填充(Via Filling)

采用銅電鍍(Cu Electroplating)或化學氣相沉積(CVD)等方式將TSV孔填滿。

要求金屬填充過程中無空洞、無縫隙,避免電遷移問題。

去除多余金屬與表面處理

通過化學機械拋光(CMP)將表面多余金屬去除,恢復平坦化。

若為“via-middle”或“via-last”工藝,還需進一步封裝與鍵合處理。

使用TSV,數據信號可以通過較薄的硅襯底垂直傳輸,將信號傳播延遲降低幾個數量級。使用TSV,通過較薄的硅晶圓的短垂直連接減少互連長度,有助于減少芯片的整體面積和功耗。這些優點使其非常適合用于數據中心、服務器、圖形處理單元(GPU)、基于人工智能(AI)的處理器的不同高速應用以及許多無線通信設備。

TSV技術的另一個顯著優點是其能夠實現異構集成。異構集成涉及將來自不同技術和制造商的多個芯片組合到單個封裝中,使它們能夠提供更好的功能性和性能。TSV通過為相應的芯片提供可靠的互連技術,使這些特性成為可能。

#02

博世工藝

1993年,Robert Bosch提出了一種ICP(電感耦合等離子體)刻蝕工藝技術,被稱作“Bosch 工藝”。

2.1 Bosch工藝介紹

Bosch工藝,也稱為交替側壁鈍化深層硅蝕刻工藝,是一種用于制造高深寬比微結構的先進技術,廣泛應用于微機電系統(MEMS)和深硅刻蝕領域。Bosch工藝的影響可以從多個方面進行考慮:

1.高深寬比微結構的制造:Bosch工藝能夠制造具有高深寬比的微結構,這對于許多MEMS器件至關重要。這種能力擴展了MEMS設計的可能性,使得可以制造更復雜、更精細的器件。

2.各向異性蝕刻:Bosch工藝以其出色的各向異性蝕刻能力而聞名,這意味著它可以精確地垂直蝕刻,而不僅僅是沿著晶圓的表面。這為制造具有精確幾何形狀的微結構提供了可能。

3.蝕刻均勻性和控制性:通過精細調整工藝參數,Bosch工藝可以實現高蝕刻均勻性和控制性,這對于批量生產高質量MEMS器件至關重要。

4.微負載效應:Bosch工藝在處理高深寬比結構時可能會遇到微負載效應,即蝕刻速率隨著蝕刻深度的增加而減慢。這需要通過優化工藝參數和設計策略來管理。

5.設備成本和復雜性:Bosch工藝需要專門的設備和技術,這可能會增加制造過程的成本和復雜性。

6.環境影響:Bosch工藝使用多種化學品和氣體,這可能對環境造成影響。因此,需要適當的廢物處理和環境保護措施。

7.工藝發展和創新:Bosch工藝的廣泛應用促進了相關工藝技術的發展和創新,為MEMS和半導體行業帶來了新的制造技術和解決方案。

總體而言,Bosch工藝對MEMS和深硅刻蝕領域產生了深遠的影響,為制造先進微結構提供了關鍵的技術支持。然而,它也帶來了挑戰,需要持續的技術創新和優化來克服。

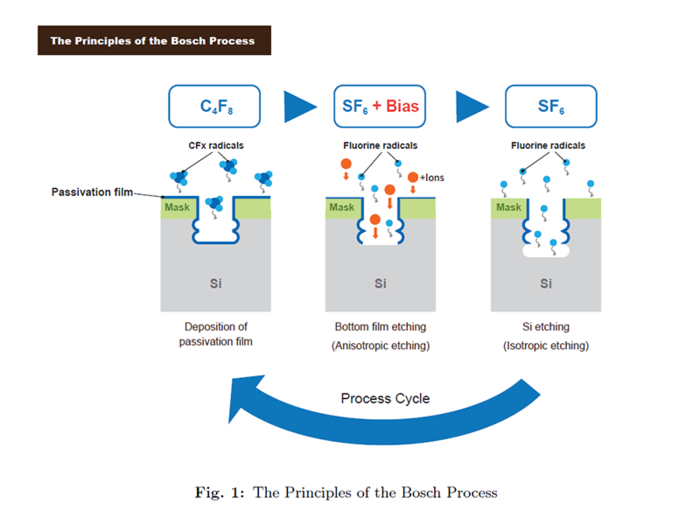

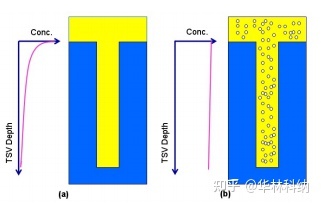

2.2 工藝原理

博世工藝的基本循環包括兩個階段:

刻蝕步驟(Etching Step)

通常使用SF?等氣體,在等離子體中產生氟離子對硅進行各向異性刻蝕。

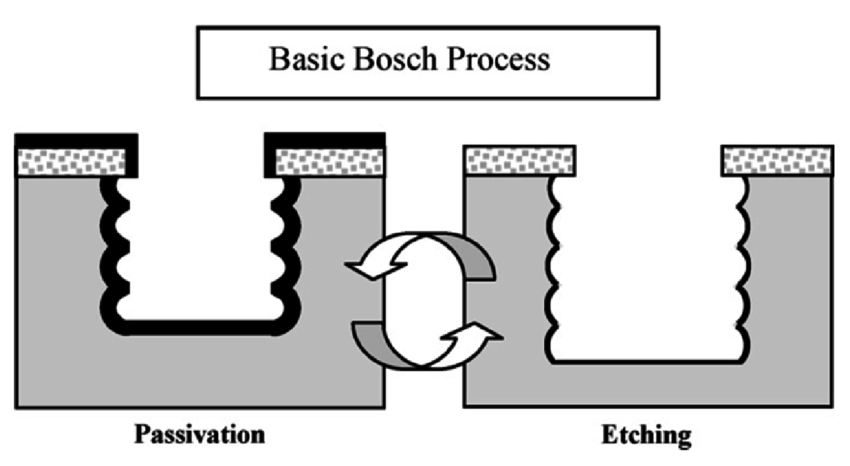

鈍化步驟(Passivation Step)

通常采用C?F?等氣體,在側壁形成聚合物鈍化層,防止橫向刻蝕,保持垂直側壁。

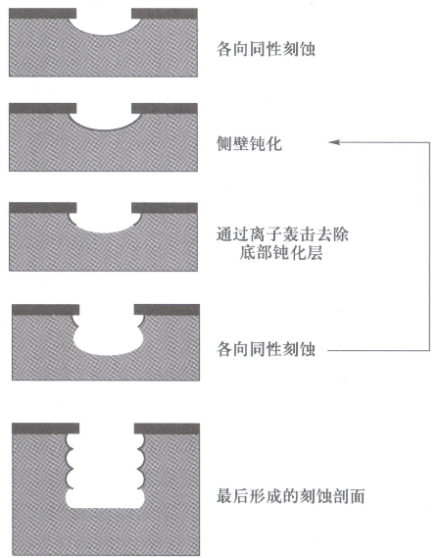

這種工藝首先采用氟基活性基團進行硅的刻蝕,然后進行側壁鈍化,刻蝕和保護兩步工藝交替進行。如下圖說明了其工藝過程。它是通過交替轉換刻蝕氣體與鈍化氣體實現刻蝕與邊壁鈍化。其中刻蝕氣體為SF6,鈍化氣體為C4F8。C4F8在等離子體中能夠形成氟化碳類高分子聚合物。它沉積在硅表面能夠阻止氟離子與硅的反應。刻蝕與鈍化每5~10s 轉換一個周期。在短時間的各向同性刻蝕之后即將剛剛刻蝕過的硅表面鈍化。在深度方向由于有離子的物理濺射轟擊,鈍化膜可以保留下來,這樣下一個周期的刻蝕就不會發生側向刻蝕。通過這種周期性“刻蝕-鈍化-刻蝕”,刻蝕只沿著深度方向進行。

工藝循環方式:

1.刻蝕→ 硅被向下蝕刻;

2.鈍化→ 形成側壁保護層;

3.重復交替多次實現“階梯狀”深刻蝕。

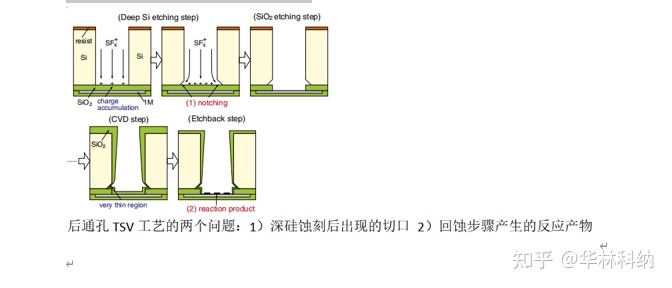

Bosch工藝并不是簡單地重復這三個步驟就能輕易實現的。實際上,這個過程是困難的,存在一些特定于Bosch工藝的問題。因為Bosch工藝的第三步(硅蝕刻過程)是與氟自由基的化學反應,蝕刻速率高度依賴于暴露硅的開口面積。這通常被稱為負載效應。此外,隨著深寬比的增加,氟自由基被輸運到溝槽或孔底部的概率降低。這導致與圖案相關的蝕刻效應,通常稱為微負載,這會不利地影響深度均勻性。微負載是由于晶圓局部高密度區域反應物的耗盡而發生的。此外,特定于DRIE的問題包括在蝕刻SOI(絕緣體上硅)晶圓時的倒角和非均勻等離子體分布引起的傾斜。這些問題通過調整系統硬件、工藝參數和器件結構來解決。

#03

TSV和Bosch工藝的關系

TSV(Through-Silicon Via)中的第一關鍵步驟即為“硅通孔的形成”,其核心工藝是對硅基材料進行高深寬比的垂直刻蝕,而這正是博世工藝的核心能力。

因此,博世工藝在TSV制造中扮演的是“核心刻蝕技術提供者”的角色,可視為TSV工藝鏈中的基礎支撐技術之一。

項目 | TSV工藝 | 博世工藝 |

工藝屬性 | 互連技術 | 刻蝕技術(DRIE) |

關鍵環節 | 通孔形成、金屬填充、研磨 | 硅深孔的高縱深比刻蝕 |

技術交集 | TSV中的孔形成步驟依賴于博世工藝 | 博世工藝提供TSV關鍵孔形成能力 |

工藝特點 | 強調互連性能、電氣性能 | 強調刻蝕精度、垂直性、粗糙控制 |

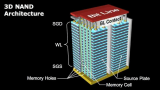

應用 | 3D集成、HBM、圖像傳感器等 | TSV形成、MEMS、冷卻微結構等 |

TSV工藝與博世工藝之間的關系是基礎與應用的關系,博世工藝是實現TSV技術的關鍵制造工具,決定了TSV孔結構的精度、良率與性能。隨著3D集成技術發展,TSV的制程需求不斷提高,也推動了博世工藝不斷進化,兩者之間構成了緊密的協同發展關系。

項目 | TSV工藝優勢 | 博世工藝協同貢獻 |

實現3D垂直互聯 | 利用金屬填充形成高密度通孔互連 | 提供高質量孔結構作為互連基礎 |

集成度提升 | 可在芯片垂直方向疊加多個功能模塊 | 提供深刻蝕能力,確保模塊間通孔貫穿 |

嵌入式系統集成 | TSV適合異構整合(如邏輯+存儲) | 博世工藝兼容多類型晶圓(高阻硅、SOI等) |

小型化與輕薄化 | 有利于降低芯片厚度、封裝尺寸 | 可控制孔深至目標深度,匹配目標封裝厚度 |

總 結:

TSV技術通過在硅晶圓中創建垂直的導電通道,實現了芯片之間的高效電氣連接,是3D IC封裝的關鍵技術之一。這種技術不僅減少了互連長度,降低了信號延遲,還顯著提高了數據傳輸速度和功率效率。TSV技術通過垂直集成多個芯片,打破了傳統的2D封裝限制,使得芯片堆疊成為可能,從而實現了超越摩爾定律的目標。

Bosch工藝在TSV制造中的應用,通過其精確的各向異性蝕刻能力,確保了TSV的高質量和均勻性。這種工藝的精確控制能力對于制造具有精確幾何形狀的TSV至關重要,從而確保了3D IC封裝的整體性能和可靠性。

隨著技術的不斷進步,TSV和Bosch工藝正在推動封裝技術的標準化、新技術的開發、協同設計工具以及多尺度和多物理仿真技術的發展。這些進步對于先進封裝技術的可持續開發至關重要,尤其是在后摩爾時代,它們將幫助行業進一步挖掘縮放的好處,實現更高的封裝密度和更優化的芯片架構。

參考文獻:

1-What is 2D, 2.5D & 3D Packaging of Integrated Chips? - techovedas

2-Challenges and prospects for advanced packaging - ScienceDirect

3-Through-Silicon-Via (TSV) – Revolution in IC Packaging Technology | Blog Posts | Lumenci

4-芯片封裝之2D封裝,2.5D封裝,3D封裝各有什么特點優勢介紹 - 合明科技 (unibright.com.cn)

5-1.2.2 Classification and Designs (tuwien.ac.at)

6-Bosch工藝_百度百科 (baidu.com)

7-What is the Bosch Process (Deep Reactive Ion Etching)?|Tech News|Samco Inc.

8-What is the Bosch Process (Deep Reactive Ion Etching)?|Tech News|Samco Inc.

9-Figure 1 | Scientific Reports

-

TSV

+關注

關注

4文章

121瀏覽量

81861 -

博世

+關注

關注

11文章

478瀏覽量

75294

發布評論請先 登錄

TSV工藝流程與電學特性研究

簡單介紹硅通孔(TSV)封裝工藝

硅通孔(TSV)電鍍

深度解讀TSV 的工藝流程和關鍵技術

博世和西門子哪個好_博世和西門子的關系

什么是TSV封裝?TSV封裝有哪些應用領域?

SAPS兆頻超聲波技術應用于TSV晶片的刻蝕后清洗工藝

TSV關鍵工藝設備及特點

TSV的工藝流程和關鍵技術綜述

什么是硅或TSV通路?使用TSV的應用和優勢

基于兩步刻蝕工藝的錐形TSV制備方法

TSV以及博世工藝介紹

TSV以及博世工藝介紹

評論