在上篇文章中介紹了扇入型晶圓級芯片封裝(Fan-In WLCSP)、扇出型晶圓級芯片封裝(Fan-Out WLCSP)、重新分配層(RDL)封裝、倒片(Flip Chip)封裝,這篇文章著重介紹硅通孔(TSV)封裝工藝。

硅通孔封裝工藝

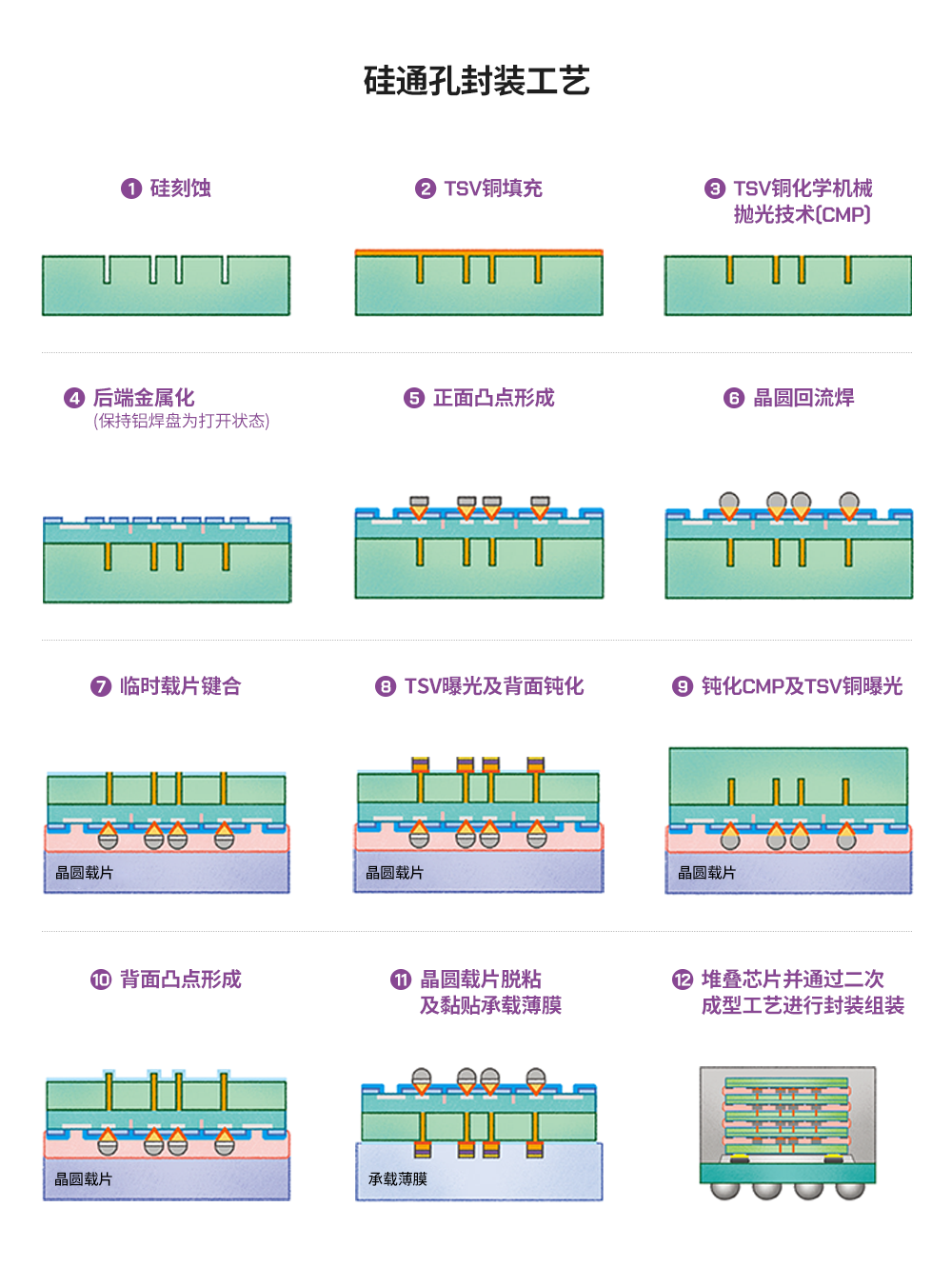

圖6展示了采用中通孔(Via-middle)5方法的硅通孔封裝工藝步驟。首先在晶圓制造過程中形成通孔。隨后在封裝過程中,于晶圓正面形成焊接凸點。之后將晶圓貼附在晶圓載片上并進行背面研磨,在晶圓背面形成凸點后,將晶圓切割成獨立芯片單元,并進行堆疊。

5中通孔(Via Middle):一種硅通孔工藝方法,在互補金屬氧化物半導體形成后及金屬層形成之前開展的工序。

接下來,將簡單概括中通孔的基本工序。首先在前道工序(Front-end of Line)中,在晶圓上制作晶體管,如互補金屬氧化物半導體等。隨后使用硬掩模(Hard Mask)6在硅通孔形成區域繪制電路圖案。之后利用干刻蝕(Dry Etching)工藝去除未覆蓋硬掩膜的區域,形成深槽。再利用化學氣相沉積工藝(Chemical Vapor Deposition)制備絕緣膜,如氧化物等。這層絕緣膜將用于隔絕填入槽中的銅等金屬物質,防止硅片被金屬物質污染。此外絕緣層上還將制備一層金屬薄層作為屏障。

6硬掩膜(Hard Mask):一種由硬質材料而非軟質材料制成的薄膜,用于繪制更為精細的電路圖案。硬掩膜本身對光線并不敏感,所以需使用光刻膠才能進一步繪制電路圖案,以最終實施刻蝕工藝。

此金屬薄層將被用于電鍍銅層。電鍍完成后,采用化學機械拋光(Chemical Mechanical Polishing)技術使晶圓表面保持平滑,同時清除其表面銅基材,確保銅基材只留在溝槽中。然后通過后道工序(Back-end of Line)完成晶圓制造。

▲圖6:硅通孔封裝工序(? HANOL出版社)

使用硅通孔技術制造芯片堆疊封裝體時,一般可采用兩種類型的封裝方法。第一種方法是利用3D芯片堆疊技術的基板封裝。第二種方法則需創建KGSD,然后基于KGSD來制作2.5D或3D封裝。下文將詳細介紹如何創建KGSD,以及如何基于KGSD來制作2.5D封裝的過程。作為利用硅通孔技術制作而成的芯片堆疊封裝體,制作KGSD必需經歷額外封裝工藝,如2.5D封裝、3D封裝以及扇出型晶圓級芯片封裝等,高帶寬存儲器(HBM)就是KGSD產品的一個典型例子。由于KGSD需經歷額外封裝工藝,其作為連接引腳的焊接凸點需要比傳統錫球更加精細。因此3D封裝體中芯片堆疊在基板上,而KGSD中的芯片則堆疊于晶圓上方,晶圓也可以視為KGSD的最底層芯片。就HBM而言,位于最底層的芯片被稱為基礎芯片或基礎晶圓,而位于其上方的芯片則被稱為核心芯片。

此方法工序如下:首先,通過倒片工藝在基礎晶圓和核心晶圓的正面制作凸點。在制作2.5D封裝體時,基底晶圓需要排列凸點,使之能夠附著到中介層(Interposer);相反,核心晶圓上的凸點布局則是有助于晶圓正面的芯片堆疊。在晶圓正面形成凸點后,應減薄晶圓,同時也需在晶圓背面形成凸點。然而,正如前文在介紹背面研磨工藝時所述,需注意在減薄過程中導致晶圓彎曲。在傳統封裝工藝中,進行減薄之前,可將晶圓貼附到貼片環架上,以防止晶圓彎曲,但在硅通孔封裝工藝中,由于凸點形成于晶圓背面,所以這種保護方法并不適用。為解決此問題,晶圓承載系統(Wafer Support System)應運而生。利用晶圓承載系統,可借助臨時粘合劑將帶有凸點的晶圓正面貼附于晶圓載片上,同時對晶圓背面進行減薄處理。此時晶圓貼附于晶圓載片上,即使經過減薄也不會發生彎曲。

此外,因晶圓載片與晶圓形式相同,因此也可使用晶圓設備對其進行加工。基于此原理,可在核心晶圓的背面制作凸點,當核心晶圓正面及背面上的凸點均制作完成時,便可對載片進行脫粘。隨后將晶圓貼附于貼片環架中,并參照傳統封裝工藝,對晶圓進行切割。基礎晶圓始終貼附于晶圓載片上,從核心晶圓上切割下來的芯片則堆疊于基礎晶圓之上。芯片堆疊完成后,再對基礎晶圓進行模塑,而后進行晶圓載片脫粘。至此,基礎晶圓就變成了堆疊有核心晶圓的模制晶圓。隨后對晶圓進行研磨,使其厚度達到制作2.5D封裝體所需標準,然后再將其切割成獨立的芯片單元,以制作KGSD。HBM成品包裝后將運送至制作2.5D封裝體的客戶手中。

審核編輯:湯梓紅

-

芯片封裝

+關注

關注

11文章

576瀏覽量

31371 -

封裝工藝

+關注

關注

3文章

64瀏覽量

8140 -

晶圓級封裝

+關注

關注

5文章

40瀏覽量

11650 -

硅通孔

+關注

關注

2文章

26瀏覽量

11983

原文標題:硅通孔(TSV)封裝工藝。

文章出處:【微信號:閃德半導體,微信公眾號:閃德半導體】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

TSV硅通孔填充材料

3D IC集成與硅通孔TSV互連

3D封裝與硅通孔(TSV)工藝技術

詳解TSV(硅通孔技術)封裝技術

簡單介紹硅通孔(TSV)封裝工藝

簡單介紹硅通孔(TSV)封裝工藝

評論