隨著集成電路工藝制程技術(shù)的不斷發(fā)展,為了提高集成電路的集成度,同時提升器件的工作速度和降低它的功耗,MOS器件的特征尺寸不斷縮小,MOS器件面臨一系列的挑戰(zhàn)。例如短溝道效應(yīng)(Short Channel Effect - SCE),熱載流子注入效應(yīng)(Hot Carrier Inject - HCI)和柵氧化層漏電等問題。為了克服這些挑戰(zhàn),半導(dǎo)體業(yè)界不斷開發(fā)出一系列的先進工藝技術(shù),例如多晶硅柵、源漏離子注入自對準、LDD離子注入、polycide、Salicide、SRD、應(yīng)變硅和HKMG技術(shù)。另外,晶體管也從MOSFET演變?yōu)镕D-SOI、Bulk FinFET和SOI FinFET。

1.1鋁柵MOS管

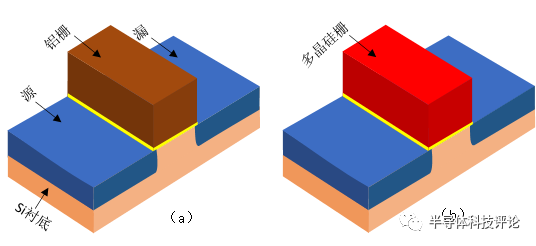

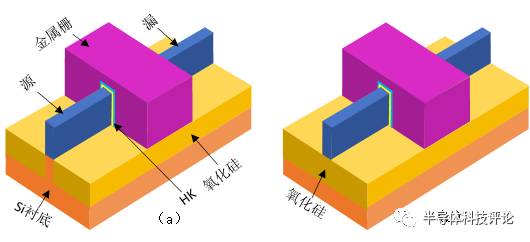

MOS誕生之初,柵極材料采用金屬導(dǎo)體材料鋁,因為鋁具有非常低的電阻,它不會與氧化物發(fā)生反應(yīng),并且它的穩(wěn)定性非常好。柵介質(zhì)材料采用SiO2,因為SiO2可以與硅襯底形成非常理想的Si-SiO2界面。如圖1.13(a)所示,是最初鋁柵的MOS管結(jié)構(gòu)圖。

圖1.13鋁柵和多晶硅柵的MOS管結(jié)構(gòu)圖

1.2多晶硅柵MOS管

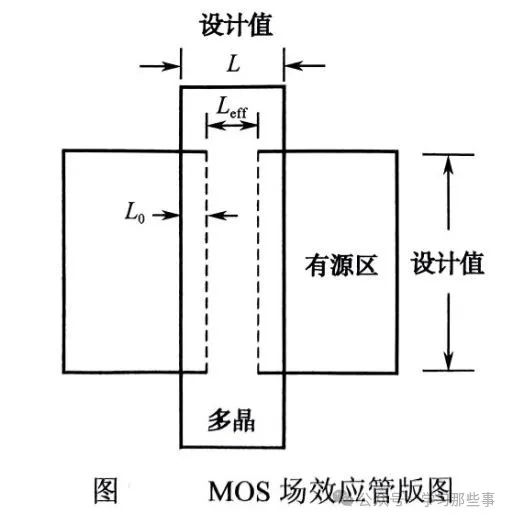

隨著MOS器件的特征尺寸不斷縮小,鋁柵與源漏擴散區(qū)的套刻不準問題變得越來越嚴重,源漏與柵重疊設(shè)計導(dǎo)致,源漏與柵之間的寄生電容越來越嚴重,半導(dǎo)體業(yè)界利用多晶硅柵代替鋁柵。多晶硅柵具有三方面的優(yōu)點:第一個優(yōu)點是不但多晶硅與硅工藝兼容,而且多晶硅可以耐高溫退火,高溫退火是離子注入的要求;第二個優(yōu)點是多晶硅柵是在源漏離子注入之前形成的,源漏離子注入時,多晶硅柵可以作為遮蔽層,所以離子只會注入多晶硅柵兩側(cè),所以源漏擴散區(qū)與多晶硅柵是自對準的;第三個優(yōu)點是可以通過摻雜N型和P型雜質(zhì)來改變其功函數(shù),從而調(diào)節(jié)器件的閾值電壓。因為MOS器件的閾值電壓由襯底材料和柵材料功函數(shù)的差異決定的,多晶硅很好地解決了CMOS技術(shù)中的NMOS和PMOS閾值電壓的調(diào)節(jié)問題。如圖1.13(b)所示,是多晶硅柵的MOS管結(jié)構(gòu)圖。

1.3Polycide技術(shù)

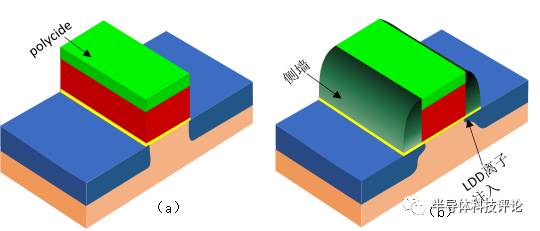

多晶硅柵的缺點是電阻率高,雖然可以通過重摻雜來降低它的電阻率,但是它的電阻率依然很高,厚度3K?的多晶硅的方塊電阻高達36ohm/sq。雖然高電阻率的多晶硅柵對MOS器件的直流特性是沒有影響的,但是它嚴重影響了MOS器件的高頻特性,特別是隨著MOS器件的特征尺寸不斷縮小到亞微米(1um≥L≥0.35um),多晶硅柵電阻率高的問題變得越發(fā)嚴重。為了降低多晶硅柵的電阻,半導(dǎo)體業(yè)界利用多晶硅和金屬硅化物(polycide)的雙層材料代替多晶硅柵,從而降低多晶硅柵的電阻,Polycide的方塊電阻只有3ohm/sq。半導(dǎo)體業(yè)界通用的金屬硅化物材料是WSi2。如圖1.14(a)所示,是多晶硅和金屬硅化物柵的MOS管結(jié)構(gòu)圖。

1.4LDD 離子注入技術(shù)

20世紀60年代,第一代MOS器件的工作電壓是5V,柵極長度是25um,隨著MOS器件的特征尺寸不斷縮小到亞微米,MOS器件的工作電壓并沒有減小,它的工作電壓依然是5V,直到MOS器件柵極長度縮小到0.35um時,MOS器件的工作電壓才從5V降低到3.3V。2008年,MOS器件的柵極長度縮小到45nm,MOS器件的工作電壓縮小到1V。柵極長度從25um縮小到45nm,縮小的倍率是555倍,而MOS器件的工作電壓只從5V縮小到1V,縮小的倍率是5倍,可見MOS器件的工作電壓并不是按比例縮小的。隨著MOS器件的特征尺寸不斷縮小到亞微米級,MOS器件的溝道橫向電場強度是不斷增強的,載流子會在強電場中進行加速,當載流子的能量足夠大時形成熱載流子,并在強場區(qū)發(fā)生碰撞電離現(xiàn)象,碰撞電離會形成新的熱電子和熱空穴,熱載流子會越過Si/SiO2界面的勢壘形成柵電流,熱空穴會流向襯底形成襯底電流,由熱載流子形成的現(xiàn)象稱為熱載流子注入效應(yīng)。隨著MOS器件的特征尺寸不斷縮小到亞微米,熱載流子注入效應(yīng)變得越來越嚴重,為了改善熱載流子注入效應(yīng),半導(dǎo)體業(yè)界通過利用LDD (Lightly Doped Drain - LDD)結(jié)構(gòu)改善漏端耗盡區(qū)的峰值電場來改善熱載流子注入效應(yīng)。如圖1.14(b)所示,是利用LDD結(jié)構(gòu)的MOS管結(jié)構(gòu)圖。

圖1.14金屬硅化物和LDD結(jié)構(gòu)的MOS管結(jié)構(gòu)圖

1.5Salicide技術(shù)

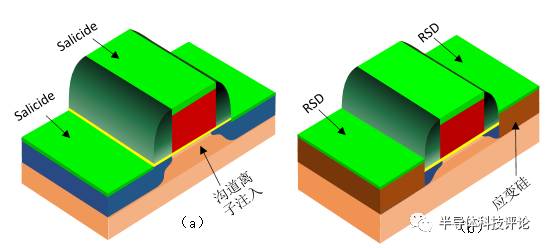

隨著MOS器件的特征尺寸縮小到深亞微米(0.25um≥L),限制MOS器件縮小的主要效應(yīng)是短溝道效應(yīng)。為了改善短溝道效應(yīng),MOS器件的擴散區(qū)結(jié)深也不斷縮小,結(jié)深不斷縮小導(dǎo)致擴散區(qū)的電阻不斷變大,因為擴散區(qū)的縱向橫截面積變小,另外金屬互連的接觸孔的尺寸也減小到0.32um以下,接觸孔變小導(dǎo)致接觸孔與擴散區(qū)的接觸電阻升高了,單個接觸孔的接觸電阻升高到200ohm以上。為了降低擴散區(qū)的電阻和接觸孔的接觸電阻,半導(dǎo)體業(yè)界利用硅和金屬發(fā)生反應(yīng)形成金屬硅化物(silicide)降低擴散區(qū)的電阻和接觸孔的接觸電阻。可利用的金屬材料有Ti、Co和Ni等,金屬材料只會與硅和多晶硅發(fā)生反應(yīng)形成金屬硅化物,而不會與氧化物發(fā)生反應(yīng),所以Silicide也稱為自對準金屬硅化物Salicide(Self Aligned Silicide)。另外擴散區(qū)和多晶硅柵是同時形成Silicide,所以不需要再考慮進行多晶硅柵的polycide。如圖1.15(a)所示,是Salicide的MOS管結(jié)構(gòu)圖。

1.6溝道離子注入和暈環(huán)離子注入技術(shù)

MOS器件的特征尺寸縮小到深亞微米導(dǎo)致的另外一個問題是短溝道效應(yīng)引起的亞閾值漏電流。隨著MOS器件的柵極長度縮小到0.25um,源漏之間的耗盡區(qū)會相互靠近,導(dǎo)致它們之間的勢壘高度降低,形成亞閾值漏電流。雖然MOS器件的柵極長度從0.33um縮小到0.25um時,器件的工作電壓也從3.3V降低到2.5V,但是MOS器件的亞閾值區(qū)的漏電流依然很大。為了降低MOS器件的亞閾值區(qū)的漏電流,需要增加一道溝道離子注入和暈環(huán)(Halo)離子注入增加溝道區(qū)域的離子濃度,從而減小源漏與襯底之間的耗盡區(qū)寬度,改善亞閾值區(qū)的漏電流。如圖1.15(a)所示,進行溝道離子注入的MOS管結(jié)構(gòu)圖。

圖1.15 Salicide和應(yīng)變硅的MOS管結(jié)構(gòu)圖

1.7RSD和應(yīng)變硅技術(shù)

隨著MOS器件的特征尺寸不斷縮小到90nm及以下時,短溝道效應(yīng)中的器件亞閾值電流成為妨礙工藝進一步發(fā)展的主要因素,盡管提高溝道摻雜濃度可以在一定程度上抑制短溝道效應(yīng),然而高摻雜的溝道會增大庫倫散射,使載流子遷移率下降,導(dǎo)致器件的速度降低,所以僅僅依靠縮小MOS器件的幾何尺寸已經(jīng)不能滿足器件性能的提高,需要一些額外的工藝技術(shù)來提高器件的電學(xué)性能,例如應(yīng)變硅技術(shù)。應(yīng)變硅技術(shù)是通過外延生長在源漏區(qū)嵌入應(yīng)變材料使溝道發(fā)生應(yīng)變,從而提高載流子遷移率,最終提高器件的速度。例如NMOS的應(yīng)變材料是SiC,PMOS的應(yīng)變材料是SiGe。另外,隨著源漏的結(jié)深的短減小,源漏擴散區(qū)的厚度已經(jīng)不能滿足形成Salicide的最小厚度要求,必須利用新技術(shù)RSD(Raise Source and Drain)技術(shù)來增加源漏擴散區(qū)的厚度。RSD技術(shù)是通過外延技術(shù)生長在源漏區(qū)嵌入應(yīng)變材料的同時提高源漏擴散區(qū)的厚度。如圖1.15(b)所示,是采用應(yīng)變硅和RSD技術(shù)的MOS管結(jié)構(gòu)圖。

1.8HKMG技術(shù)

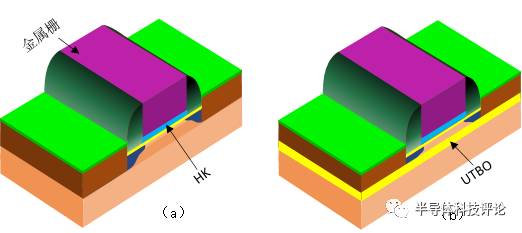

當MOS器件的特征尺寸不斷縮小45nm及以下時,為了改善短溝道效應(yīng),溝道的摻雜濃度不斷提高,為了調(diào)節(jié)閾值電壓Vt,柵氧化層的厚度也不斷減小到1nm。1nm厚度的SiON柵介質(zhì)層已不再是理想的絕緣體,柵極與襯底之間將會出現(xiàn)明顯的量子隧穿效應(yīng),襯底的電子以量子的形式穿過柵介質(zhì)層進入柵,形成柵極漏電流Ig。為了改善柵極漏電的問題,半導(dǎo)體業(yè)界利用新型高K介電常數(shù)(High-k - HK)介質(zhì)材料HfO2來代替?zhèn)鹘y(tǒng)SiON來改善柵極漏電流問題。SiON的介電常數(shù)是3.9,而HfO2的介電常數(shù)是25,在相同的EOT條件下,HfO2的物理厚度是SiON的6倍多,這將顯著減小柵介質(zhì)層的量子隧穿的效應(yīng),從而降低柵極漏電流及其引起的功耗。但是利用HK介質(zhì)材料代替SiON也會引起很多問題,例如導(dǎo)致多晶硅柵耗盡效應(yīng)形成高阻柵,HK介質(zhì)材料與多晶硅的界面會形成界面失配現(xiàn)象降低載流子遷移率,HK介質(zhì)材料還會造成費米能級的釘扎現(xiàn)象。目前半導(dǎo)體業(yè)界利用金屬柵(Metal Gate - MG)取代多晶硅柵電極可以解決Vt漂移、多晶硅柵耗盡效應(yīng)、過高的柵電阻和費米能級的釘扎等現(xiàn)象。利用HK介質(zhì)材料代替SiON和利用金屬柵取代多晶硅柵的技術(shù)稱為HKMG工藝技術(shù)。如圖1.16(a)所示,是采用HKMG技術(shù)的MOS管結(jié)構(gòu)圖。

圖1.16采用HKMG技術(shù)的MOS管結(jié)構(gòu)圖和FD-SOI

1.9FD-SOI晶體管

當MOS器件的特征尺寸不斷縮小22nm及以下時,僅僅提高溝道的摻雜濃度和降低源漏結(jié)深已不能很好的改善短溝道效應(yīng)。加利福尼亞大學(xué)伯克利分校的胡正明教授基于SOI的超薄絕緣層上的平面硅技術(shù)提出UTB-SOI(Ultra Thin Body - UTB),也就是FD-SOI晶體管。研究發(fā)現(xiàn)要使FD-SOI有效抑制短溝道效應(yīng),并能正常工作,絕緣層上硅膜的厚度應(yīng)限制在柵長的四分之一左右。對于25nm柵長的晶體管,F(xiàn)D-SOI的硅膜厚度應(yīng)被控制在5nm左右。FD-SOI晶體管的溝道厚度很小,柵的垂直電場可以有效的控制器件的溝道,從而降低了器件關(guān)閉時的漏電流,抑制短溝道效應(yīng)。如圖1.16(b)所示,是FD-SOI晶體管的剖面圖。

1.10Bulk FinFET和SOI FinFET晶體管

另外,1989年,Hitachi公司的工程師Hisamoto對傳統(tǒng)的平面型晶體管的結(jié)構(gòu)作出改變提出的基于體硅襯底,采用局部氧化絕緣隔離襯底技術(shù)制造出全耗盡的側(cè)向溝道三維晶體管,稱為DELTA(Depleted Lean-Channel Transistor)。胡正明教授依據(jù)Hisamoto的三維晶體管提出采用三維立體型結(jié)構(gòu)的體FinFET和SOI FinFET代替平面結(jié)構(gòu)的MOSFET作為集成電路的晶體管,由于三維立體晶體管結(jié)構(gòu)很像魚的鰭,所以稱為鰭型場效應(yīng)晶體管。如圖1.17所示,是Bulk FinFET和SOI FinFET晶體管的剖面圖。

FinFET晶體管凸起的溝道區(qū)域是一個被三面柵極包裹的鰭狀半導(dǎo)體,沿源-漏方向的鰭與柵重合的區(qū)域的長度為溝道長度。柵極三面包裹溝道的結(jié)構(gòu)增大了柵與溝道的面積,增強了柵對溝道的控制能力,從而降低了漏電流,抑制短溝道效應(yīng),同時也有效的增加了器件溝道的有效寬度,并且增加了器件的跨導(dǎo)。另外為了改善柵極漏電流,F(xiàn)inFET晶體管的柵介質(zhì)也采用HK材料,柵極也采用金屬柵。

圖1.17 Bulk FinFET和SOI FinFET

-

電阻

+關(guān)注

關(guān)注

87文章

5620瀏覽量

174982 -

電極

+關(guān)注

關(guān)注

5文章

842瀏覽量

27840 -

MOS

+關(guān)注

關(guān)注

32文章

1358瀏覽量

96908

發(fā)布評論請先 登錄

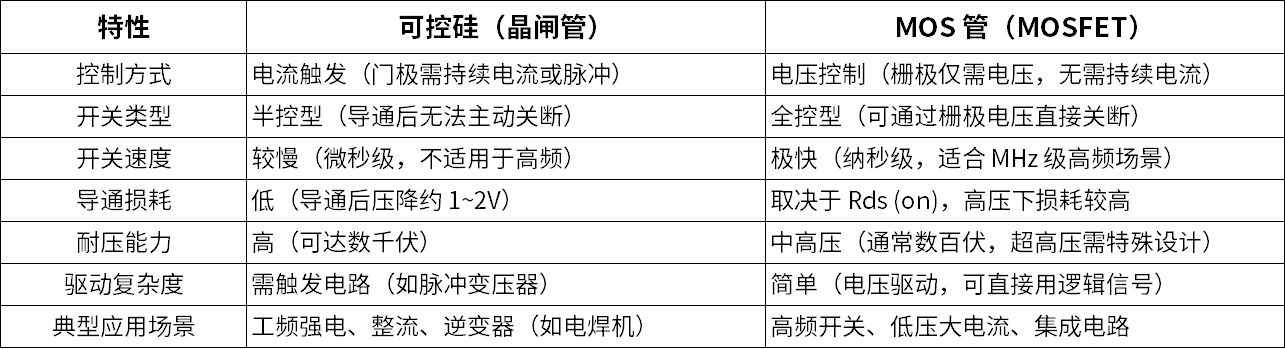

開關(guān)器件應(yīng)用辨析:可控硅能否替代MOS管?

高效迷你化MOS管在快充頭的核心應(yīng)用

CMOS器件面臨的挑戰(zhàn)

電子元器件失效分析與典型案例(全彩版)

混合信號設(shè)計的概念、挑戰(zhàn)與發(fā)展趨勢

工業(yè)電機行業(yè)現(xiàn)狀及未來發(fā)展趨勢分析

GaN、超級SI、SiC這三種MOS器件的用途區(qū)別

高速 MOS 驅(qū)動電路設(shè)計和應(yīng)用指南

MOS高溫挑戰(zhàn)終結(jié)者?仁懋三款MOS器件引爆主機能效革命

MOS管的常見應(yīng)用領(lǐng)域分析

關(guān)于MOS器件的發(fā)展與挑戰(zhàn)分析介紹

關(guān)于MOS器件的發(fā)展與挑戰(zhàn)分析介紹

評論