基于提升框架的小波變換方法,利用FPGA 可編程特性可實現多種小波變換。提升框架(LS :Lifting Scheme) 是由Sweldens 等人在近幾年提出的一種小波變換方法,用它的框架結構能有效地計算DWT。對于較長的濾波器,LS 的操作次數比濾波器組的操作方式減少將近一半,更適合硬件實現。作者根據提升小波變換的框架式結構,利用FPGA 可完全重構的特點構造不同的小波變換核,以滿足不同應用場合的要求。在結構設計中采用由下至上的設計方法,每個提升步驟都由一些可編程的參數來表示,保證了每個步驟均可重構。這些參數包括用于表示數據的位數和每個內部數學模塊的通道深度。在邏輯綜合時按不同小波的要求,改變參數可得到不同的結果。以圖像處理中常用的(5 ,3)濾波器為例說明依靠FPGA 的重組特性實現濾波器的小波變換核方法。實驗結果表明,利用FPGA 設計的提升小波變換核能滿足不同場合和不同運行的要求。

LS 小波變換理論

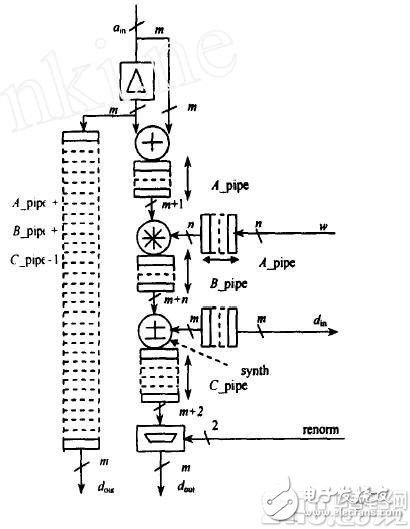

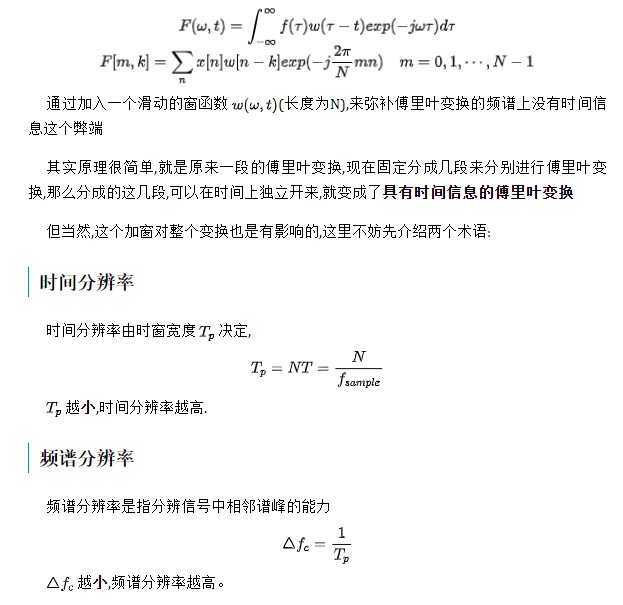

LS 變換過程如圖1 所示,逆變換與正變換相同,只是順序相反。時間離散的濾波器可由它的多項矩陣來表示,多項矩陣由脈沖響應的奇偶采樣序列的Z 變換得到。LS 小波變換的實質是對經典小波濾波器采用Euclidean 算法的多項式進行分解。

圖1 正向LS 變換

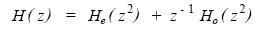

一個時間離散的濾波器H( z ) 用多項式表示如下:

基于FPGA實現多種小波變換

He ( z ) 和Ho ( z ) 各自從

基于FPGA實現多種小波變換

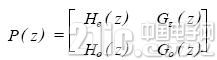

奇偶系數得到。分析濾波器H ( z ) 和G( z ) 分別表示低通和高通,表示成多相矩陣為

基于FPGA實現多種小波變換

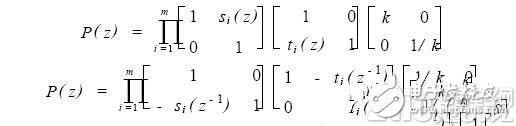

P( z ) 可被模擬為分析濾波器。根據Euclidean算法可將P( z ) 和P( z ) 分解成:

基于FPGA實現多種小波變換

上面的分解不是唯一的,可有幾對{ si ( z ) } 和{ t i ( z ) } 濾波器,但對于計算DWT 所有的選擇是等同的。

FPGA 及提升核的實現

FPGA 及重構特性

FPGA(Field Programmable Gate Array ,現場可編程門陣列) 是超大規模集成電路(VL、SI) 技術和計算機輔助設計(CAD) 技術發展的結果。FPGA 器件集成度高、體積小、具有通過用戶編程實現專門應用的功能。FPGA 一般由3 種可編程電路和1 個用于存放編程數據的SRAM 組成。這3 種可編程電路是:可編程邏輯塊CLB (Configurable Logic Block) 、輸入/輸出模塊IOB ( I/O Block) 和互連資源IR( Interconnect Resource) 。由于基于小波的應用越來越廣泛,所以利用FPGA 的靈活結構實現可重構的提升框架小波變換核具有很高的應用價值和研究價值。設計從基本的數學模塊和邏輯模塊開始,采用由下至上的設計方法,所有的庫模塊用VHDL 語言描述,允許根據設計精度要求選擇每個單元的數據通道大小。為了滿足不同環境的需要,既要求可以改變單獨模塊的通道層深度,又要求考慮與其他設備的相容性。將提升方法與FPGA 的特性結合起來,使不同的提升小波變換在FPGA 上可滿足不同應用場合的需要。

圖2 提升核結構體

提升小波變換核的實現

如圖1 所示,LS 變換是連續的獨立的簡單濾波操作過程,這個過程就是提升步驟。由圖1 可導出優化了的提升核結構體。近幾年,采用JPEG2000 標準進行圖像傳輸成為熱點,很多文獻中均提出了不同的提升小波變換結構體。

但是這些提升結構體大都只考慮可操作性,而忽略了功耗和靈活性。作者提出的提升核結構體(圖2) 采用與以往不同的由下至上的設計方法。主要特點是指定了1 個單獨的流水式的乘法單元和2個加法單元。乘法單元主要用于處理濾波器系數的對稱問題,加法單元用于實現分析或綜合的變換。

值得注意的是所有的通道層都可用所設計的庫模塊來排列,因此為了保證內部IP 核數據流的同步性,必須考慮前后交叉問題。例如,在加法輸出時,已經放置了一個乘法器,允許對提升步驟的結果進行歸一化。采用這種設計方法,能獲得最高的數據精度和最快的運行速度。此外,整數的數學單元更容易進行深層的流水操作,獲得很高的數據吞吐量。圖2 所提出的結構既考慮了可操作性又考慮了應用的靈活性,由于提高了運行速度,所以降低了功耗。

邏輯綜合結果

首先采用VHDL 語言來描述由基本的可重構的數學模塊和邏輯模塊設計的變換核結構體,然后在MAX+PLUSⅡ集成環境下進行功能仿真,實現所需變換核,最后進行FPGA 邏輯綜合。在Altera1 公司的FLEX10K上設計的結構體,經過邏輯綜合得到很滿意的結果,見表1 。表1 的結果直接由邏輯綜合得到,沒有考慮各種客觀因素引起的延時。在設計流程步驟之后的安放運行過程中,可進行更精確的時序分析。另外,為了獲得完整的分析結果,需參考FPGA 廠家提供的指標估計功率消耗,使用時應選擇功耗小的可編程器件,更好地滿足不同使用環境的要求。以(5 ,3) 濾波器為例,計算(5 ,3) 小波需要4個提升核的疊加,所提出的結構體計算正向或逆向(5 ,3)DWT ,對每幀像素1400×1400 采用15位采樣數和12位合成濾波器系數,以全時鐘頻率運行,進行5 層分解、重構,每秒鐘能處理25 幀圖像,功耗為267.6 mW。

結束語

提出的可重構的提升核結構體,采用特殊的即從下至上的設計方法,保證了最大限度地重復利用性和重構特性。仿真結果說明,提升小波變換核的結構體無論在處理能力和功耗方面都取得了很好的結果,尤其在處理速度上,能滿足圖像處理實時性要求。將來的進一步發展是將更多的自由參數加入基本的算術模塊中,保證結構體具有更好的操作性,并且使功率消耗減少,能滿足不同應用場合的需要,對降低設備成本,提高使用效率有實際意義。

-

FPGA

+關注

關注

1643文章

21982瀏覽量

614568 -

濾波器

+關注

關注

162文章

8094瀏覽量

181194 -

小波變換

+關注

關注

2文章

183瀏覽量

30071

發布評論請先 登錄

基于DSP Builder的小波變換設計實現

基于DSP Builder的小波變換設計實現

基于FPGA的快速9/7整形離散小波變換系統

雙運算核提升小波變換的FPGA硬件實現

如何使用FPGA實現多種小波變換

如何使用FPGA實現多種小波變換

評論