歡迎訪問有關(guān)如何使用基本VHDL和Basys 3板構(gòu)建秒表的說明。我們很高興與您分享我們的項(xiàng)目!這是2016年秋季在SLO的Cal Poly開設(shè)的CPE 133課程(數(shù)字設(shè)計(jì))的最終項(xiàng)目。我們構(gòu)建的項(xiàng)目是一個簡單的秒表,用于啟動,重置和暫停時間。它以Basys3板上的三個按鈕作為輸入,并且時間顯示在板的四位數(shù)七段顯示器上。經(jīng)過的時間以 seconds:厘秒格式顯示。它使用開發(fā)板的系統(tǒng)時鐘作為輸入來跟蹤經(jīng)過的時間,并將時間輸出到七段顯示器的四位數(shù)。

步驟1:材料

該項(xiàng)目所需的材料:

從Xilinx安裝了1臺裝有Vivado Design Suite WebPack的計(jì)算機(jī)(首選版本2016.2)

1 Digilent Basys3 Xilinx Artix-7 FPGA板

步驟2:設(shè)置輸入和輸出

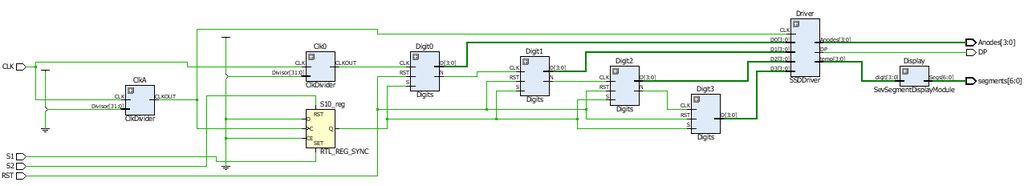

上圖顯示了秒表主模塊的頂級框圖。秒表接受輸入“ CLK”(時鐘),“ S1”(開始按鈕),“ S2”(暫停按鈕)和“ RST”(復(fù)位),并具有4位輸出“陽極”,7位輸出“段”和一位輸出“ DP”(小數(shù)點(diǎn))。當(dāng)輸入“ S1”為高時,秒表開始計(jì)時。當(dāng)“ S2”為低時,秒表暫停時間。當(dāng)“ RST”為高電平時,秒表將停止并重置時間。電路中有四個子模塊:時鐘分頻器,數(shù)字計(jì)數(shù)器,七段顯示驅(qū)動器和七段顯示編碼器。秒表主模塊將所有子模塊鏈接在一起,并鏈接到輸入和輸出。

步驟3:制作時鐘

時鐘分頻器模塊接收一個系統(tǒng)時鐘,并使用一個除數(shù)輸入來創(chuàng)建一個不大于系統(tǒng)時鐘速度的時鐘。秒表使用兩個不同的時鐘模塊,一個創(chuàng)建一個500 Hz的時鐘,另一個創(chuàng)建一個100 Hz的時鐘。時鐘分頻器的原理圖如上圖所示。時鐘分頻器接收一個位輸入“ CLK”,一個32位輸入“除數(shù)”和一個位輸出“ CLKOUT”。 “ CLK”是系統(tǒng)時鐘,“ CLKOUT”是結(jié)果時鐘。該模塊還包括一個“非”門,當(dāng)計(jì)數(shù)達(dá)到除數(shù)的值時,它將切換信號“ CLKTOG”。

步驟4:計(jì)數(shù)到十

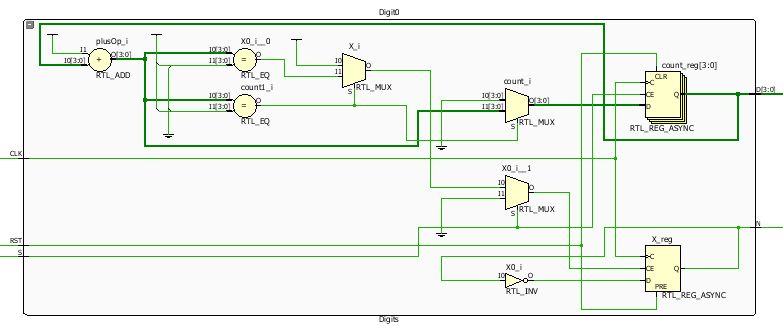

數(shù)字計(jì)數(shù)器對從0到10的每個數(shù)字進(jìn)行計(jì)數(shù),并為下一個數(shù)字創(chuàng)建另一個時鐘,以使該數(shù)字在計(jì)數(shù)達(dá)到10時振蕩。模塊接收3個單位輸入“ S”, “ RST”和“ CLK”并產(chǎn)生一個單位輸出“ N”和一個4位輸出“ D”。輸入“ S”是輸入中的啟用。當(dāng)“ S”為高電平時,時鐘打開;當(dāng)“ S”為低電平時,時鐘關(guān)閉。 “ RST”是復(fù)位輸入,因此當(dāng)“ RST”為高電平時時鐘將復(fù)位。 “ CLK”是數(shù)字計(jì)數(shù)器的時鐘輸入。 “ N”是時鐘輸出,成為下一位數(shù)字的輸入時鐘。輸出“ D”表示計(jì)數(shù)器所在數(shù)字的二進(jìn)制值。

步驟5:顯示數(shù)字

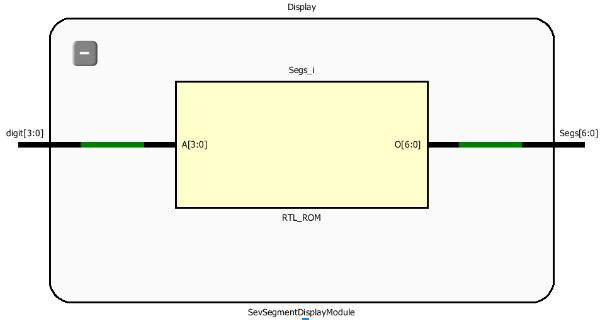

這七個-segment顯示編碼器將對從七段顯示驅(qū)動器模塊接收到的二進(jìn)制數(shù)進(jìn)行編碼,并將其轉(zhuǎn)換為比特流,對于每個顯示段,該比特流將被解釋為“ 1”或“ 0”值。二進(jìn)制數(shù)由模塊作為4位輸入“數(shù)字”接收,并產(chǎn)生7位輸出“段”。該模塊由一個單例處理塊組成,該塊為從0到9的每個可能的輸入值分配一個特定的7位流。七位流中的每個位代表顯示器上數(shù)字的七個部分之一。流中各段的順序?yàn)椤?abcdefg”,其中“ 0”表示為給定數(shù)字點(diǎn)亮的段。

步驟6:如何顯示秒表

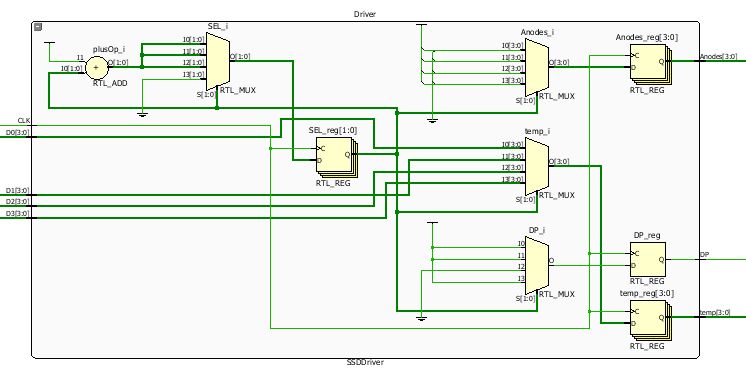

在七段顯示驅(qū)動器模塊中,有四個4位輸入“ D0”,“ D1”,“ D2”和“ D3”,每個輸入代表4位數(shù)字。被顯示。輸入“ CLK”是系統(tǒng)的時鐘輸入。一位輸出“ DP”代表七段顯示器上的小數(shù)點(diǎn)。 4位輸出“ Anodes”確定顯示七段顯示器上的哪個數(shù)字,而4位輸出“ temp”取決于2位控制輸入“ SEL”的狀態(tài)。該模塊使用4個多路復(fù)用器作為控制輸入“ SEL”和三個輸出。 “陽極”,“溫度”和“ DP”。

第7步:將它們整合在一起

一個從中運(yùn)行的‘if’過程塊500Hz時鐘用于創(chuàng)建開始和暫停按鈕。然后,通過聲明每個單獨(dú)的子模塊的組件并使用各種信號,將秒表主模塊中的所有子模塊鏈接在一起。數(shù)字子模塊采用前一個數(shù)字子模塊的時鐘輸出,第一個采用100Hz時鐘。然后,數(shù)字子模塊的“ D”輸出變?yōu)槠叨物@示驅(qū)動器模塊的“ D”輸入。最后,七段顯示驅(qū)動程序模塊的“ temp”輸出變?yōu)槠叨尉幋a器模塊的“ temp”輸入。

步驟8:約束

使用3個按鈕(W19,T17和U18)輸入“ RST”,“ S1”和“ S2”。 W19是重置按鈕,T17是開始按鈕(S1),而U18是暫停按鈕(S2)。還需要使用端口W5限制時鐘輸入的輸入。另外,請記住將此行添加到時鐘約束中:

create_clock -add -name sys_clk_pin -period 10.00 -waveform {0 5} [get_ports {CLK}]

也請鏈接陽極和電路板上的分段,因此秒表顯示在約束文件中所示的七段顯示器上。

步驟9:測試

通過按三個按鈕來確保設(shè)備正常工作:以各種可能的方式推動并按住它們,以便發(fā)現(xiàn)代碼中可能存在的問題。

責(zé)任編輯:wv

-

vhdl

+關(guān)注

關(guān)注

30文章

819瀏覽量

129606 -

秒表

+關(guān)注

關(guān)注

3文章

81瀏覽量

22280 -

basys3

+關(guān)注

關(guān)注

0文章

4瀏覽量

4557

發(fā)布評論請先 登錄

請問如何使用UUU進(jìn)行獨(dú)立內(nèi)核構(gòu)建?

在嘗試更新到6.6.52 scarthgap支持時,面臨yocto構(gòu)建錯誤怎么解決?

為自定義板構(gòu)建具有scarthgap 6.6.52支持的yocto映像時遇到報(bào)錯如何解決?

求助,關(guān)于K3s的GoldVIP yocto構(gòu)建問題求解

淺談Verilog和VHDL的區(qū)別

使用XC3S1500-4FGG456C控制ADS1248,讀不到AD數(shù)據(jù),為什么?

Verilog與VHDL的比較 Verilog HDL編程技巧

Verilog vhdl fpga

使用低成本MSP430 MCU簡化7段LED秒表應(yīng)用說明

如何使用基本VHDL和Basys3板構(gòu)建秒表

如何使用基本VHDL和Basys3板構(gòu)建秒表

評論