PCB的層數(shù)多少取決于電路板的復雜程度,從PCB的加工過程來看,多層PCB是將多個“雙面板PCB”通過疊加、壓合工序制造出來的。但多層PCB的層數(shù)、各層之間的疊加順序及板材選擇是由電路板設計師決定的,這就是所謂的“PCB層疊設計”。

PCB層疊設計需考慮的因素

一款PCB設計的層數(shù)及層疊方案取決于以下幾個因素:

1、硬件成本:PCB層數(shù)的多少與最終的硬件成本直接相關,層數(shù)越多硬件成本就越高,以消費類產(chǎn)品為代表的硬件PCB一般對于層數(shù)有最高限制,例如筆記本電腦產(chǎn)品的主板PCB層數(shù)通常為4~6層,很少超過8層;

2、高密元器件的出線:以BGA封裝器件為代表的高密元器件,此類元器件的出線層數(shù)基本決定了PCB板的布線層層數(shù);

3、信號質(zhì)量控制:對于高速信號比較集中的PCB設計,如果重點關注信號質(zhì)量,那么就要求減少相鄰層布線以降低信號間串擾,這時布線層層數(shù)與參考層層數(shù)(Ground層或Power層)的比例最好是1:1,就會造成PCB設計層數(shù)的增加;反之,如果對于信號質(zhì)量控制不強制要求,則可以使用相鄰布線層方案,從而降低PCB層數(shù);

4、原理圖信號定義:原理圖信號定義會決定PCB布線是否“通順”,糟糕的原理圖信號定義會導致PCB布線不順、布線層數(shù)增加;

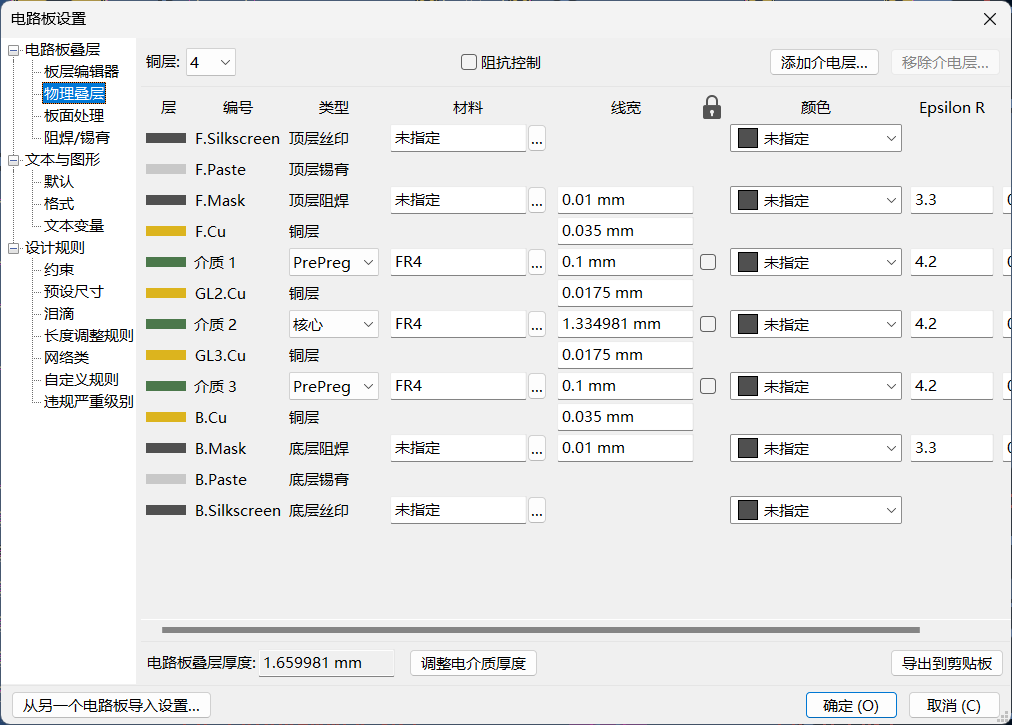

5、PCB廠家加工能力基線:PCB設計者給出的層疊設計方案(疊層方式、疊層厚度等),必須要充分考慮PCB廠家的加工能力基線,如:加工流程、加工設備能力、常用PCB板材型號等。

PCB層疊設計需要在以上所有設計影響因素中尋求優(yōu)先級和平衡點。

PCB層疊設計的一般規(guī)則

1、地層與信號層之間應緊密耦合,意思就是說,地層與電源層之間的距離應盡量小,介質(zhì)厚度應盡量小,以增大電源層與地層之間的電容(如果這里不明白,大家可以想一下平板電容,電容的大小與間距成反比)。

2、兩個信號層之間盡量不要直接相鄰,這樣容易發(fā)生信號的串擾,影響電路的性能。

3、對于多層電路板,例如4層板,6層板,一般要求信號層盡量與一個內(nèi)電層(地層或者電源層)相鄰,這樣可以利用內(nèi)電層的大面積覆銅來起到屏蔽信號層的作用,從而有效的避免了信號層之間的串擾。

4、對于高速信號層,一般要位于兩個內(nèi)電層之間,這樣做的目的是一方面起到對高速信號提供一個有效的屏蔽層,另一方面則將高速信號限制在兩個內(nèi)電層之間,減小對其他信號層的干擾。

5、要考慮層疊結(jié)構(gòu)的對稱性。

6、多個接地的內(nèi)電層可以有效的降低接地阻抗。

推薦的層疊結(jié)構(gòu)

1、把高頻走線布在頂層,以避免高頻走線過程中使用到過孔而引入感應電感。在頂層隔離器和發(fā)送接收電路的數(shù)據(jù)線用高頻走線直接相連。

2、高頻信號線下面放置一個地平面,以控制傳輸連接線的阻抗,也提供了一個非常低電感的通路給返回電流(returncurrent)流過。

3、將電源層置于接地層下面。這兩個參考層構(gòu)成了一個大約為100pF/inch2的附加高頻旁路電容器。

4、在底層布線布置低速控制信號。這些信號線擁有較大的余量來承受過孔引起的阻抗不連續(xù),這樣的話就更有靈活性。

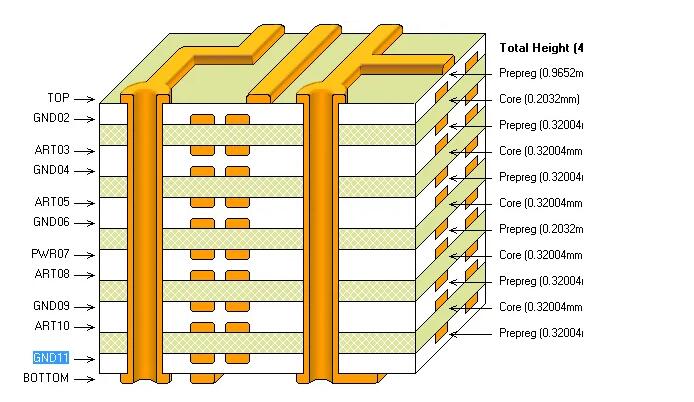

▲四層板疊層設計示例

如果還需要增加供電層(Vcc)或信號層,增加的第二組電源層/地層必須對稱層疊。這樣層疊層壓結(jié)構(gòu)才穩(wěn)定,板子也不會翹曲。不同電壓的電源層和地層之間應該靠近一點,這樣增加高頻旁路電容,從而抑制噪聲。

提醒:這里還有一層的意思就是要使用偶數(shù)層PCB,避免使用奇數(shù)層。因為奇數(shù)層電路板容易彎曲。

-

pcb

+關注

關注

4358文章

23443瀏覽量

407735 -

層疊設計

+關注

關注

0文章

12瀏覽量

7742

發(fā)布評論請先 登錄

PCB層疊結(jié)構(gòu)設計的先決條件

高層數(shù)層疊結(jié)構(gòu)PCB的布線策略

層疊布局 (Stack):Stack組件為容器組件,容器內(nèi)可包含各種子元素

不可忽視!四層PCB打樣設計中的關鍵細節(jié)大盤點!

mark點定位的一般原理與步驟

PCB 設計規(guī)則、層疊結(jié)構(gòu)的導入/導出

12條PCB設計規(guī)則

0.4mm層疊封裝(PoP)封裝的PCB組裝指南,第二部分

0.5mm層疊封裝應用處理器的PCB設計指南,第一部分

0.5mm層疊封裝應用處理器的PCB組裝指南,第II部分

0.4毫米層疊封裝(PoP)的PCB設計指南,第一部分

飛凌 Elfboard硬件分享-高速 PCB 設計需考慮因素

基于熱性能的NIS(V)3071 PCB設計考慮因素

PCB層疊設計需考慮的因素_PCB層疊設計的一般規(guī)則

PCB層疊設計需考慮的因素_PCB層疊設計的一般規(guī)則

評論