單板中的不同電源如何去耦?工程師們往往都是嚴格按照元件Datasheet推薦方法與建議,這些建議往往如下所描述:“The supply tothis pin should be decoupled with 0.1uF and 0.01uF Capacitor to ground as nearas possible”,如下圖所示,而這些建議歸納起來就是2點:

(1) “使用0.1uF或0.01uF的電容”

(2) ”離電源管腳越近越好”

圖 1. 某Datasheet上濾波電容的使用建議

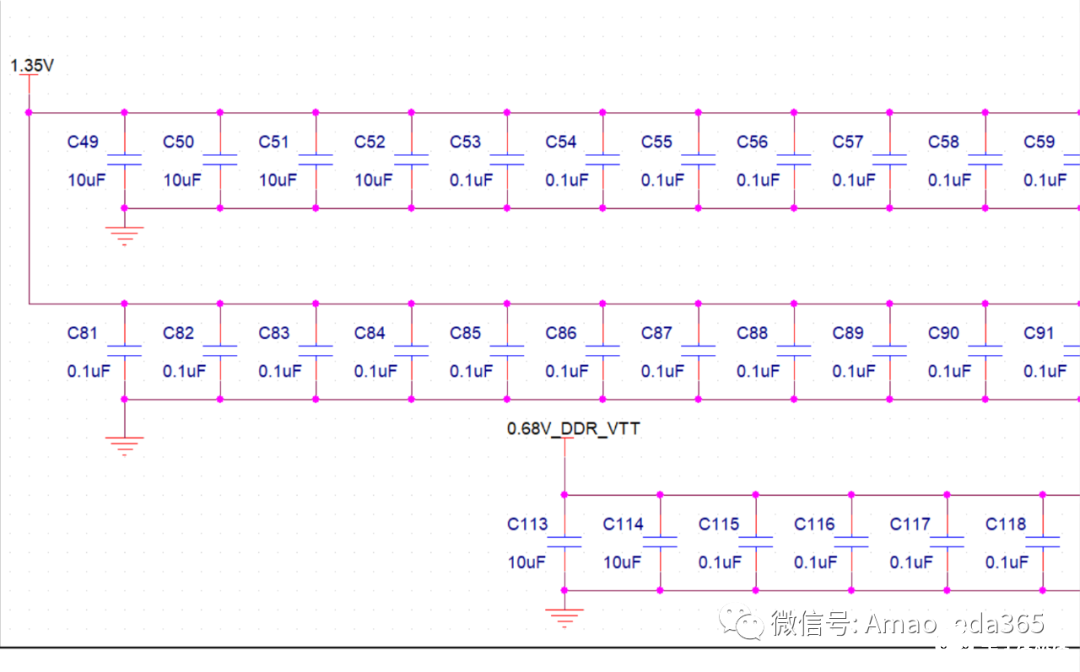

這類建議看起來是萬能的,但是用起來又有點“萬萬不能”,因為單板的應用情景千變萬化,這些建議在具體應用時往往令硬件工程師感覺需要喝上幾杯“蟻力神”才緩得過氣來,實在煩了有時也會存在一點“甩鍋”心里,不再多想而嚴格執行Datasheet上的建議或“過設計”。最后的原理圖往往成了如下的模樣,即閉著眼睛多按幾下Clt+V。

圖 2. 常見的電容組合原理圖

下游PCB布局時發現沒足夠的空間放置這么多電容后,再是一翻“溝通”過后,硬件工程師再對原理圖作部分刪除,這種方法從電容的數量、位置、類型組合等方面對PCB的設計都沒有定量的細節指導。因而出現了本文開始時提到的:“越多越好、越近越好”的建議。

經仔細分析發現這些問題是可以解決的,且可以在早期做較準確的定量分析,這需要在產品開發的初期PI仿真工作就要介入。

2. 初期評估與策略

如何在項目初期確定項目的電容濾波方案是最關鍵的步驟,業界已有成熟的EDA工具可以在項目初期提供較為精細的電容設計:包括電容容值組合、位置的放置、目標阻抗是否滿足等,如按相應的流程處理可以做到降低綜合成本、減少返工風險等。

目標阻抗

初期電容的評估與制定策略具體步驟如下:

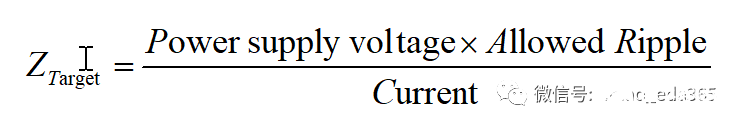

首先確定目標阻抗值,早期PI都是使用如下的方法確定目標阻抗,公式與結果樣圖如下:

圖 3. 目標阻抗計算公式

圖 4. 目標阻抗與仿真評估

這個估算方法在對于電流及鏈路上寄生電感影響越來越大的今天,再使用一條直線的目標阻抗已不能適應。

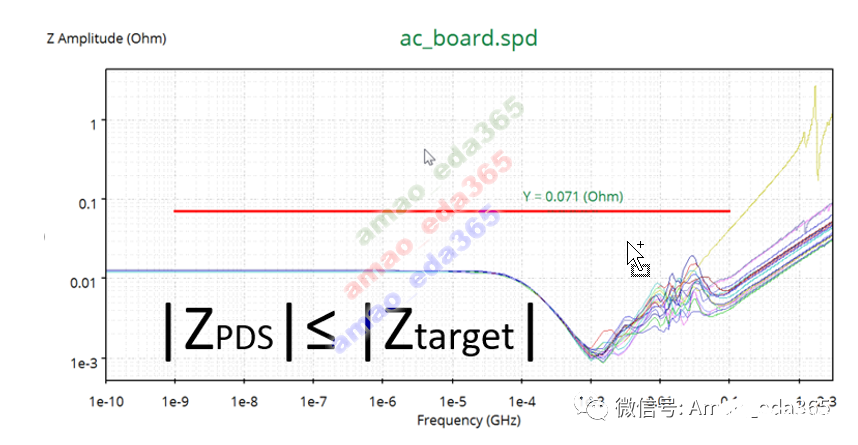

如下圖中使用與頻率相關的目標阻抗曲線,這使仿真時滿足目標阻抗值實現起來更接近現實狀況。

圖 5. 與頻率相關的目標阻抗

但對于低電壓,大電流的情況,目前這類目標阻抗評估還是顯得粗略,需要獲得在一個周期內logic門、buffer的詳細翻轉及精確的電流才能得到符合更真實的目標阻抗,由于“部門墻”及不同行業間的隔閡問題,這個想法在一般公司非常難以實現,因而很多公司會把重心轉到在封裝與及芯片內部的電容去耦的設計與策略上。

電容組合與精細設計

電容的位置范圍、電容的數量、電容的容值組合、使用何種Fanout形式等,這些只要流程及思路正確運用現有的商業EDA軟件,在設計的初期是可以實現,后期的Layout完成后基本就可以滿足目標阻抗的要求,即使要調整也只是很小的局部調整。

3. 項目中后期

SI工程師在單板完成后會對單板進行一次PowrAC的仿真(詳細操作過程可以參考《信號、電源完整性仿真設計與高速產品應用實例》11章),看看阻抗曲線是否滿足目標阻抗要求,很多時候仿真的結果是這樣:

(1) 阻抗曲線在某些頻點有較高的諧振,但沒有超過目標阻抗

(2) 目標阻抗滿足的地方只能到幾MHz。

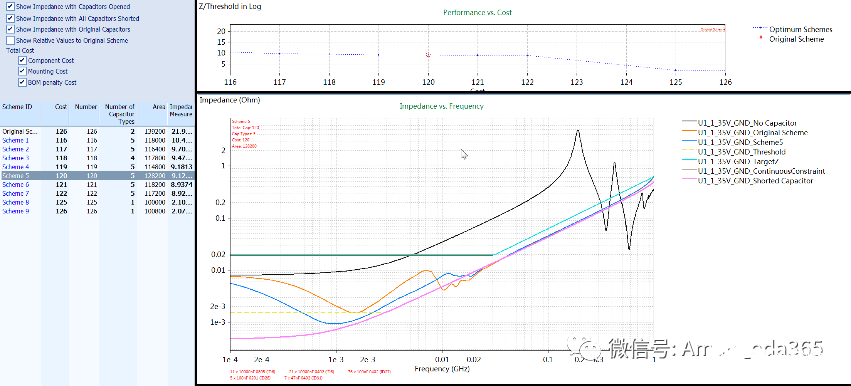

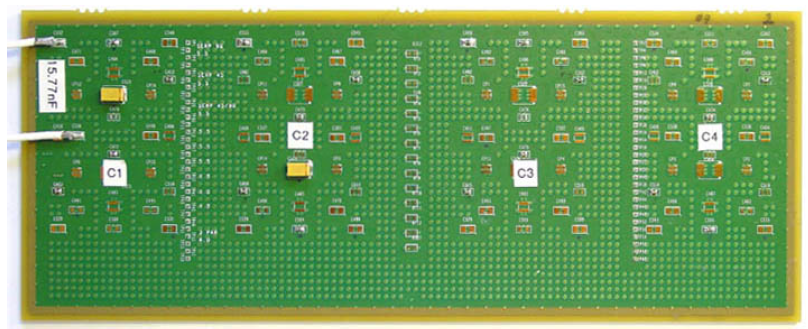

對于第一種情況,一般工程師不愿再作處理而默認PASS,第二種情況,則會嘗試加更高頻的電容進行改善,如沒掌握好方法這將會是一個較為繁瑣的手工迭代工作,因而選擇包括有各種優化項(最小的成本、最小的電容種類、最小的電容類型…。)的軟件(如OptimizedPI等軟件)進行PI仿真優化則是一個非常明智的選擇,軟件最后結果會給出多個方案供選擇,如下圖的結果所示。

圖 6. OptimizedPI完成的仿真效果

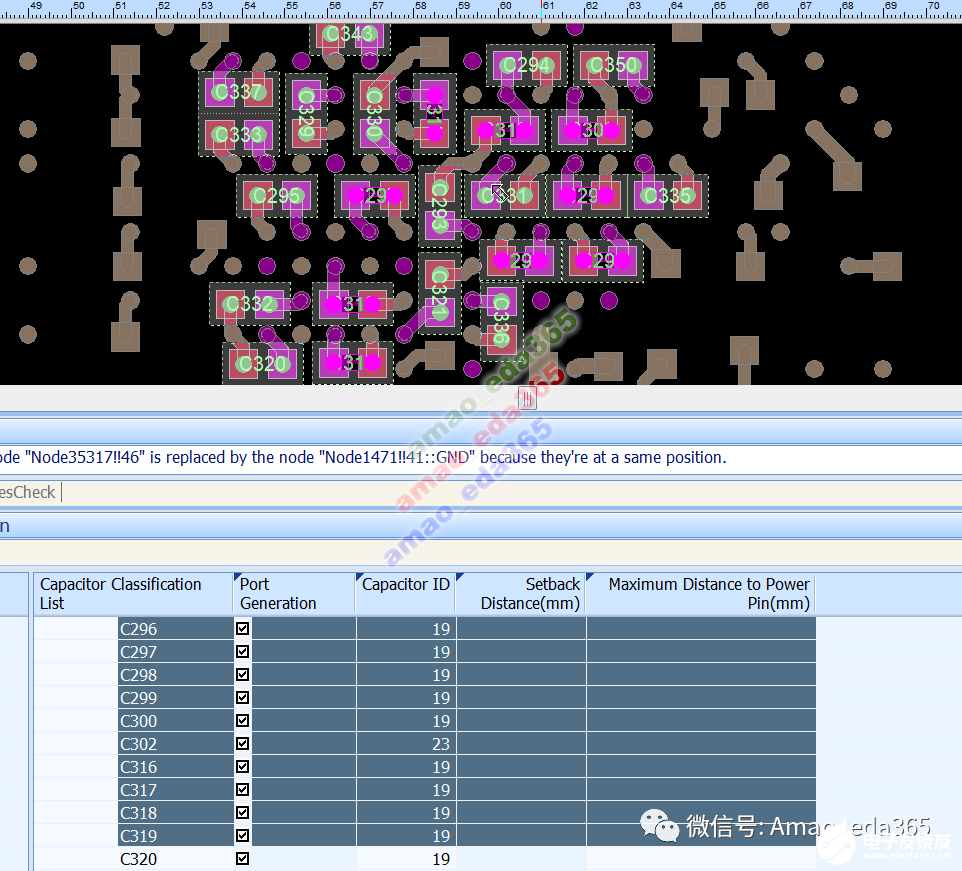

另一種方式,是所有工程師最愿意接受的方法,就是不改變當前的電容位置與大小,只是改變電容容值組合的優化需求,如下圖,這種方式可以通過使用類似于What if方式即可快速得到結果。

圖 7. Whatif 針對選定電容優化

但如目標阻抗人為不合理地設置太嚴格,通常會得不到優化結果,或優化結果根本就不可能實現,因而一個好的設計不是通過后期的優化得到,而是在項目初期基本定型,后期只需要較小的調整。

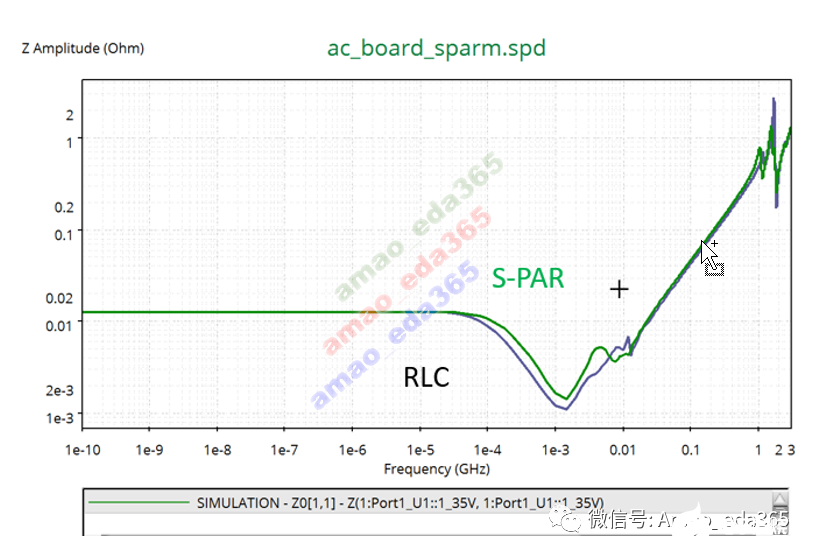

4. 電容模型與管理

項目仿真過程,不同軟件對電容的不同模型處理也不一樣,提供一套精確的電容電模型,對于結果精度的保證非常重要,電容模型可以由供應商提供或自行測量。由于各寄生參數的影響,不同模型的電容仿真出的結果會不一樣,如下圖同一個電容,在使用S參數模型與RLC模型時仿真出的結果會發現有一定的偏差。

圖 8. 電容使用S參數與RLC參考的仿真結果對比

5 。 總結

綜上所述,在進行PowerAC仿真時,應在項目前期介入并給出一個詳細、可行的方案,這樣對于后期的PDN優化工作量會非常小,而準備一套常用、準確的電容模型庫更能保證仿真的精度。

責任編輯:pj

-

電源

+關注

關注

185文章

18373瀏覽量

256400 -

單板

+關注

關注

0文章

32瀏覽量

11088 -

華秋DFM

+關注

關注

20文章

3504瀏覽量

5505

發布評論請先 登錄

PCB設計如何用電源去耦電容改善高速信號質量

面試常考:為什么芯片電源引腳的去耦電容一般選100nF?

干貨推薦!去耦電容的基本知識

去耦電容的基本知識

探索光耦:光耦在開關電源中的應用——保障高效、安全的電源控制

單板中的不同電源如何去耦?

單板中的不同電源如何去耦?

評論