有人采用STM32H743ZI芯片的SPI外設跟ADC器件通信,發現一旦SPI的SCK時鐘超過25MHz時,比如50Mhz,就會發生讀取數據失敗,并提示Busy忙信息或ERR錯誤信息。反正只要串行時鐘不超過25Mhz,收發都很正常。

但是STM32H743芯片手冊上明白地說了SPI時鐘最高可達150MHz,這會是什么原因呢?

根據他所提到的異常現象初步判斷,不論他的硬件方面還是軟件配置方面都應該沒有很大的問題,不然根本沒法通信。像這種情況有可能是下面幾種原因之一或組合原因【當然不僅限于這些】:

第一種情況就是通信速率明顯提高時,由于通信速率加快,而接收處理的相關代碼本身所用時間相對固定,這樣可能導致不能及時讀走數據而發生溢出,尤其是基于查詢方式或中斷方式接收處理時。這時我們可以考慮對接收代碼做進一步的精簡優化,壓縮接收處理時間,或者改用DMA方式進行數據的收發。

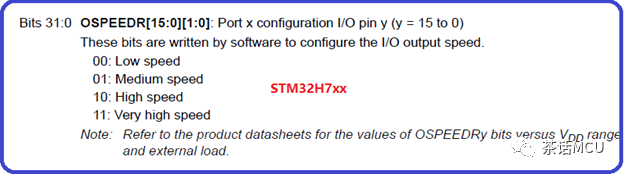

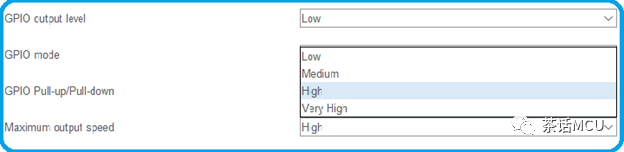

第二種情況就是當通信速率明顯提高時,跟外設復用的GPIO輸出速率檔位的配置沒有跟上來。以本案例來說,當我們將SPI的時鐘上到50MHz甚至更高時,若相應的GPIO的輸出速率配置還維持在相對低速水平,與實際輸出需求不相匹配時往往就會出現異常。

關于這個配置,如果使用STM32CubeMx配置的話就非常簡單,通過菜單選擇即可完成。如下圖所示:

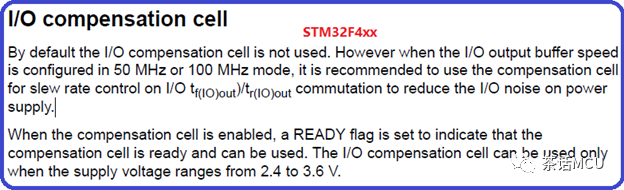

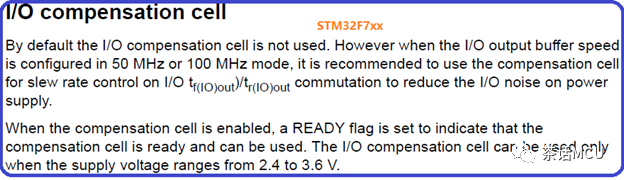

第三種情況就是當通信速率明顯提高時,即使相應的GPIO輸出能力配置也匹配了,但有些情況下還是有可能出通信異常的問題。我們知道,當GPIO輸出速率越來越高的時候,GPIO模塊帶來的噪聲也越大,作為通信口時其信號質量也會隨著通信速率的提升而變差,當然,此時芯片所需的功耗也隨之增大。對于很多STM32系列芯片,當GPIO輸出速率達到一定程度時,建議開啟片內GPIO補償單元。【下面截圖是兩個STM32系列關于GPIO補償單元的介紹文字】

該GPIO補償單元的作用就是通過控制IO口的輸出斜率,降低GPIO的噪聲對整個電源的影響并盡力改善信號質量,所以當我們基于STM32芯片實現較高速率的通信時,比方50Mhz甚至上百兆的SPI或USB通信時,如果芯片有GPIO補償單元的話,建議將其開啟。順便提醒下,使用GPIO補償單元的話,往往對電源電壓有相應要求,具體依手冊而定。

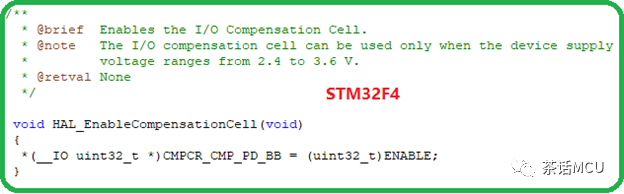

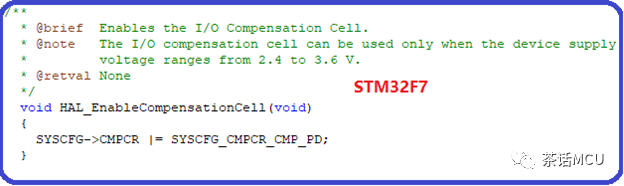

下面是分別基于STM32F4和STM32F7系列的HAL庫相關開啟GPIO補償單元的函數。

至于本案例異常的真正原因是什么呢?后來經確認屬于上面提到的第二種情況,GPIO輸出速率擋位選擇與實際輸出需求不匹配,稍加調整配置就好。

-

STM32

+關注

關注

2293文章

11031瀏覽量

364321 -

SPI

+關注

關注

17文章

1801瀏覽量

95731 -

GPIO

+關注

關注

16文章

1280瀏覽量

53979

原文標題:提高SPI時鐘時通信異常的案例分享

文章出處:【微信號:stmcu832,微信公眾號:茶話MCU】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

使用BLE(CYW20829)作為SPI slave和MCU(TC387)作為SPI master,調試SPI通信時遇到的問題求解

使用SPI進行通信,STM32F4做從機,通信時數據異常怎么解決?

DDP4422的SPI通信異常的原因?

iic協議與spi協議的區別

通信控制器驅動異常原因,怎么解決

KeyStone架構串行外設接口(SPI)手冊

ADS8688IDBT SPI讀取數據波形異常,為什么?

通信協議之SPI總線硬件篇

spi master接口的fpga實現

提高SPI時鐘時通信異常的案例分享

提高SPI時鐘時通信異常的案例分享

評論