1 簡(jiǎn)介

1.1 LPC1752及AT24C08C簡(jiǎn)介

LPC1752是NXP推出的一款Cortex M3的芯片,最高運(yùn)行頻率可達(dá)80M

AT24C08C是Atmel的一款I2C串行EEPROM,代替原來的型號(hào)AT24C08B及AT24C08A。共有8K(1024*8 bit)、1024字節(jié)的存儲(chǔ)單元。可進(jìn)行1百萬次的寫操作,數(shù)據(jù)可保存100年。

1.2 連接方式

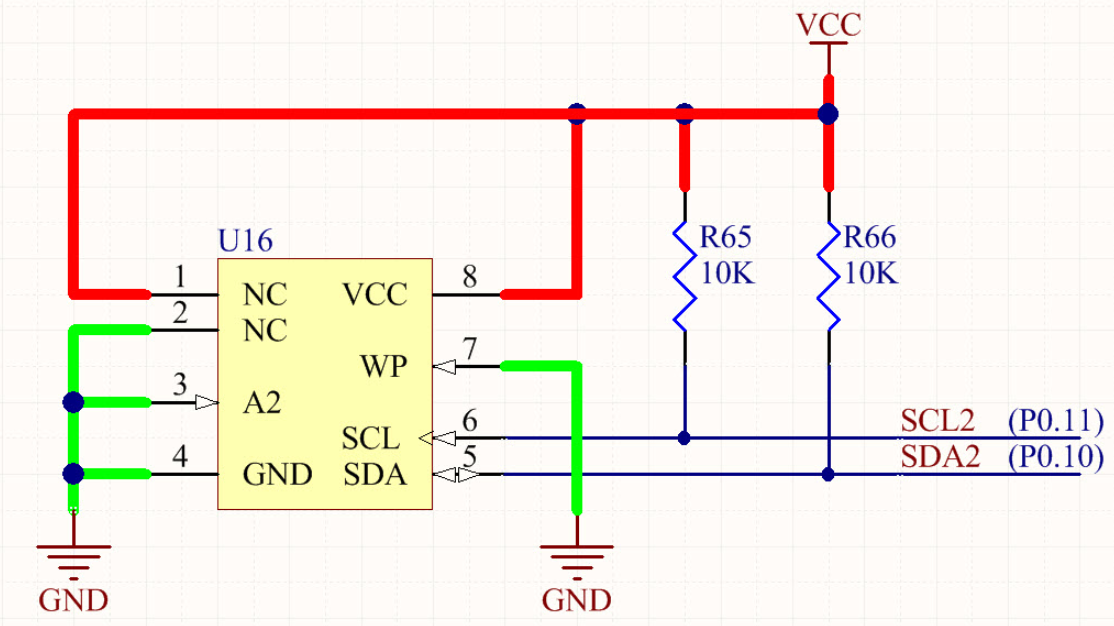

AT24C08C是通過LPC1752的I2C2連接的,連接圖如下:

圖1 LPC1752連接圖

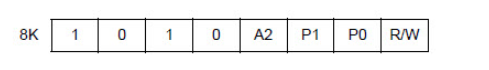

1.3 AT24C08C設(shè)備地址

The 8K EEPROM only uses the A2 device address bit with the next twobits (P1, P0) being for memory page addressing. The A2 bit must compare to itscorresponding hardwired input pin. The A1 and A0 pins are not connected.

根據(jù)連接圖可得知AT24C08的地址為0xA0。

圖2 AT24C08CDevice Address

1.4 I2C運(yùn)行時(shí)鐘頻率

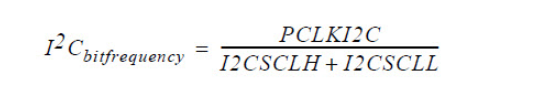

主機(jī)模式下必須通過對(duì)I2SCLH和I2SCLL寄存器進(jìn)行設(shè)置來選擇合適的總線速率和占空比。I2SCLH定義SCL高電平所保持的PCLK_I2C周期數(shù),I2SCLL定義SCL低電平的PCLK_I2C周期數(shù)。位頻率由下面的公式得出(PCLK_I2C是外圍總線APB的頻率):

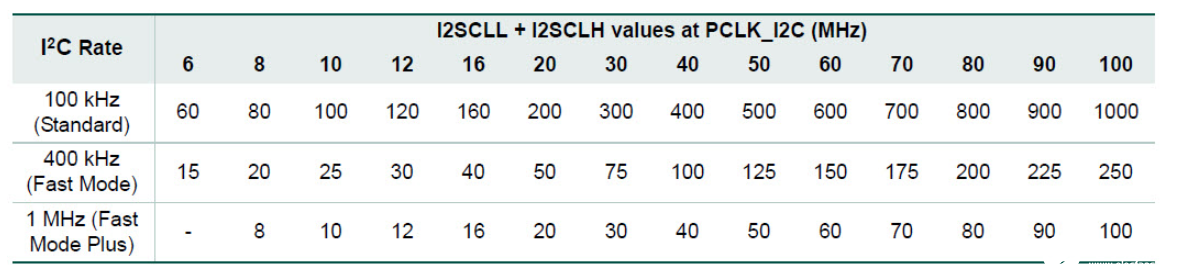

選用的I2SCLL和I2SCLH值必須確保得出的總線速率在I2C總線速率的范圍之內(nèi)。I2SCLL和I2SLH的值都必須大于或等于4。表1給出了根據(jù)PCLK_I2C頻率和I2SCLL和I2SCLH值計(jì)算出來的I2C總線速率的示例。

表1 I2C時(shí)鐘速率的實(shí)例

2 函數(shù)介紹

2.1 初始化函數(shù)i2c2_init

按照LPC1752用戶手冊(cè)(UM10360)中第三章的介紹進(jìn)行初始化,步驟如下:

a)。 電源:在寄存器PCONP中置位PCI2C2。

b)。 時(shí)鐘:在寄存器PCLK_SEL1中選擇PCLK_I2C2。

c)。 引腳: 通過寄存器PINSEL0使能I2C2引腳。通過寄存器PINMODE來配置I2C2引腳模式。

d)。 時(shí)鐘頻率:向I2SCLH和I2SCLH寄存器加載頻率值來定義串行時(shí)鐘頻率(主機(jī)模式)。

e)。 中斷:在NVIC中置位I2C2_IRQn寄存器使能I2C2中斷。

f)。 向寄存器I2CONSET寫入0x40來置位I2EN位。

2.2 中斷函數(shù)I2C2_IRQHandler

通過讀取I2STAT寄存器的值判斷I2C總線上的狀態(tài),并進(jìn)行下一步操作。

中斷函數(shù)只處理了主機(jī)接收模式與主機(jī)發(fā)送模式。

1)I2C進(jìn)入主機(jī)進(jìn)入發(fā)送起始條件時(shí),串行中斷標(biāo)志(SI)置位,狀態(tài)寄存器(I2STAT)中的狀態(tài)代碼為0x08。此時(shí)將從機(jī)地址和數(shù)據(jù)方向位(SLA+W)裝入I2DAT,同時(shí)復(fù)位I2CON的STA,STO和SI。

2.3 I2C總線進(jìn)入開始狀態(tài)i2c2_start

可通過置位STA位進(jìn)入主機(jī)發(fā)送模式。一旦總線空閑,I2C邏輯會(huì)馬上測(cè)試I2C總線并產(chǎn)生一個(gè)起始條件。

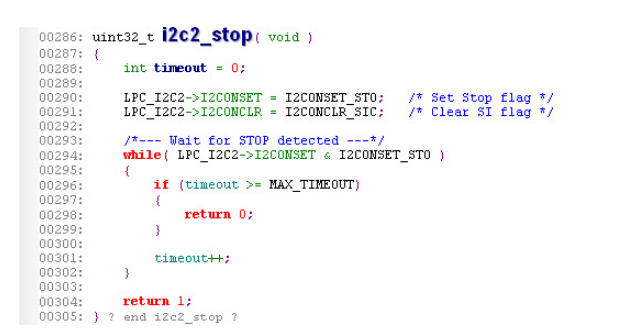

2.4 I2C停止函數(shù)i2c2_stop:

I2C結(jié)束時(shí)發(fā)送停止條件并釋放總線。

a)向I2CONSET寫入0x14來置位STO和AA位;

b)向I2CONCLR寫入0x08來清除SI標(biāo)志;

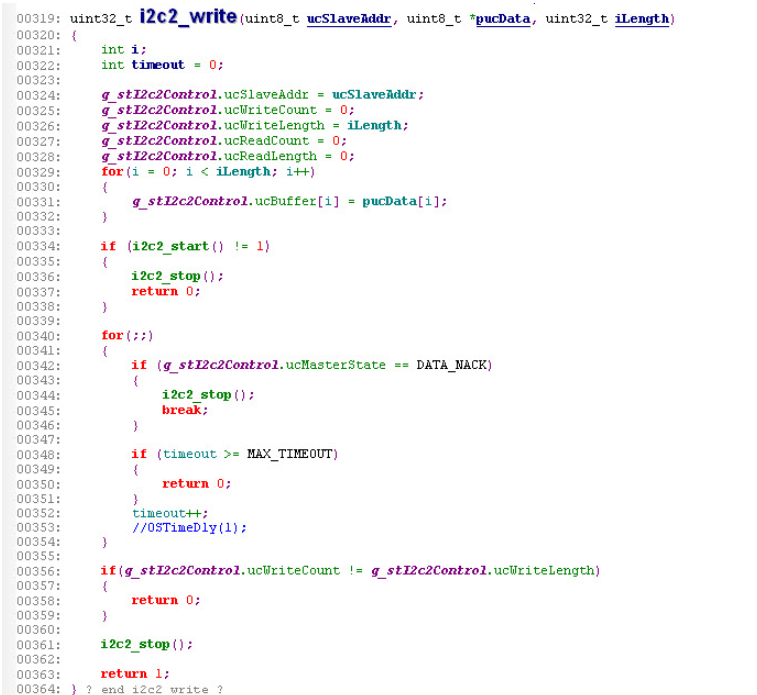

2.5主機(jī)發(fā)送函數(shù)i2c2_write

啟動(dòng)主機(jī)發(fā)送功能,向從機(jī)發(fā)送數(shù)據(jù),通過建立緩沖區(qū)、指針和數(shù)據(jù)計(jì)數(shù)然后發(fā)啟起始條件便可執(zhí)行主發(fā)送操作。

a)初始化主機(jī)數(shù)據(jù)計(jì)數(shù)器;

b)建立數(shù)據(jù)將被發(fā)送到的從機(jī)地址,并且添加寫位;

c)向I2CONSET寫入0x20來置位STA位;

d)在主發(fā)送緩沖區(qū)內(nèi)建立要發(fā)送的數(shù)據(jù);

e)初始化主機(jī)數(shù)據(jù)計(jì)數(shù)器來匹配正在發(fā)送的信息長(zhǎng)度;

f)退出。

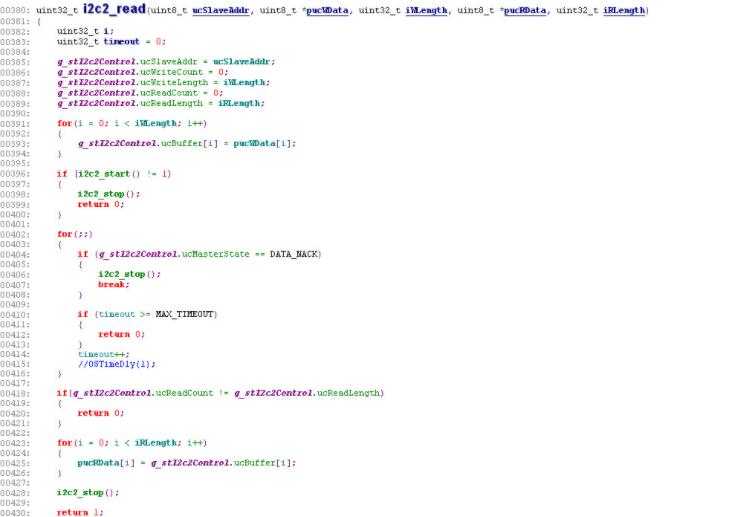

2.6主機(jī)接收函數(shù) i2c2_read

啟動(dòng)主機(jī)接收功能,接收從機(jī)發(fā)出的數(shù)據(jù)。

通過建立緩沖區(qū)、指針和數(shù)據(jù)計(jì)數(shù)然后發(fā)啟起始條件便可執(zhí)行主接收操作。

a)初始化主機(jī)數(shù)據(jù)計(jì)數(shù)器;

b)建立數(shù)據(jù)將被發(fā)送到的從機(jī)地址,并且添加讀位;

c)向I2CONSET寫入0x20來置位STA位;

d)在主接收緩沖區(qū)內(nèi)建立要發(fā)送的數(shù)據(jù);

e)初始化主機(jī)數(shù)據(jù)計(jì)數(shù)器來匹配正在發(fā)送的信息長(zhǎng)度;

f)退出。

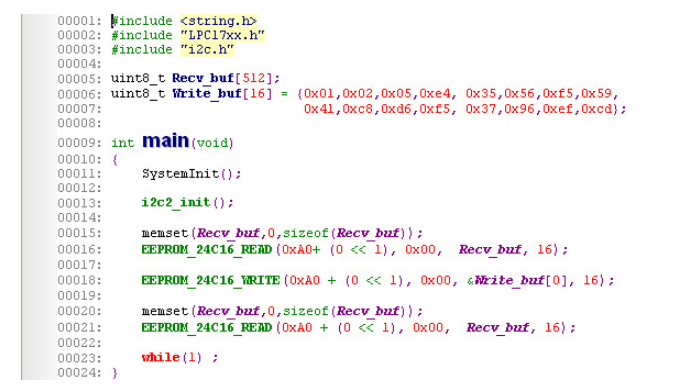

3 測(cè)試

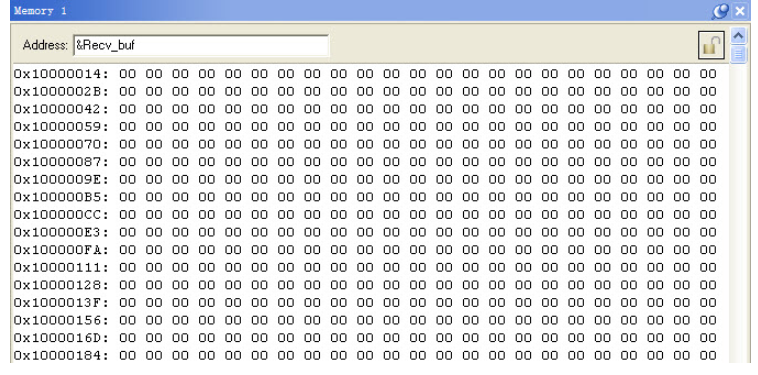

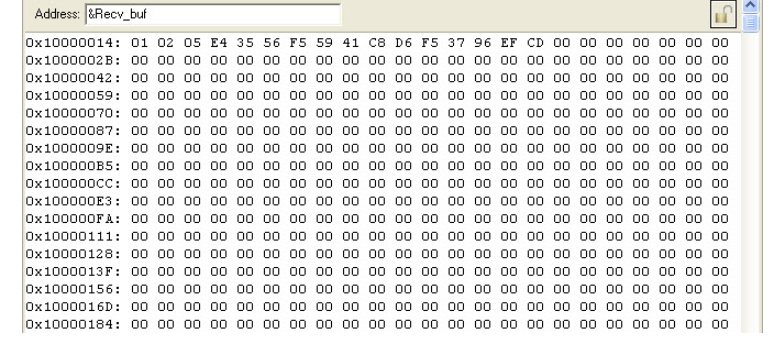

通過向0x00地址寫入并回讀固定數(shù)據(jù)驗(yàn)證有效性。

測(cè)試結(jié)果比較

第一次讀取

第二次讀取

經(jīng)驗(yàn)證可以正常使用。

編輯:hfy

-

寄存器

+關(guān)注

關(guān)注

31文章

5424瀏覽量

123497 -

存儲(chǔ)單元

+關(guān)注

關(guān)注

1文章

66瀏覽量

16371 -

EEPROM

+關(guān)注

關(guān)注

9文章

1083瀏覽量

83329 -

Cortex M3

+關(guān)注

關(guān)注

0文章

7瀏覽量

8661 -

LPC1752

+關(guān)注

關(guān)注

0文章

4瀏覽量

3601

發(fā)布評(píng)論請(qǐng)先 登錄

PFD12-36S24B2(C)5 PFD12-36S24B2(C)5

FD12-36S24A3(C)4 FD12-36S24A3(C)4

FD6-36S24A3C3 FD6-36S24A3C3

FD6-36D24A3(C) FD6-36D24A3(C)

FW2-24S15C3 FW2-24S15C3

FW2-24S15C FW2-24S15C

NN3-24S24C4N NN3-24S24C4N

NN3-12S24C3N NN3-12S24C3N

FN2-24D24C3N FN2-24D24C3N

FN2-24D15C FN2-24D15C

FN2-24D15C3 FN2-24D15C3

FA10-220S24C2N3 FA10-220S24C2N3

FA5-220D24C2N4 FA5-220D24C2N4

鐵電存儲(chǔ)器SF24C64對(duì)標(biāo)FM24C64性能、應(yīng)用和成本分析

采用LPC1752讀取AT24C08C的原理與實(shí)現(xiàn)方案

采用LPC1752讀取AT24C08C的原理與實(shí)現(xiàn)方案

評(píng)論