用于網(wǎng)絡(luò)的RF板、高速處理器的板以及許多其他系統(tǒng)對(duì)串?dāng)_強(qiáng)度有嚴(yán)格的要求。信號(hào)標(biāo)準(zhǔn)中并不總是規(guī)定最大串?dāng)_強(qiáng)度,而且在設(shè)計(jì)中串?dāng)_最強(qiáng)烈的地方也不總是很明顯。盡管您可能會(huì)嘗試對(duì)設(shè)計(jì)進(jìn)行正確的布局規(guī)劃,但您可能會(huì)發(fā)現(xiàn)布局和布線會(huì)因攻擊者的蹤跡而產(chǎn)生強(qiáng)烈的串?dāng)_。

那么,在設(shè)計(jì)中哪里可以找到串?dāng)_,以及在PCB中識(shí)別出不良走線的最簡(jiǎn)單方法是什么?您可以使用全波場(chǎng)求解器,但是可以在PCB設(shè)計(jì)軟件中使用更簡(jiǎn)單的分析功能來識(shí)別和抑制串?dāng)_。用于PCB設(shè)計(jì)和布局的最佳布局后仿真工具將使用具有簡(jiǎn)化數(shù)值算法的場(chǎng)求解器來計(jì)算附近走線之間的串?dāng)_,從而為您提供一種在設(shè)計(jì)中發(fā)現(xiàn)串?dāng)_的快速方法。

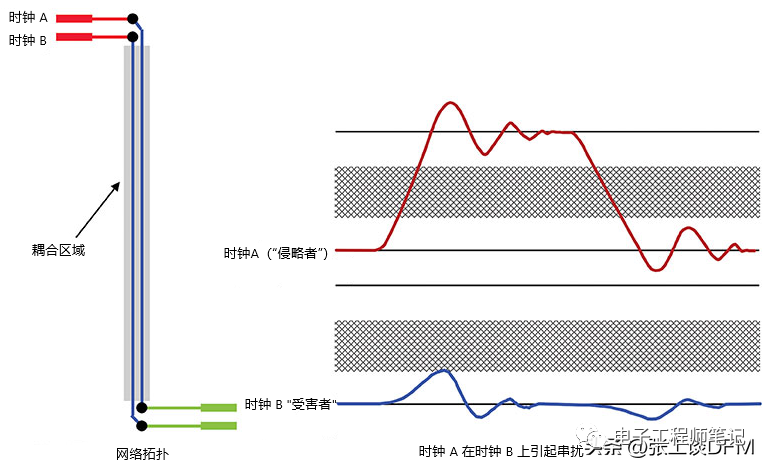

很簡(jiǎn)單,在PCB中承載信號(hào)的任何兩個(gè)導(dǎo)體之間都可能發(fā)生串?dāng)_。這包括數(shù)字和模擬網(wǎng)絡(luò)。當(dāng)發(fā)生串?dāng)_時(shí),一根導(dǎo)體(攻擊者網(wǎng)絡(luò))上的信號(hào)將其自身的一部分耦合為附近導(dǎo)體(受害者網(wǎng)絡(luò))上的新信號(hào)。數(shù)字和模擬信號(hào)可能以不同的方式引起串?dāng)_。

串?dāng)_以兩種方式耦合到信號(hào)網(wǎng)絡(luò)之間,具體取決于兩條或多條走線之間存在的主要寄生類型:

電容串?dāng)_。這種串?dāng)_是由于兩條導(dǎo)體之間的寬邊寄生電容和接地耦合電容而發(fā)生的。電容性串?dāng)_的大小與兩個(gè)導(dǎo)體之間的寄生電容成正比。對(duì)于模擬信號(hào),容性耦合信號(hào)的強(qiáng)度隨頻率而增加,因此這種串?dāng)_在高頻網(wǎng)絡(luò)或數(shù)字信號(hào)具有非常快的邊沿速率時(shí)會(huì)占主導(dǎo)地位。數(shù)字信號(hào)會(huì)在開關(guān)期間和之后引起瞬態(tài)振鈴,從而引起電容性串?dāng)_。

感應(yīng)串?dāng)_。這種類型的串?dāng)_是由于導(dǎo)體的兩個(gè)回路之間的寄生電感引起的。來自模擬攻擊者信號(hào)的感應(yīng)串?dāng)_信號(hào)的大小與攻擊者跡線中電流變化的速率成比例(即,與信號(hào)頻率成比例)。數(shù)字信號(hào)會(huì)在開關(guān)過程中引起感應(yīng)串?dāng)_,在此期間,從信號(hào)發(fā)出的磁場(chǎng)會(huì)在受害網(wǎng)絡(luò)中感應(yīng)變化的通量。

電感和電容串?dāng)_分別取決于兩條走線之間的互感和互電容。這些術(shù)語完全取決于不同導(dǎo)體之間的電磁相互作用和靜電相互作用,以及這些導(dǎo)體在空間中的排列方式。這意味著您需要在布局后仿真中分析串?dāng)_。您無法做任何事情來從原理圖中發(fā)現(xiàn)串?dāng)_。

找出兩種類型的串?dāng)_都需要一些獨(dú)特的分析步驟。您可以嘗試使用串?dāng)_系數(shù)的解析方程式來量化不同類型的串?dāng)_,這將告訴您在受害者網(wǎng)絡(luò)上感應(yīng)出的攻擊者信號(hào)電平的分?jǐn)?shù)。但是,由于實(shí)際PCB布局中的幾何結(jié)構(gòu)可能變得非常復(fù)雜,因此它們將不可避免地近似,從而使得互感和互電容難以精確確定。更好的選擇是直接從PCB設(shè)計(jì)程序中使用布局后仿真工具。

完成PCB布局后,您可以采取步驟嘗試并找出可能遭受大量串?dāng)_的網(wǎng)絡(luò)。由于任何PCB中的幾何形狀都很復(fù)雜,因此任何給定的網(wǎng)絡(luò)上都會(huì)存在多個(gè)寄生現(xiàn)象,即使您遵循基本的走線寬度和間隔規(guī)則,也可能會(huì)看到強(qiáng)烈的串?dāng)_ 。在具有數(shù)百個(gè)網(wǎng)絡(luò)的密集電路板上,您無需模擬每條跡線之間的串?dāng)_。取而代之的是,您只需要選擇關(guān)鍵網(wǎng)絡(luò)作為受害者跡線,并查看附近可能充當(dāng)攻擊者跡線的網(wǎng)絡(luò)。

為此,您需要使用兩個(gè)重要的仿真工具來分析串?dāng)_:

耦合分析。該分析的目的是確定兩條跡線之間的耦合系數(shù),并采取措施減小耦合系數(shù)太大的耦合系數(shù)。

串?dāng)_分析。顧名思義,這涉及從攻擊者到受害者的串?dāng)_信號(hào)的直接仿真。這是一個(gè)時(shí)域仿真,它將向您顯示由于串?dāng)_而在受害網(wǎng)上引入的確切波形。

耦合分析

運(yùn)行此工具時(shí),用戶選擇要分析的網(wǎng)絡(luò)。一旦計(jì)算出結(jié)果,就可以在您的布局中以表格格式和可視格式查看它們。受害者網(wǎng)絡(luò)與其攻擊者網(wǎng)絡(luò)之間的耦合長(zhǎng)度和強(qiáng)度可以在您的布局中視為熱圖,從而使您可以確定需要糾正的網(wǎng)絡(luò)。

在下圖中,網(wǎng)絡(luò)N22287555與VDDS的耦合最強(qiáng),這表明數(shù)字電源層中的噪聲很容易耦合到該網(wǎng)絡(luò)。網(wǎng)絡(luò)USB0_ID與網(wǎng)絡(luò)N22155575具有強(qiáng)耦合。這兩個(gè)網(wǎng)絡(luò)位于不同的層上,但沒有被接地層隔開。這應(yīng)該說明在不同層的信號(hào)之間放置接地層的效果;它降低了潛在耦合信號(hào)的強(qiáng)度。可以使用熱圖從視覺上識(shí)別存在高耦合的特定區(qū)域,該熱圖顯示了可能需要調(diào)整布線的哪個(gè)區(qū)域以抑制串?dāng)_。

解決PCB布局中的串?dāng)_問題

一旦確定了容易受到串?dāng)_的網(wǎng)絡(luò),就需要分離受害者和侵害者的跡線,或者在它們之間提供更大的隔離度。您永遠(yuǎn)無法完全消除串?dāng)_,但可以將其降低到不會(huì)導(dǎo)致接收機(jī)意外切換(對(duì)于數(shù)字信號(hào))或波形失真過度(對(duì)于模擬信號(hào))的程度。這可以通過多種方式完成:

增加走線之間的間距。串?dāng)_與兩條跡線之間的電磁場(chǎng)強(qiáng)度成正比。增大受害者和攻擊者走線之間的間隔將降低受害者看到的場(chǎng)強(qiáng),然后將降低耦合的串?dāng)_信號(hào)的強(qiáng)度。

在不同的層上路由受害者痕跡。如果創(chuàng)建堆棧以支持高速信號(hào),則很可能在平面層之間具有交錯(cuò)的信號(hào)層。平面層將提供不同信號(hào)層之間的自然隔離。如果沒有空間在其當(dāng)前層上移動(dòng)信號(hào)路徑,則可以在不同的信號(hào)層中路由受害跡線或差分對(duì)。

將走線移到更靠近接地平面的位置。接地平面會(huì)使攻擊者跡線產(chǎn)生的電場(chǎng)和磁場(chǎng)失真,并增加它們之間的隔離度。

在有問題的跡線之間放置防護(hù)痕跡或通過圍欄。就像在使用接地層一樣,在兩個(gè)走線之間放置接地走線或通過圍欄也可以提供一定的屏蔽。每當(dāng)您放置隔離結(jié)構(gòu)時(shí),最好始終使用3D EM場(chǎng)求解器量化該結(jié)構(gòu)的效果 。

注意串?dāng)_是一個(gè)相互的過程。如果兩條走線攜帶相同類型的信號(hào),則受害走線將在攻擊者走線上產(chǎn)生相同的串?dāng)_信號(hào)。這意味著解決一個(gè)網(wǎng)絡(luò)的串?dāng)_問題也將抑制其攻擊者的串?dāng)_。

從表面微帶切換到帶狀線意味著帶狀線在被導(dǎo)體圍繞時(shí)會(huì)產(chǎn)生較少的串?dāng)_,并且會(huì)被屏蔽以免受表面微帶的影響。通常,如果從微帶切換到具有相同特征阻抗和間距的帶狀線,則帶狀線的串?dāng)_會(huì)比微帶小。

無論您是在另一層上路由受害信號(hào)還是增加間隔,都可能需要檢查走線中的長(zhǎng)度匹配。通過通孔布線會(huì)產(chǎn)生額外的傳播延遲,這會(huì)在并行網(wǎng)絡(luò)或差分對(duì)中引起 偏斜。請(qǐng)注意,如果愿意,可以將差分對(duì)的一端穿過內(nèi)部層,只要您保持差分阻抗即可。

更改路由或?qū)佣褩:螅?qǐng)使用軟件中的“串?dāng)_分析”和“阻抗分析”工作流再次檢查布局。這將確保您保持阻抗控制,同時(shí)將串?dāng)_降低到可接受的水平。

編輯:hfy

-

阻抗控制

+關(guān)注

關(guān)注

1文章

57瀏覽量

10785

發(fā)布評(píng)論請(qǐng)先 登錄

高速PCB板設(shè)計(jì)中的串擾問題和抑制方法

解決PCB設(shè)計(jì)消除串擾的辦法

高速PCB設(shè)計(jì)中的串擾分析與控制

高速PCB中微帶線的串擾分析

PCB串擾如何解決

串擾在高速PCB設(shè)計(jì)中的影響分析

如何解決PCB布局中的串?dāng)_問題

如何解決PCB布局中的串?dāng)_問題

評(píng)論