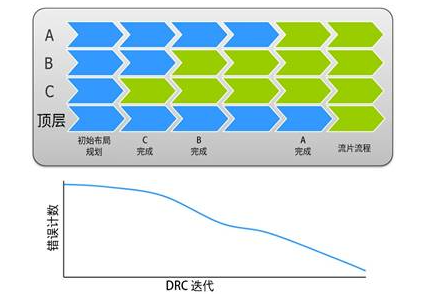

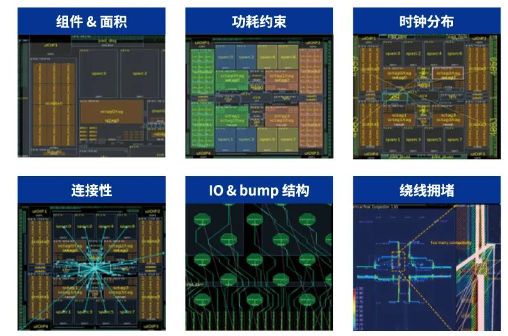

鑒于先進工藝設計的規模和復雜性,而且各方為 搶先將產品推向市場而不斷競爭,片上系統 (SoC) 設計團隊沒有時間等到所有芯片模塊都全 部完成后才開始組裝芯片。因此,SoC 設計人員 通常會在模塊開發的同時開始芯片集成工作,以 便在設計周期的早期捕獲并糾正任何布線違規, 從而幫助縮短至關重要的上市時間。錯誤在早期 階段更容易修復,而且對版圖沒有重大影響,設 計人員在此階段消除錯誤,可以減少實現流片所 需的設計規則檢查 (DRC) 迭代次數(圖 1)。

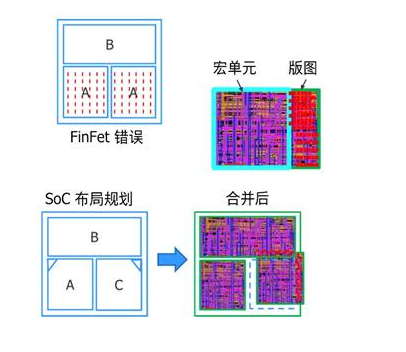

但是,早期階段芯片級物理驗證面臨許多挑 戰。通常,在布局規劃的早期階段,未完成模 塊中報告的違規數量非常多,導致此現象的原 因是許多系統性問題可能廣泛分布在整個設計中。系統性問題的典型例子包括:SoC 級別的模塊布局偏離網格、SoC MACRO 封裝外發生IP 合并、保留布線層上發生 IP 布線、時鐘網絡上的過孔類型 不正確,以及 SoC 中 IP 布局方向不匹配,如圖 2 所示。在這 個階段區分模塊級違規和頂層布線違規并非易事。

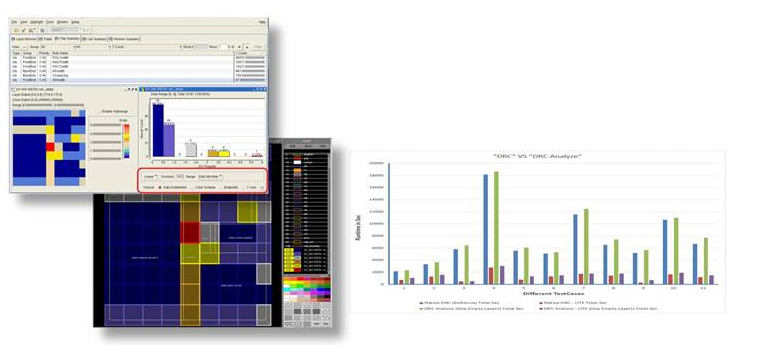

圖 1:識別和解決芯片集成問題與模塊開發并行 進行,可最大程度地減少整個設計實現流程中 的 DRC 迭代次數。

對初始 DRC 運行使用晶圓代工廠規則集中的默認設置,通常會 導致運行時間非常長,還會報告非常多的違規,并產生極其龐 大的結果數據庫,所有這些都使得調試極其困難且耗時。

圖 2:系統性錯誤常常導致早期芯片級驗 證中出現大量違規。

在此早期階段,SoC 設計人員的目標通常是最大限度地減少每 次 DRC 迭代的運行時間,并且僅關注此時相關的違規情況。 除了將模塊違規與需要調試的布線違規區分開來之外,SoC 設 計人員還可以將模塊違規送回模塊所有者進行調試和更正。 從早期的布局規劃到最終的產品流片,SoC 設計人員的終極目 標是發現并修復 SoC 系統性問題。

改善錯誤較多的模塊/芯片級驗證

Calibre? Reconnaissance (Calibre Recon) 工具是一個完整的功能包,支持設計團隊在設計周 期的早期階段(此時各種組件尚不成熟)便開始對整個芯片設計版圖進行探索和物理驗 證。Caliber Recon 工具能夠非常有效地發現早期潛在的集成問題,向設計團隊快速提供反 饋以便其采取適當的糾正措施,最終減少 DRC 迭代次數,縮短總周轉時間,加快產品上市。 此外,Caliber Recon 工具經過精心設計,從第一次運行便能提供所有這些功能,支持在任何 工藝技術節點上按原樣使用任何晶圓代工廠/獨立設備制造商 (IDM) 的 Caliber sign-off 設計 套件。

自動檢查選擇

當存在錯誤時,某些規則檢查往往會運行很長時 間。取消選擇此類規則可以大大加快運行速度,但 設計人員如何確定取消選擇哪些檢查呢?取消選擇涉 及許多操作的檢查?還是取消選擇某一類檢查,例 如天線檢查或所有連通性檢查?選擇運行 “最佳” 的一 組檢查并不容易,這可能需要進行大量的高級分 析,并對晶圓代工廠規則集進行一些編輯(圖 3)。

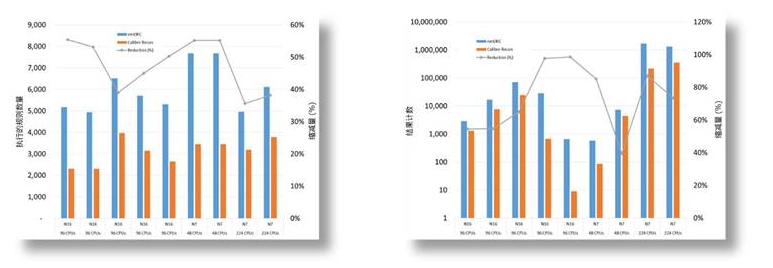

Caliber Recon 工具可自動取消選擇與當前開發階段無 關的檢查。Calibre 引擎根據檢查類型和檢查涉及的操 作數量來決定取消選擇哪些檢查,以提供良好的覆蓋率、加快運行時間并減少內存消耗。對于各種工藝節點,平均而言,Caliber Recon 工具可將 要執行的檢查數量減少約 50%。取消選擇的檢查/類別會在過程記錄副本中報告,以供用戶 參考。Caliber Recon 工具也會接受用戶手動取消選擇的所有檢查/類別。

圖 3:選擇正確的檢查集合進行早期驗 證需要仔細分析。

自動取消選擇檢查時,報告的違規總數通常會減少到原數量的 70% 左右(圖 4)。但這些違 規對于目標實現階段更有意義,有助于分析和調試實際系統性問題。

圖 4:使用 Caliber Recon 功能時執行的規則檢查總 數量的減少情況,以及最 終報告的違規數量的減少 情況。

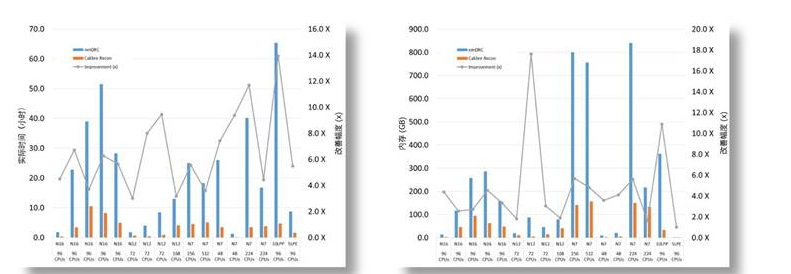

Caliber Recon 工具最多可將整體 DRC 運行時間縮短為原來的 1/14,同時仍能檢查總 DRC 集合的大約 50%。Calibre 引擎自動選擇的規則子集可以有效識別布局規劃和子芯片集成問 題,向設計團隊快速提供反饋以便采取適當的糾正措施,并顯著縮短總周轉時間。圖 5 基于 測試顯示了不同芯片的 DRC 運行時間結果。

圖 5:在各種芯片上測試 Caliber Recon 自動檢查選 擇的結果表明,早期實 現階段的 DRC 運行時間和 內存耗用量大幅減少。

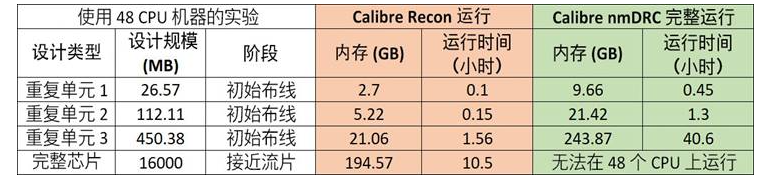

Caliber Recon 驗證不僅能幫助 SoC 設計人員進行早期芯片級驗證,而且支持早期模塊驗證。 因為模塊和芯片設計是并行完成,所以模塊設計人員可以在模塊上運行 Caliber Recon 驗證。 如果報告了錯誤,模塊設計人員可以修復系統性問題。如果 Caliber Recon 結果無錯誤,便可 將模塊傳遞給芯片,而模塊設計人員可以在該模塊上并行運行其余規則。如圖 6 所示,在初 始布線期間對模塊(重復單元)運行 Caliber Recon 工具可使運行時間縮短 8 倍,內存占用減 少 4 倍。

圖 6:在不同的開發階段 時,將針對重復單元和完 整芯片執行的 Calibre Recon 和完整 Calibre nmDRC 進 行比較,結果顯示 Calibre Recon 的運行時間和內存 耗用量都減少。

灰框排除

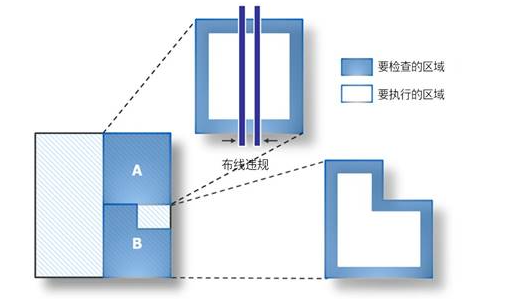

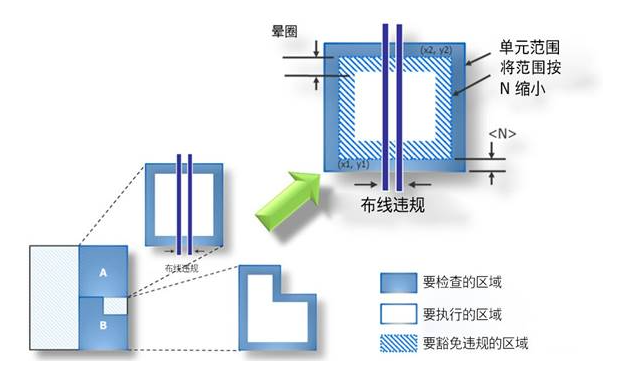

遵循相同的排除概念,但這次是從設計 角度來看,是否有可能忽略設計的某些 部分(主要是不成熟的模塊),從而聚 焦于接口和布線違規并減少運行時間? Caliber Recon 灰框功能允許設計人員在 檢查頂層布線時不必考慮單元細節。 灰框標記可移除指定單元中的數據,而 不會從更高的父層級中刪除幾何形狀

(圖 7)。因此,指定單元上的任何布線 違規仍能被捕捉到。此外,設計人員可 以通過縮小單元的范圍來在移除的幾何 形狀周圍保留一個暈圈,以便捕獲指定 單元與其相鄰單元之間的接口違規。

圖 7:利用 Caliber Recon 灰框標記,設計人員可以從 DRC 中排除版圖的某些部分,同時仍能檢查這些區域是 否存在接口或布線違規。

灰框解決方案對于矩形和非矩形單元均適用,但設計人員可能需要指定代表非矩形單元范 圍的層(邊界層可用于此目的)。

雖然灰框功能可縮短運行時間,但從指定單元中移除幾何形狀可能會引入一些新的 DRC 違 規,這將需要額外的調試來區分哪些是實際違規,哪些是因為從指定單元中切除幾何形狀所 產生的違規。為了避免此問題,以及免于編輯晶圓代工廠規則集來為灰框功能增加規范說 明,設計人員可以將 Caliber Recon 灰框功能與 Caliber Auto-Waivers 功能結合使用。如圖 8 所示,其主要目的是不檢查不完整模塊中的幾何形狀以縮短運行時間,附帶的好處是可豁免 從指定單元排除區域時所引入的任何違規。這種結合使得設計人員可以專注于原始(有效) DRC 接口違規。所有豁免的違規都保存到豁免結果數據庫文件中,供日后需要時審查。

圖 8:Caliber Recon 灰框 功能與 Calibre Auto-Waiver 功能相結合,使得設計人 員可以執行接口和頂層布 線驗證,而不必擔心因為 從灰框單元中移除幾何形 狀而產生錯誤。

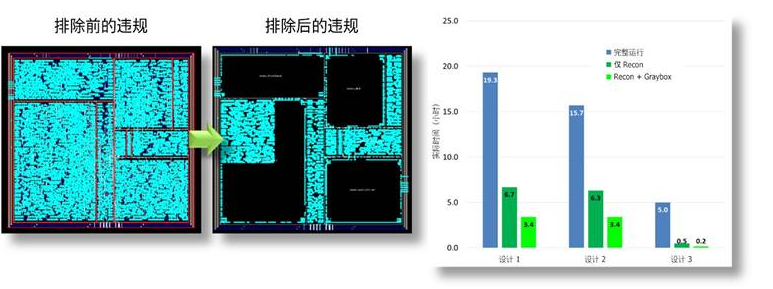

灰框解決方案能將 SoC 團隊指向需要注意的接口 DRC 錯誤。它還將與組裝相關的集成和布 線違規與不成熟模塊的違規區分開來。如圖 9 所示,將此功能與自動選擇相關檢查相結合, 可進一步縮短運行時間,因為系統會針對設計區域報告的違規,選擇其中需要在特定階段 多加注意的違規,讓設計人員只專注在這些違規上。因此,它有助于設計團隊在設計周期 的早期解決更多關鍵接口問題,避免最后一刻出現令人沮喪的意外。

圖 9:Caliber Recon 自動 檢查選擇與灰框功能結合 使用,有助于在早期設計 實現階段將驗證重點放在 關鍵接口和布線問題上。

DRC ANALYZE

Caliber Recon DRC Analyze 功能可幫助設計人員快速分析其設計并直觀地查看錯誤分布,以 便找出可快速提高版圖質量的機會點。

DRC Analyze 功能允許設計人員繪制不同的直方圖(基于層次化單元或窗口)以進行芯片分 析,并為這些直方圖指定自定義縮放范圍。它還支持繪制結果的彩色圖,既可以在獨立窗 口上繪制,也可以映射到設計上,讓設計人員能夠探查每個單元和每個窗口的錯誤細節, 結果會分布在整個設計上(圖 10)。

圖 10:Caliber Recon DRC Analyze 功能支持在錯誤 檢查和調試過程中進行 快速、深入的可視化和 分析。

DRC Analyze 功能的主要優點是,設計人員可以使用晶圓代工廠規則集來執行所有必需的分 析,而無需進行任何編輯。與這種分析在芯片分析和調試期間提供的價值相比,相關開銷

(運行時間平均增加 10% 和內存耗用量平均增加 20% )非常小。

編輯:hfy

-

soc

+關注

關注

38文章

4303瀏覽量

221087 -

晶圓代工

+關注

關注

6文章

866瀏覽量

48967 -

芯片分析

+關注

關注

0文章

3瀏覽量

10406

發布評論請先 登錄

相關推薦

【「芯片通識課:一本書讀懂芯片技術」閱讀體驗】芯片如何設計

深入解析:SiP與SoC的技術特點與應用前景

芯閱科技發布芯片級水質傳感器

行業首個芯片級游戲技術,OPPO「風馳游戲內核」正式亮相一加游戲大會

一加將首發芯片級游戲技術 帶來極致手游體驗

瑞沃微:一文詳解CSP(Chip Scale Package)芯片級封裝工藝

SOC芯片設計的挑戰與解決方案

龍芯中科“基于國產芯片級密碼安全的新一代信創云解決方案”入選2023年工信部信創典型案例

早期階段芯片級物理驗證同步 SoC 設計方案解析

早期階段芯片級物理驗證同步 SoC 設計方案解析

評論