深反應離子刻蝕工藝,是實現高深寬比特性的重要方式,已成為微加工技術的基石。這項刻蝕技術在眾多領域均得到了應用:1)MEMS電容式慣性傳感器;2) 宏觀設備的微型化;3) 三維集成電路堆疊技術的硅通孔工藝。

對于慣性MEMS傳感器,有研究發現制備的電容式加速度計具有高深寬比結構能夠顯著增加傳感面積,提供更高的驗證質量并降低彈簧剛度,從而提高電容靈敏度。在三維集成電路封裝領域,在單個基板上通過垂直互聯的多個芯片可以顯著提高設備性能降低尺寸,對于相同直徑的通孔結構,深寬比越大越有助于解決熱耗散和翹曲問題。 由于刻蝕結構的表面形貌與刻蝕區域的線寬大小有很大關系,微小線寬結構刻蝕隨著刻蝕深度的在增加,氣體傳輸受到一定程度的限制,缺乏活性氣體刻蝕導致能力減弱是制約小線寬高深寬比增大的主要因素。

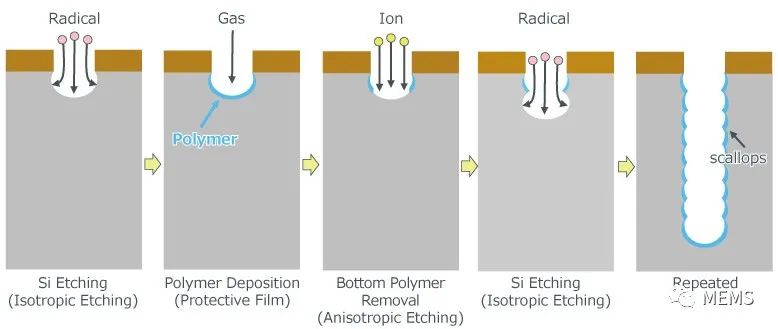

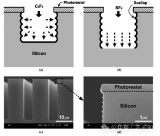

深反應離子刻蝕應用最普遍的是【Bosch工藝】,基于刻蝕和鈍化交替進行,將一個刻蝕循環分解為三個子過程:碳氟聚合物沉積、鈍化層刻蝕和硅的刻蝕,分別對應刻蝕菜單中Dep1,Etch1和Etch2。

為了改善刻蝕對深寬比的依賴性,在線圈功率和腔室壓力不改變的情況下,逐漸增大Etch2子過程刻蝕時間,以及Etch1和Etch2兩個刻蝕子過程中的極板功率,一方面增加反應氣體,并為反應氣體擴散和反應產物脫離提供了更多時間,另一方面提高極板功率能夠提高等離子體的垂直角度和入射能量,加強等離子體垂直轟擊能力,從而改善深溝槽底部的刻蝕情況。另一方面如果出現隨著刻蝕深度增加開口尺寸增大,表明當前側壁鈍化層厚度不足以保護側向不被刻蝕,需要增加Dep1或者減小Etch1。

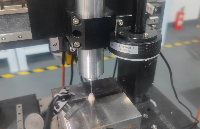

通過對工藝參數的優化,得到了下圖為2μm線寬刻蝕深度80微米,深寬比達40:1。

除了超高深寬比溝槽結構,下圖展示了微柱陣列、SOI器件、齒輪、彈簧等硅基刻蝕樣品,更多工藝展示,繼續關注勵德微系統。

更多深硅刻蝕樣品

-

刻蝕工藝

+關注

關注

2文章

40瀏覽量

8577

原文標題:高精度深硅刻蝕如何實現?答案在這里!

文章出處:【微信號:MEMSensor,微信公眾號:MEMS】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

【轉帖】干法刻蝕的優點和過程

請問如何實現高精度熱電阻測量電路的設計?

高精度溫度控制的實現

晶體硅太陽能電池刻蝕的作用及方法與刻蝕的工藝流程等介紹

激光掃描裝配間隙尺寸高精度檢測系統的設計與實現

實現高精度深硅刻蝕的方法

實現高精度深硅刻蝕的方法

評論