作者: DEAN BANERJEE,MOHAN RUDRAPPA,UDAY MEDA和AJEET PAL,德州儀器(TI)

在大多數鎖相環(PLL)合成器應用中,相位噪聲是一個關鍵參數。例如,在雷達中,低偏移頻率的相位噪聲轉化為辨別彼此靠近的兩個物體的能力。數據轉換器時鐘應用還需要低相位噪聲,以實現低信噪比。對于接收器,相位噪聲有助于檢測微弱的信號。對于測試設備,相位噪聲有助于測量較低噪聲的信號。

領先于性能的應用程序將需要更好的相位噪聲,即使它會轉化為更多的組件和復雜性。改善相位噪聲的一些嘗試包括使用帶乘法器的固定頻率源和使用窄帶壓控振蕩器(VCO),但要以降低頻率覆蓋范圍和下變頻VCO頻率為代價。在本文中,我們將討論下變頻PLL的VCO頻率的方法,并將該方法的仿真結果與實際測量結果進行比較。

PLL理論基礎

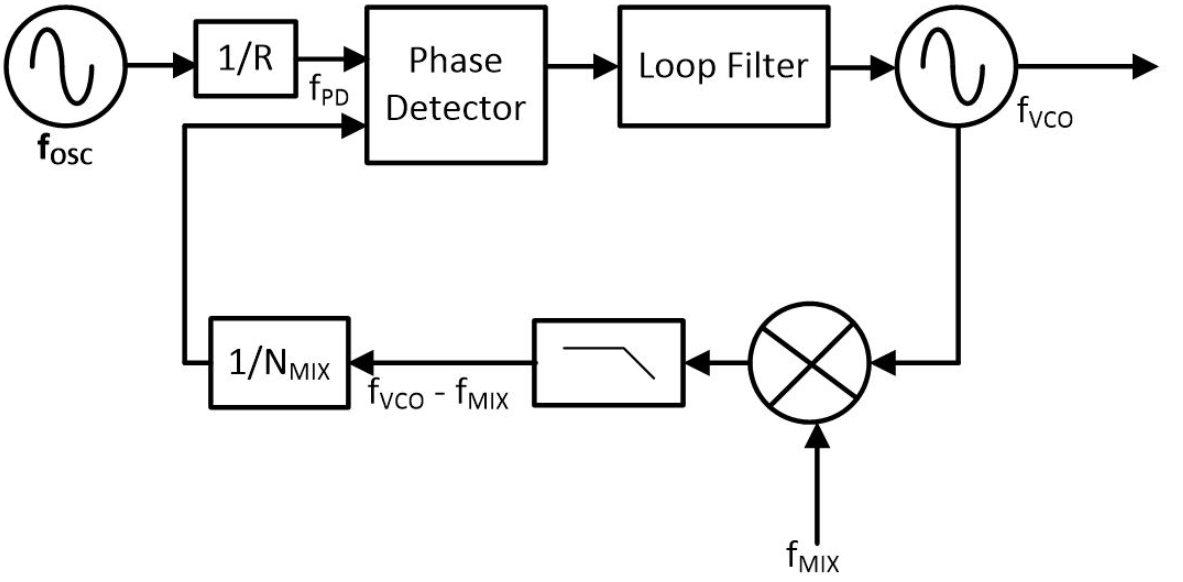

在解釋如何下變頻信號之前,讓我們回顧一下PLL理論的一些基礎知識。可以使用PLL從穩定源產生一定范圍的頻率。圖1顯示了PLL的傳統架構。

圖1該框圖顯示了傳統的PLL架構。資料來源:德州儀器(Texas Instruments)

PLL中的相位噪聲會嚴重影響指標,例如接收機靈敏度,誤碼率和信噪比。影響相位噪聲的一個關鍵參數是通過公式1計算得出的反饋分頻器值N。

VCO頻率fVCO除以鑒相器頻率fPD會產生N,它乘以PLL的分頻器和電荷泵。如果可以減小該值,則還可以降低噪聲性能。從理論上講,可以在不增加fPD的情況下將N減小2倍,從而將相位噪聲提高到6 dB。如果通過將fPD加倍將N減小2倍,則PLL 1 / f噪聲不會提高,但是PLL噪聲會提高到3 dB。無論哪種情況,減少N對相位噪聲都是有益的。

但是,很少有因素會限制您減少N的程度:

fPD的最大值受到限制;限制fPD的一件事是輸入頻率fOSC。通常,除非存在乘數,否則fPD不能大于fOSC。許多設備具有一個非常有用的x2乘法器,但是大于該值的分頻器通常會比低N所實現的改進增加更多的噪聲。除了受fOSC限制之外,最大fPD通常限于幾百兆赫茲由于電荷泵的架構。

N的最小值可以被限制。對于更高頻率的PLL,N被設計為在非常高的頻率下運行,這需要可以對最小N施加限制的預分頻器。此外,如果N支持小數,則該小數電路可以對N施加其他限制。

下變頻以獲得更好的相位噪聲

圖2顯示了一種方法,該方法可以通過添加穩定且非常低的噪聲頻率fMIX來降低N而又不增加fPD。

圖2下變頻架構可以幫助實現更好的噪聲相位。資料來源:德州儀器(Texas Instruments)

公式2將減少的N表示為:

公式3顯示了此架構在環路帶寬內的理論PLL相位噪聲改善:

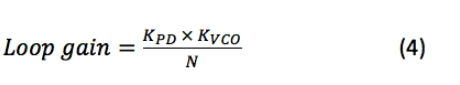

環路增益常數將影響環路動態,如公式4所示:

當環路增益發生顯著變化時,環路帶寬也將發生變化,從而導致不穩定或更大的環路帶寬(具有很高的峰值)。調整電荷泵增益KPD會使環路增益保持相對恒定,就像重新設計環路濾波器一樣。

圖3顯示了理論分析,其中忽略了混頻器和用于混頻的本地振蕩器的噪聲以及PLL的任何實際限制。本示例中的默認曲線適用于LMX2820寬帶射頻合成器。該器件具有200 MHz的fPD和9 GHz的輸出頻率,因此N為45。從理論上講,增加的FPD曲線用于將fPD增加到9 GHz。

圖3理論分析顯示PLL N從45降低到1。來源:德州儀器(Texas Instruments)

下變頻曲線顯示了使用圖2所示的架構將9 GHz輸出與無噪聲8.8 GHz輸出混頻器混頻至0.2 GHz時的理論相位噪聲。對于這些仿真,重新設計環路濾波器可保持類似的效果。環路帶寬。

當fPD增加45倍時,PLL噪聲平穩性提高,而PLL 1 / f噪聲卻沒有。相位噪聲仍然是一個很好的改善,但是當輸出進行下變頻時,相位噪聲性能會大大提高。

默認設置下的相位噪聲測量

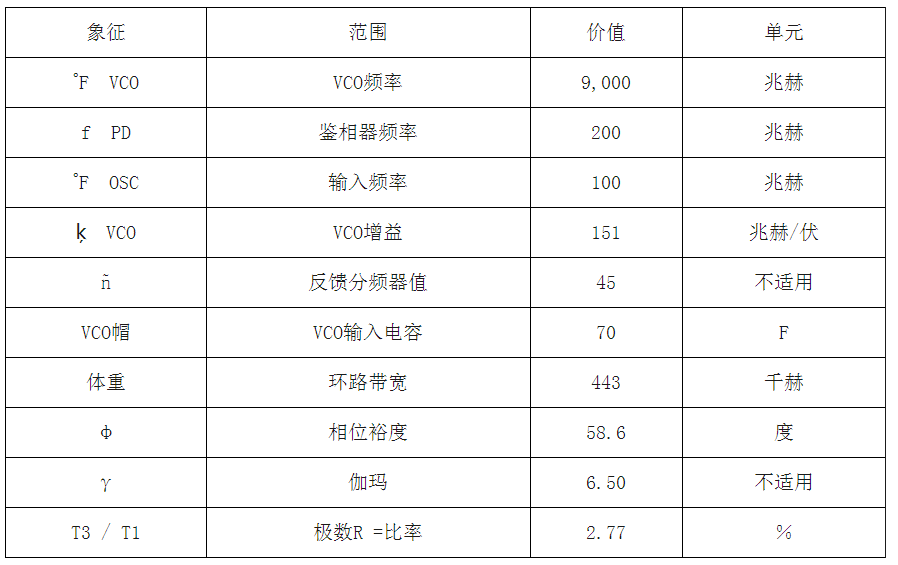

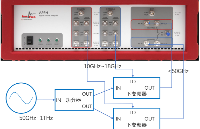

對下變頻的理論分析顯示出令人鼓舞的結果,但是有必要通過實際測量來證明這一點。因此,在基于LMX2820的評估板的測試中使用了圖3中的結果,條件如圖4和表1所示。

圖4設計示例顯示了傳統的PLL設置。資料來源:德州儀器(Texas Instruments)

表1播種了環路濾波器參數以進行實際測量。資料來源:德州儀器(Texas Instruments)

我們將來自100 MHz振蕩器的相位噪聲添加到仿真中。圖5比較了測量值和模擬值。盡管模擬中的遙遠相位噪聲似乎略有偏離,但近距離相位噪聲顯示出接近的一致性,這表明即使經過1 MHz的偏移,PLL噪聲仍在環路帶寬內的相位噪聲中占主導地位。

圖5圖形表示形式比較了測量值和模擬值。資料來源:德州儀器(Texas Instruments)

由于PLL噪聲主導著近相噪聲,因此通過減小N來改善PLL噪聲有很多潛在的好處。在這種特殊情況下,已經使用x2輸入乘法器將fPD最大化至200 MHz。盡管LMX2820芯片確實具有更高的輸入倍增器值,但使用這些更高的倍增器會增加噪聲,而噪聲的減小幅度要比減小的N值大。因此,在這種情況下,x2輸入乘法器是最佳選擇。

通過下變頻測量相位噪聲

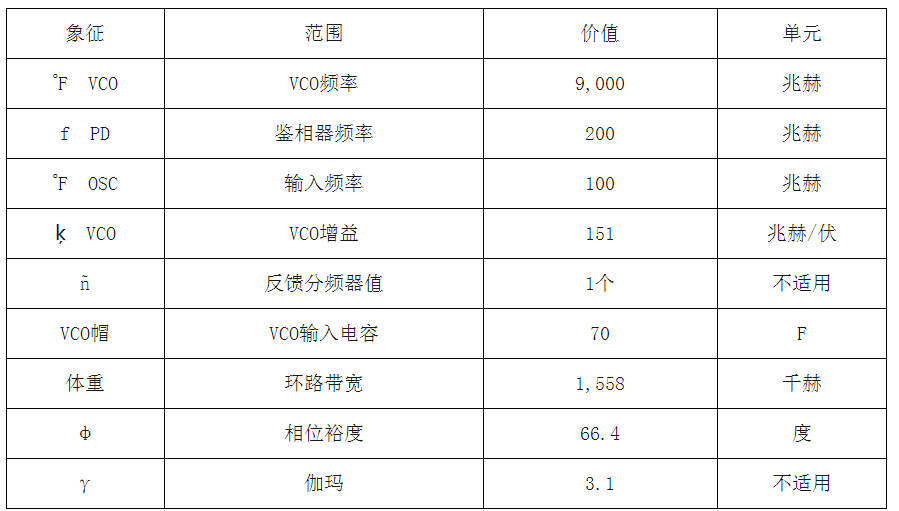

在使fPD最大化的情況下,改善相位噪聲的另一種方法是通過下變頻降低N。此設計任務需要干凈的信號源(通常是固定頻率的晶體或該晶體的倍頻版本)。但是,對于此設置,為方便起見,我們使用了信號發生器。圖6和表2顯示了設置條件。

圖6這是下變頻器架構設置的外觀。資料來源:德州儀器(Texas Instruments)

表2顯示了下變頻架構的環路濾波器參數。資料來源:德州儀器(Texas Instruments)

圖7顯示了從LMX2820芯片獲得的測量結果和仿真,該芯片具有用于下變頻頻率的獨立輸入引腳。出于仿真目的,從整個噪聲分布圖中減去38.9 dB,將本地振蕩器(在這種情況下為信號發生器)的相位噪聲從8.8 GHz降低至100 MHz。如果混頻器具有明顯的噪聲分布,則可以用相同的方法將其縮小。在這種情況下,無源混頻器的噪聲遠低于系統中的其他噪聲源。

圖7從寬帶射頻合成器設備獲得的測量結果和仿真。資料來源:德州儀器(Texas Instruments)

我們針對LMX2820器件進行了其他調整。在此器件上使用外部混頻器輸入引腳需要使用單相頻率檢測器模式,這有效地使電荷泵增益減半,并使PLL的品質因數降低3 dB。我們將此數字作為模擬因素。

正如公式3所預測的,相位噪聲的好處不是20log(45)= 33-dB的好處。無法獲得全部理論收益的原因是它受到混頻器本地振蕩器噪聲的限制。通過使用較干凈的本地振蕩源,可以大幅降低相位噪聲。無論如何,如圖8所示,相位噪聲的改善仍然很大。

圖8對于下變頻架構,相位噪聲的改善仍然很大。資料來源:德州儀器(Texas Instruments)

下轉換方法和刺激

除了改善相位噪聲外,下變頻理論上還可以改善雜散。通過下變頻,工程師可以使用混合頻率使fVCO偏離fOSC的近整數倍,從而改善整數邊界雜散。此外,通過減少N,理論上電荷泵的整數PLL雜散將減少20log(N)。

馬刺很復雜,有多種原因,因此很難不經過測試就知道馬刺的全部收益。但是,如果使用正確的方式,則降頻轉換方法理論上可以改善某些雜訊。

編輯:hfy

-

振蕩器

+關注

關注

28文章

3858瀏覽量

139494 -

分頻器

+關注

關注

43文章

448瀏覽量

50130 -

電荷泵

+關注

關注

3文章

239瀏覽量

29697

發布評論請先 登錄

相關推薦

相位噪聲分析儀的技術原理和應用

LMX2595 EVM說明–具有集成VCO的20GHz寬帶低噪聲PLL

通過變頻PLL的VCO頻率仿真測量獲得更好的相位噪聲

通過變頻PLL的VCO頻率仿真測量獲得更好的相位噪聲

評論