版權聲明:本文為博主原創文章,遵循 CC 4.0 BY-SA 版權協議,轉載請附上原文出處鏈接和本聲明。

本文鏈接:https://blog.csdn.net/yinyeyy/article/details/106422415

使用xdc文件進行管腳、位置、時序和屬性等約束的時候,經常會使用各種get命令。Vivado提供了很豐富的匹配表達式,比如等于==、不等于!=、匹配=~、不匹配!~、、=等等,這些表達式可以通過&&和||進行組合;同時還有大量的狀態、屬性和單元名稱可用,比如DIRECTION、IN、IS_LOC_FIXED、IS_PRIMITIVE、NAME等等。

我在xdc文件中匹配目標的時候,在可行的情況下更傾向于使用正則表達式。本文就介紹一下我常使用的正則表達式和一些在Vivado中應用的特殊之處,同時也有個別自己尚未解決的問題。

1. -hierarchical和-regexp的使用

在匹配FPGA內部資源時,比如get_pins、get_cells、get_nets的時候,需要同時使用-hierarchical和-regexp。

-hierarchical表示Vivado在匹配對象的時候,將在工程中不同的層次內對該信號進行搜索。如果沒有加這個選項,就必須在匹配字符中顯式且精確的指出匹配對象所在的層次。需要注意的是,當使用get_ports時,不能使用-hierarchical選項。因為ports應該位于頂層,沒有層次之分。

-regexp是指本次匹配將使用正則表達式,是必須使用的。

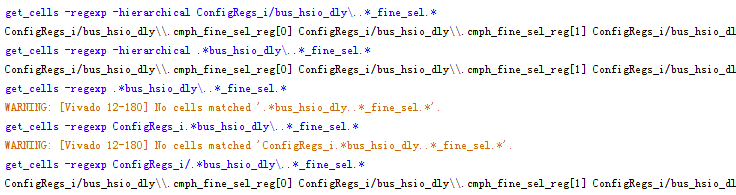

以下是一個使用-hierarchical的例子和注意事項。

首先看第一行藍色的get_cells命令,這里用來獲得ConfigRegs_i這個實例內的滿足bus_hsio_dly/。.*_fine_sel.*要求的對象。可以看到運行該命令后得到了下面黑色部分的對象。第三行指令在第一行的基礎上,把頂層實例ConfigRegs_i的限制去掉,也獲得了想要的對象。

再來看第五行的指令。此處去掉了-hierarchical,意味著匹配過程不能穿越不同的層次結構。同時“.*”雖然可以匹配任何除換行符之外的任何數量的字符,但是卻不能替代在Vivado中表示層次概念的“/”符號。所以匹配過程只在頂層進行搜索,其結果就如第六行,不能找到所需的對象。

第七行也犯了一樣的錯誤。在沒有使用-hierarchical的情況下,雖然想通過“ConfigRegs_i.*”來匹配頂層的ConfigRegs_i實例,但是“.*”是不能匹配層次符號“/”的。同樣無法獲取對象。

第九行雖然沒有使用-hierarchical,但是通過ConfigRegs_i/指定了對象的層次結構,是可以獲得想要的對象的。但是這里有一個限制,即cmph_fine_sel_reg[0]這些對象必須位于ConfigRegs_i下。如果cmph_fine_sel_reg[0]和ConfigRegs_i中間還隔了別的實例,比如ConfigRegs_i例化了CmpDef_i,CmpDef_i內部定義了cmph_fine_sel_reg[0]。這種情況下,第九行是無法找到所需對象的。

2. 常用的匹配方法

正則表達式功能強大且復雜,要完全掌握會花費很長時間。但是對于我們編寫xdc而言,只需要掌握很小一部分內容就可以應對絕大多數情況了。最常用的應該就是特殊字符和限定符了。下面是比較常用的特殊字符。

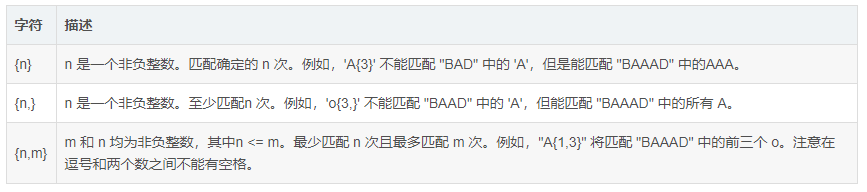

常用限定符如下。

我們在FPGA工程中使用正則表達式不是為了進行字符處理,不需要考慮太多的容錯性和可能性。對于我們而言,絕大多數命名都是確定的,使用正則是為了更方便的獲取對象和簡化匹配過程。

3. 使用示例

3.1 獲取總線類對象

看以下例子。在進行物理約束的時候,為一個總線設置信號類型,如果一個一個的寫即慢又可能犯錯。使用正則可以將這類信號全部提取出來。以一個從0到31共32路的總線為例。

set_property IOSTANDARD SSTL18_I_DCI [get_ports -regexp {c2c_sync/[.*]}]

以上指令可以獲取所有名字為c2c_sync[]的端口,方括號內可能是任意多個數字。這種寫法不夠準確,在文字處理程序里面會出大問題,但是在FPGA工程中足夠了。當然也可以寫的稍微嚴格點,比如:

set_property IOSTANDARD SSTL18_I_DCI [get_ports -regexp {c2c_sync/[[0-9]{1,2}]}]

這個表達式比上一個更進一步的約束了中括號內的內容。這里的/[是為了匹配“[”本身,而里面的[0-9]則定義了一個從數字0到數字9的字符集,[0-9]后面的{1,2}則表示[0-9]中的任意數字將出現1次,或以任意兩個數字的組合出現1次。對于我們的應用,做到這一步就夠了。

3.2 簡化匹配表達式

工程中會有一些名字很特殊的信號,比如全局復位信號,這種信號在工程中往往只會出現一次,我用更加簡單粗暴的方式來獲得。

set_false_path -from [get_cells -regexp -hierarchical .*rst_global_reg.*]

比如上面的例子。通過使用-hierarchical搜索所有層次,通過在rst_global_reg的前后都使用.*來匹配任何可能出現的字符。其中。表示匹配任何非換行符的字符,*表示。可以出現任意次。當然并不推薦這種寫法,因為會增加編譯時匹配對象的負擔。可以使用更精準的匹配。

對于層次很深的信號,只要保證列出的匹配字符能夠找到我們所要的對象即可。比如某工程有下圖的層次結構。

比如設計者發現A_i0模塊內部的D_i0內的某個關鍵信號的位置需要優化,且設計者知道該信號在D_i0中唯一。為了拿到這個關鍵信號,可以使用正則表達式,并且可以略過中間層次的所有模塊。

get_cells -regexp -hierarchical {A_i0/.*/D_i0/start_reg}

3.3 特殊字符的獲取

前面提到過一些特殊字符,比如?、。、/、[等等,如果需要匹配這些字符,需要用到轉義符“/”。比如“/。”表示“。”這個字符本身,而不再是匹配符。。

比如在上文提到的get_ports -regexp {c2c_sync/[[0-9]{1,2}]}。這個總線的完整名稱是c2c_sync[0]、c2c_sync[1]。..。..,此處的“/[”就是表示左方括號這個字符本身。而[0-9]中單獨使用的[]就表示一個字符集合。這里有個需要注意的地方,作為字符使用的左方括號左側加了轉義符“/“,而右方括號則不需要加”/“。

另外一個需要注意的是上文中提到的get_cells -regexp -hierarchical ConfigRegs_i/bus_hsio_dly.*_fine_sel.*。這里面bus_hsio_dly是一個systemverilog中的interface,獲取的對象是bus_hsio_dly接口中的cmph_fine_sel_reg信號,其表達方式應該是bus_hsio_dly.cmph_fine_sel_reg。此處我使用”.*“來匹配任何非換行字符,所以可以匹配”。“字符。

更合適一點的匹配表達式應該是ConfigRegs_i/bus_hsio_dly/。.*_fine_sel_reg。第一處修改是明確使用/。來匹配”。“,第二處修改時添加了_reg后綴(Vivado會給寄存器變量默認添加_reg后綴)。如果不添加該后綴,可能會獲取一些不期望的對象。比如使用get_cells時,可能或獲取帶_fine_sel的LUT,比如_fine_sel_i_1等等。

再進一步,我們可能注意到上述匹配獲得的對象打印出來是:

bus_hsio_dly//.cmph_fine_sel_reg

打印結果不是/。,而是//。。對于這種情況,我猜想是//用來表示轉義符”/“。而”//“表示的轉義符則作用于特殊字符”。“,用來表示普通字符”。“。

這是個人猜測,但是為什么會這樣?如果哪位清楚原因,不吝賜教。

審核編輯:何安

-

Vivado

+關注

關注

19文章

832瀏覽量

68358 -

xdc

+關注

關注

1文章

24瀏覽量

6027

發布評論請先 登錄

Cubeide1.18.1在線調試改變\"現場表達式\"中的值提示找不到地址,為什么?

干貨分享 | 零基礎上手!TSMaster圖形信號表達式實操指南

Cubeide1.18.1在線調試改變\"現場表達式\"中的值提示找不到地址,怎么解決?

Cubeide1.18.1在線調試改變\"現場表達式\"中的值提示找不到地址怎么解決?

Linux中文本處理命令的用法

Linux grep命令詳解

Verilog表達式的位寬確定規則

TestStand表達式中常用的語法規則和運算符使用

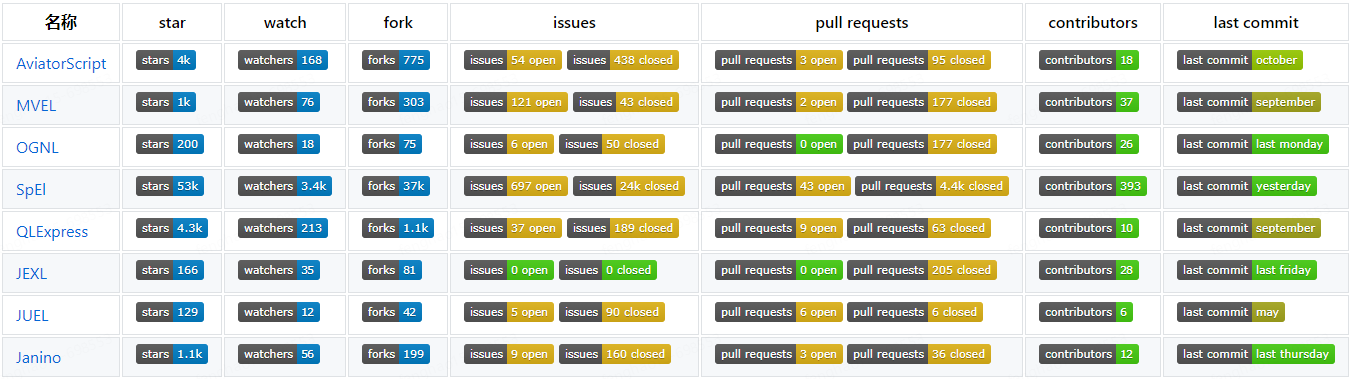

Java表達式引擎選型調研分析

正則表達式在Vivado約束文件中的應用

正則表達式在Vivado約束文件中的應用

評論