近日,西安紫光國芯半導體有限公司(以下簡稱“紫光國芯”)在第63屆國際電子器件大會(IEDM 2020)上公開發表了技術論文——《采用3D混合鍵合技術具有34GB/s/1Gb帶寬和0.88pJ/b能效接口的異質集成嵌入式LPDDR4/LPDDR4X DRAM》(A Stacked Embedded DRAM Array for LPDDR4/4Xusing Hybrid Bonding 3D Integration with 34GB/s/1Gb 0.88pJ/b Logic-to-MemoryInterface)。該論文的發表,是紫光國芯在超高帶寬、超低功耗DRAM方向技術積累和持續創新的最新突破。

受限于傳統計算機體系的馮-諾依曼架構,存儲器帶寬與計算需求之間的鴻溝(即“存儲墻”問題)日益突出。采用硅通孔(TSV)技術的高帶寬存儲器(HBM)是業界給出的一個可選解決方案,但其每數據管腳的工作頻率仍然較高(約4Gbps),存在功耗較大的缺點。比如HBM采用了x10um級微凸塊(Micro-Bump)堆疊DRAM,其數據IO數量有限且寄生電容和功耗較大,進而限制了帶寬的增加。 西安紫光國芯依托多年對存儲器和ASIC體系結構的深入研究,開發完成了異質集成嵌入式DRAM平臺(SeDRAM),提供了業界最高的單位帶寬和能效,并設計實現了完全兼容國際JEDEC標準的的4Gbit LPDDR4芯片。

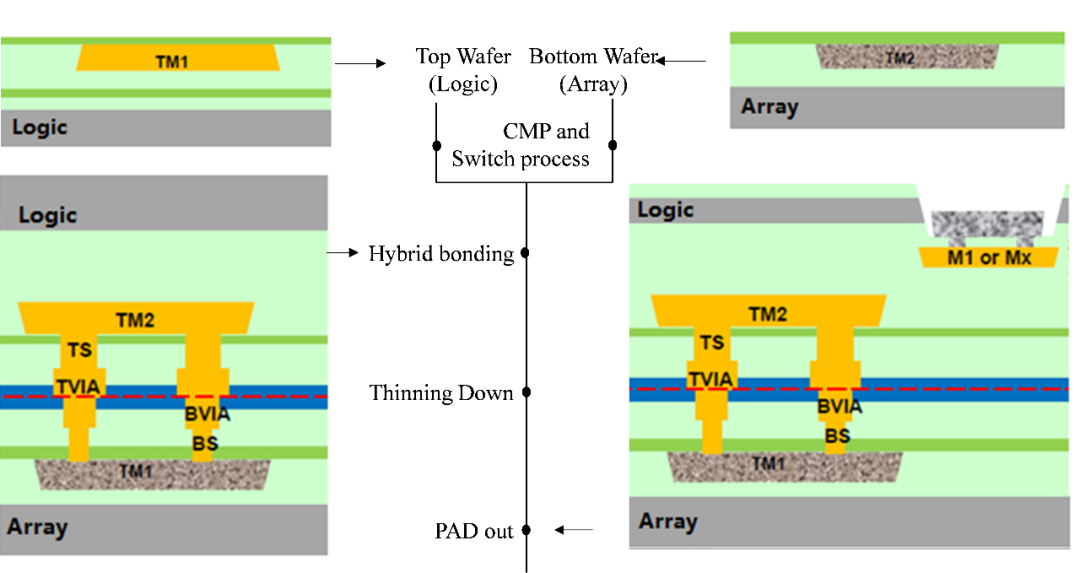

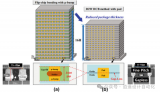

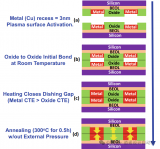

圖1. SeDRAM技術流程示意圖 紫光國芯在論文中介紹了SeDRAM平臺的實現流程(如圖1):首先,流片生產不同工藝下的DRAM存儲晶圓(DRAM Wafer)和搭載有外圍電路的邏輯晶圓(Logic Wafer),并通過平坦化、曝光和刻蝕等異質集成工藝,在兩張晶圓上分別制成用于后續步驟的接觸孔(LTVIA和LBVIA);然后,將邏輯晶圓翻轉,通過 Cu-Cu 互連的方式,將兩張晶圓直接鍵合;最后,將邏輯晶圓減薄至約3um厚度,并從邏輯晶圓背面開口完成PAD制作。 相比于HBM的微凸塊(MicroBump)工藝,通過直接鍵合方式的異質集成工藝,接觸孔可達110,000個/mm2,實現了百倍量級的密度提升,而且連接電阻低至0.5歐姆。從而實現了從邏輯電路到存儲陣列之間每Gbit高達34GB/s的帶寬和0.88pJ/bit的能效。

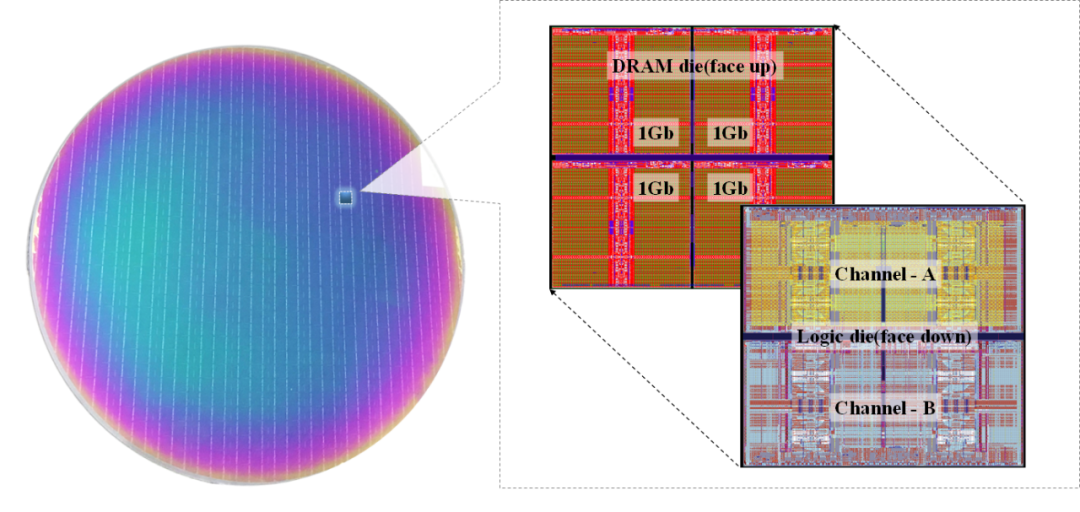

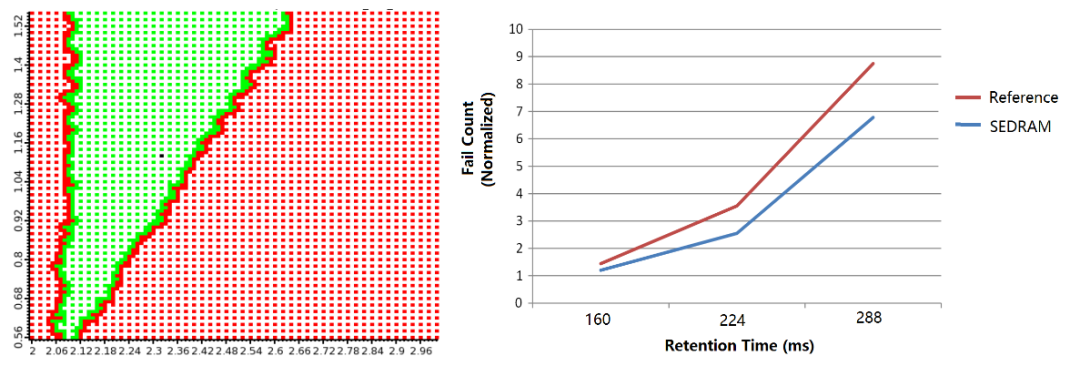

圖2. 采用SeDRAM技術開發的4Gb LPDDR4產品的晶圓(左)和版圖(右) 紫光國芯開發的4Gbit LPDDR4是業內首款異質集成的標準接口DRAM產品(如圖2)。該產品為雙通道,數據位寬X16,在每顆芯片中集成超過64,000個異質集成接觸孔。在晶圓測試階段,該產品表現出優異性能,讀取時間超過測試機臺能支持的最快時鐘周期0.56ns。在顆粒測試階段,該產品在包括高溫(95℃),高壓(VDD2=1.2v, VDD1=2v)以及低壓(VDD2=1.05v, VDD1=1.65v)在內的多個測試條件下,通過了業界最高水平4266Mbps數據率的測試。該產品在高溫測試條件下,保持時間達到96ms,與同等DRAM工藝下的傳統平面產品相比更具優勢。

圖3. 4Gb LPDDR4產品的讀取時間測試結果(左)和數據保持時間測試結果(右) 感謝武漢新芯和臺灣力積電分別支持邏輯芯片及異質集成、和存儲芯片代工合作,論文得以在IEDM 2020順利發表,這是紫光國芯在超高帶寬、超低功耗DRAM方向技術積累和持續創新的最新突破。通過4Gbit LPDDR4產品的開發,SeDRAM平臺不僅為傳統DRAM產品的開發提供了新路徑,更為人工智能(AI)和高性能計算(HPC)等領域的高帶寬、高能效需求提供了有效解決方案。

原文標題:西安紫光國芯在IEDM 2020發表 異質集成嵌入式DRAM(SeDRAM)論文

文章出處:【微信公眾號:西安紫光國芯半導體】歡迎添加關注!文章轉載請注明出處。

責任編輯:haq

-

嵌入式

+關注

關注

5148文章

19651瀏覽量

317113 -

DRAM

+關注

關注

40文章

2348瀏覽量

185536 -

存儲器

+關注

關注

38文章

7648瀏覽量

167210 -

紫光

+關注

關注

2文章

420瀏覽量

34485

原文標題:西安紫光國芯在IEDM 2020發表 異質集成嵌入式DRAM(SeDRAM)論文

文章出處:【微信號:gh_fb990360bfee,微信公眾號:西安紫光國芯半導體】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

從微米到納米,銅-銅混合鍵合重塑3D封裝技術格局

貞光科技代理紫光國芯存儲芯片(DRAM),讓國產替代更簡單

混合鍵合市場空間巨大,這些設備有機會迎來爆發

閃存沖擊400層+,混合鍵合技術傳來消息

紫光國芯:采用3D混合鍵合技術的異質集成嵌入式DRAM

紫光國芯:采用3D混合鍵合技術的異質集成嵌入式DRAM

評論