《前言》

最近在Modelsim仿真過程中,遇到一個大問題,對于分辨率2048*500的圖像數據,在進行時序約束中,發現算法模塊最高只能跑到60Mhz多,而要求必須跑到100Mhz,因而時序不滿足要求;通過看時序報告,關鍵路徑基本上都是在reg to mem和mem to reg path上,嘗試修改對邏輯處理影響較大。

如何在不修改核心算法邏輯的前提下,保證功能和時序滿足,辦法還是有的,后來發現100Mhz頻率下算法模塊輸入的數據有效帶寬只有50% ,因此考慮算法模塊入口處增加一個整形的異步FIFO,寫時鐘100Mhz,讀時鐘50Mhz這樣算法模塊只工作在50Mhz時鐘頻率下,可以滿足時序要求。同時也滿足100Mhz接口時序的要求。

此時,增加一個時鐘ip核來得到50Mhz,發現仿真速度極其慢,由原來的1~2分鐘左右變為現在的1小時左右,定位個問題,效率太低了。

《如何加速Modelsim仿真時間》

首先,需要說明的是,Modelsim仿真時間長短,也有電腦配置有關,i7+16G的配置其實也就10分鐘左右 ,i5+8G的配置就是1小時多。

其次,就是在仿真平臺上下功夫:

方法一:修改代碼仿真精度,精度越高,Modelsim效率越低。1n/1ps 修改為 1n/1ns 速度可提升一倍。

方法二:減少層次結構,減少波形信號的顯示。特別是輸出的數據文件,能減少就減少。

方法三:在不影響功能的前提下,降低測試的圖像分辨率,或者一些計數器適當縮短計數,都可以達到提速的目的。

方法四:當文件仿真系統有大量文件時,修改某個Module的信號,增量編譯可以節省時間,verilog :vlog -incr vhdl:vcom -incr

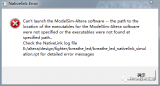

方法五:減少IP的調用,比如我的這個慢的主要原因就是調用時鐘IP的原因;這里兩個時鐘都可以在testbench 生成,大大減少了仿真時間,又回到了幾分鐘。

原文標題:Modelsim加速仿真技巧

文章出處:【微信公眾號:FPGA之家】歡迎添加關注!文章轉載請注明出處。

責任編輯:haq

-

仿真

+關注

關注

51文章

4245瀏覽量

135381 -

ModelSim

+關注

關注

5文章

174瀏覽量

47961

原文標題:Modelsim加速仿真技巧

文章出處:【微信號:zhuyandz,微信公眾號:FPGA之家】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

輪邊電機驅動汽車性能仿真與控制方法的研究

【Simcenter Flotherm】憑借快速準確的電子冷卻CFD仿真功能,有效提升電子熱管理的穩定性

技術分享 | AVM合成數據仿真驗證方案

【紫光同創盤古100Pro+開發板,MES2L676-100HP教程】盤古676系列——Modelsim的使用和do文件編寫

【Simcenter STAR-CCM+】通過快速準確的CFD仿真加速空氣動力學創新

使用LIS2DW12TR加速度傳感器可以計算物體重力方向運動的距離嗎

Simcenter Flomaster熱流體仿真軟件

這些電源常用仿真軟件,你都知道嗎?

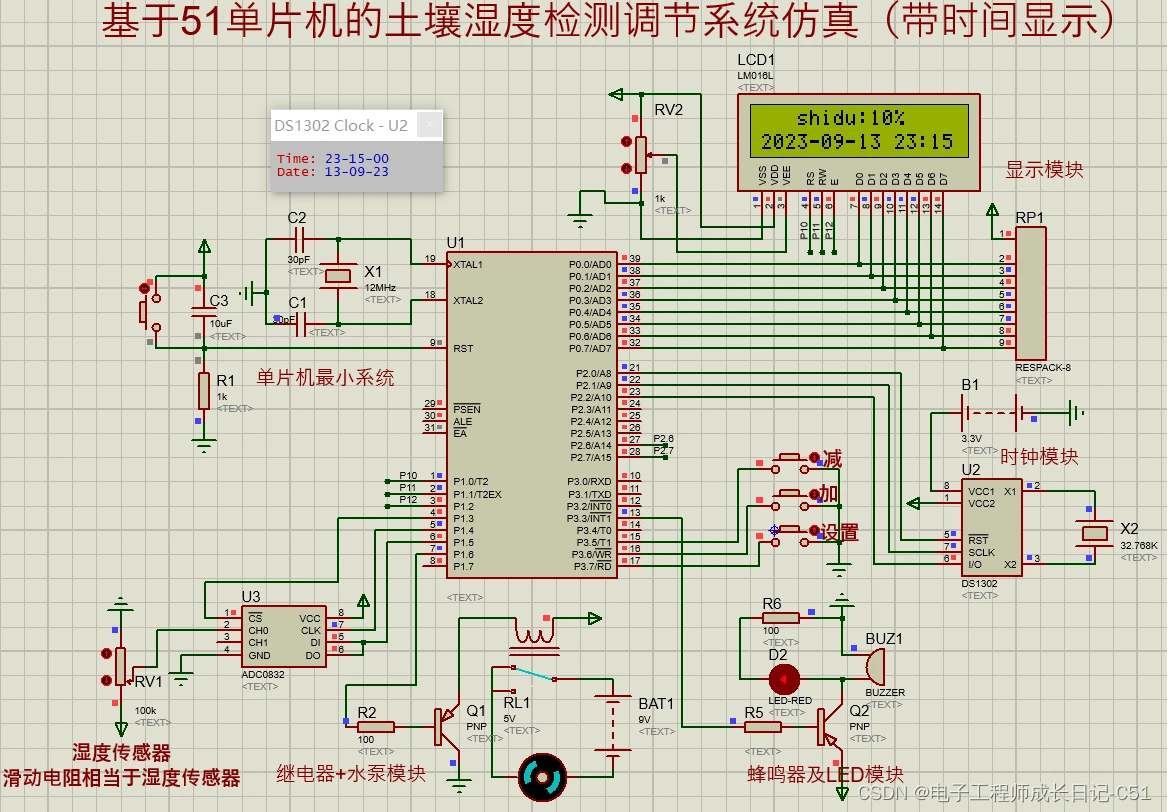

基于51單片機的土壤濕度檢測調節系統仿真(帶時間顯示)

Efinity FIFO IP仿真問題 -v1

如何加速Modelsim仿真時間?

如何加速Modelsim仿真時間?

評論