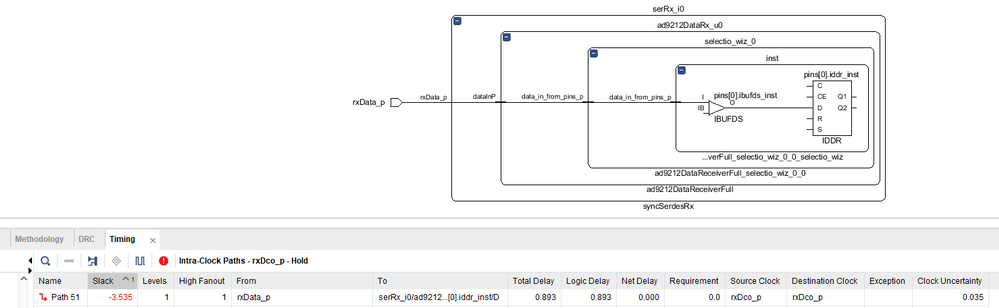

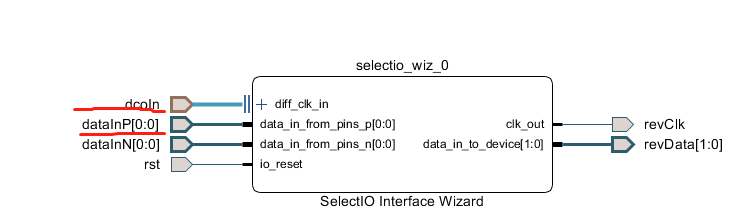

Q: 使用 zynq 器件, select io 解碼串行數據, data 和 clock 直接進入, 未進行其他處理, 綜合有關于 data 保存時間的時序錯誤, 請問什么問題? 實測接收功能基本正確

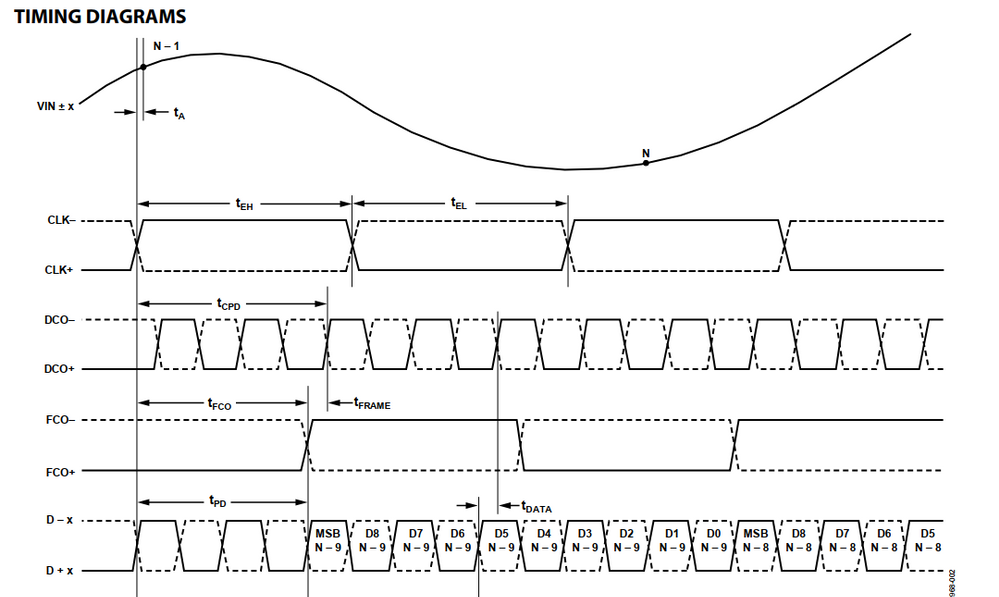

器件時序, 約束采用的是其中的 tframe = 1.3 - 1.9ns

約束:

set_input_delay -clock [get_clocks rxDco_p] -clock_fall -min -add_delay -1.300 [get_ports rxData_n]

set_input_delay -clock [get_clocks rxDco_p] -clock_fall -max -add_delay -1.900 [get_ports rxData_n]

set_input_delay -clock [get_clocks rxDco_p] -min -add_delay -1.300 [get_ports rxData_n]

set_input_delay -clock [get_clocks rxDco_p] -max -add_delay -1.900 [get_ports rxData_n]

set_input_delay -clock [get_clocks rxDco_p] -clock_fall -min -add_delay -1.300 [get_ports rxData_p]

set_input_delay -clock [get_clocks rxDco_p] -clock_fall -max -add_delay -1.900 [get_ports rxData_p]

set_input_delay -clock [get_clocks rxDco_p] -min -add_delay -1.300 [get_ports rxData_p]

set_input_delay -clock [get_clocks rxDco_p] -max -add_delay -1.900 [get_ports rxData_p]

A: 應該是 set_input_delay 約束寫錯了

參考 vivado language template 的話,這個 data 接口符合 source synchronous--》 center aligned --》 DDR 的模板

其中參數

dv_bre = dv_bfe = 1.3ns

dv_are = dv_afe = (1/2 period - 1.9)ns

所以約束里的

-max 值是(1/2 period - 1.3)

-min 值是(1/2 period - 1.9)

Language template在 vivado 圖形界面 tools 菜單里。

關于 template 的介紹,可以先學習 inputdelay/output delay 的理論基礎,結合實踐琢磨一下,這套 template 使用的方法還是有點巧妙的

經驗是通過時序圖對比,找到最匹配的 template,確定里面對應參數的值,套用 template里面的約束模板就可以。

可以找出這個 source synchronous --》 centeraligned --》 DDR 模板,看里面的時序圖跟用戶手冊里的時序圖對比下

時序圖里沒有畫出 data 有效數據跟無效數據(就是陰影部分)的范圍,但 tFRAME 的值之所以是 1.3~1.9,就是因為 data 有有效數據跟無效數據范圍的原因,把時序圖的有效數據和無效數據范圍畫出來,就容易跟 template 里的時序圖進行匹配了。

原文標題:本周一問 | Select io 解串行數據, 時序約束不通過問題

文章出處:【微信公眾號:XILINX技術社區】歡迎添加關注!文章轉載請注明出處。

責任編輯:haq

-

數據

+關注

關注

8文章

7246瀏覽量

91163 -

時序設計

+關注

關注

0文章

21瀏覽量

44006

原文標題:本周一問 | Select io 解串行數據, 時序約束不通過問題

文章出處:【微信號:gh_2d1c7e2d540e,微信公眾號:XILINX開發者社區】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

如何將dif_time打印到 uart 或將其保存在文件中?

一文詳解Vivado時序約束

AXI握手時序優化—pipeline緩沖器

怎么解決有關于data保存時間的時序錯誤?

怎么解決有關于data保存時間的時序錯誤?

評論