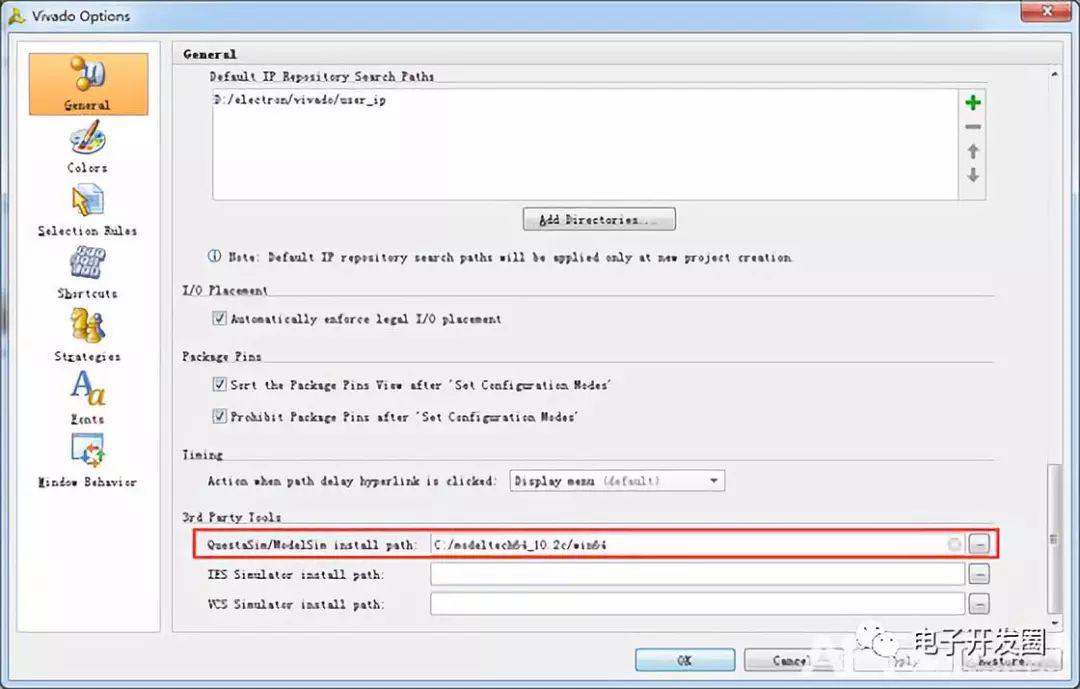

一、在vivado中設置modelsim(即第三方仿真工具)的安裝路徑。在vivado菜單中選擇“Tools”——》“Options.。。”,選擇“General”選項卡,將滾動條拉倒最底部,在“QuestaSim/ModelSim install path”欄中輸入或選擇modelsim工具的安裝路徑,如圖1所示。

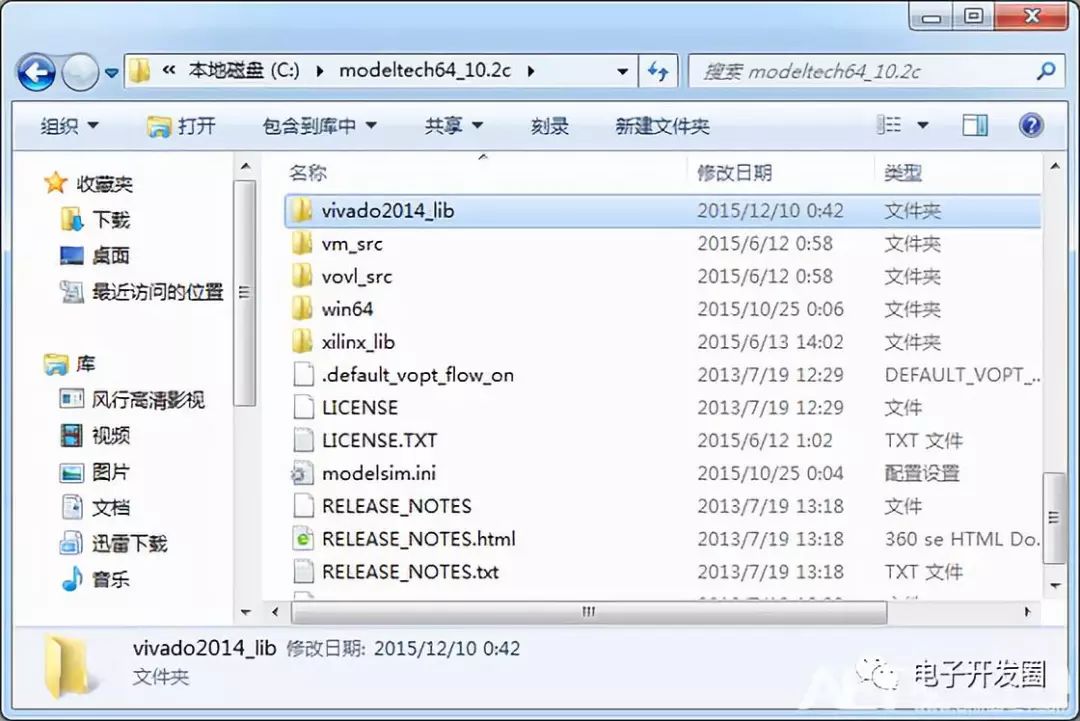

圖1 設置modelsim的安裝路徑 二、器件庫編譯。首先,在modelsim安裝路徑中新建一個名為vivado2014_lib的文件夾(路徑和文件名可改),如圖2所示。

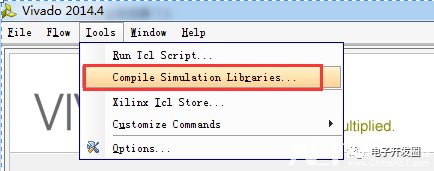

圖2 在modelsim安裝路徑下新建vivado2014_lib文件夾 接著選擇vivado菜單“Tools”——》“Compile Simulation Libraries.。。”命令,如圖3所示。

圖3 選擇“Compile Simulation Libraries.。。”命令

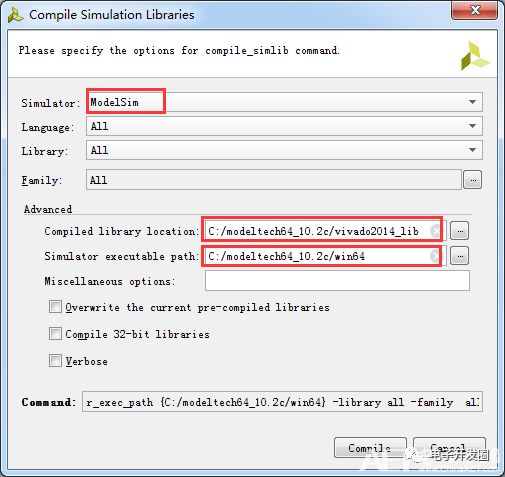

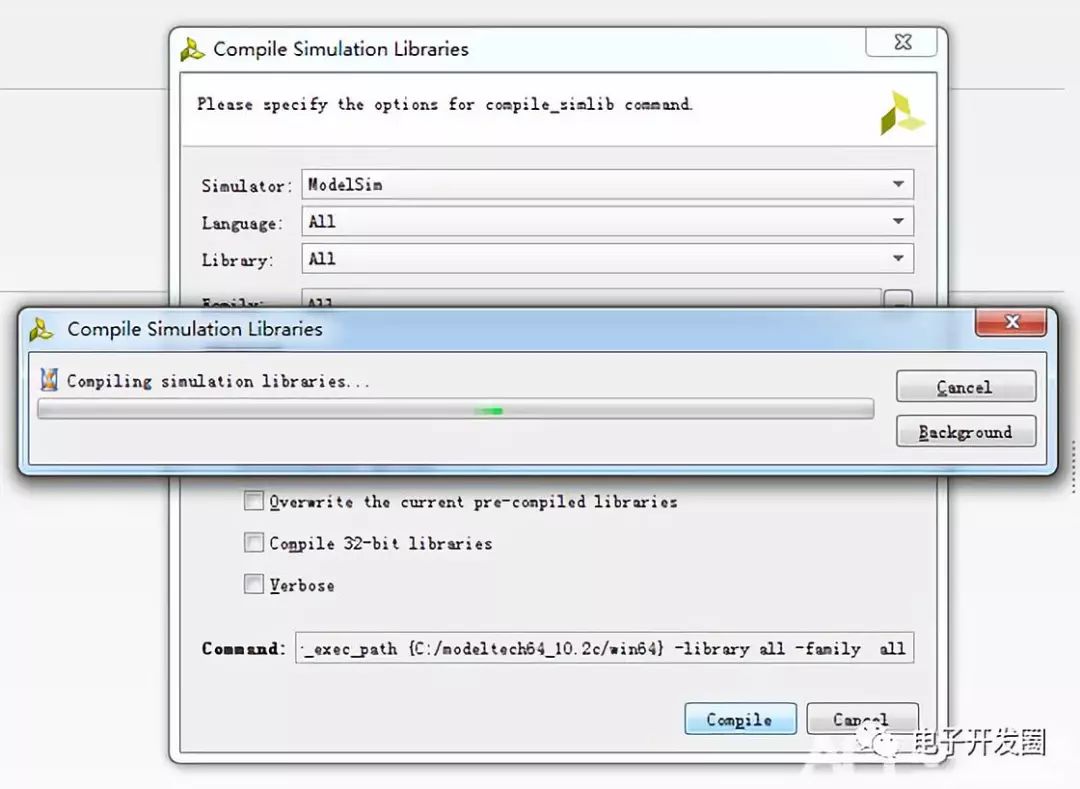

在彈出的對話框中設置器件庫編譯參數,仿真工具“Simulator”選為ModelSim,語言“Language”、庫“Library”、器件家族“Family”都為默認設置All(當然也可以根據自己的需求進行設置),然后在“Compiled library location”欄設置編譯器件庫的路徑,這里選前面新建的vivado2014_lib文件夾,此外在“Simulator executable path”欄設置modelsim執行文件的路徑,其他參數默認,如圖4所示。

圖4 設置器件庫編譯參數

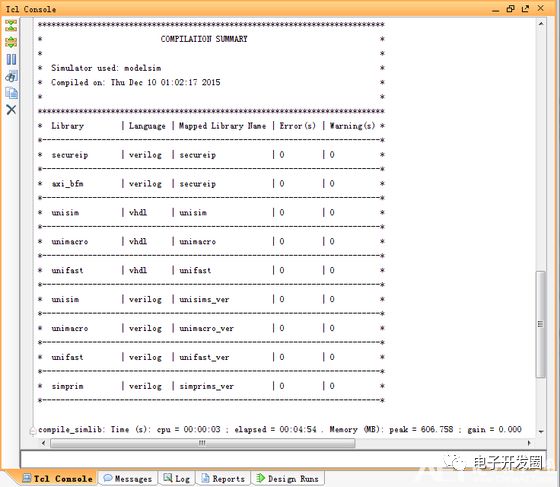

設置好參數后點擊“Compile”按鈕開始器件庫的編譯。圖5所示為正在編譯器件庫的過程中。器件庫編譯結束后給出編譯報告,從報告中看出0個警告和0個錯誤,如圖6所示。

圖5 正在編譯器件庫的過程中

圖6 器件庫

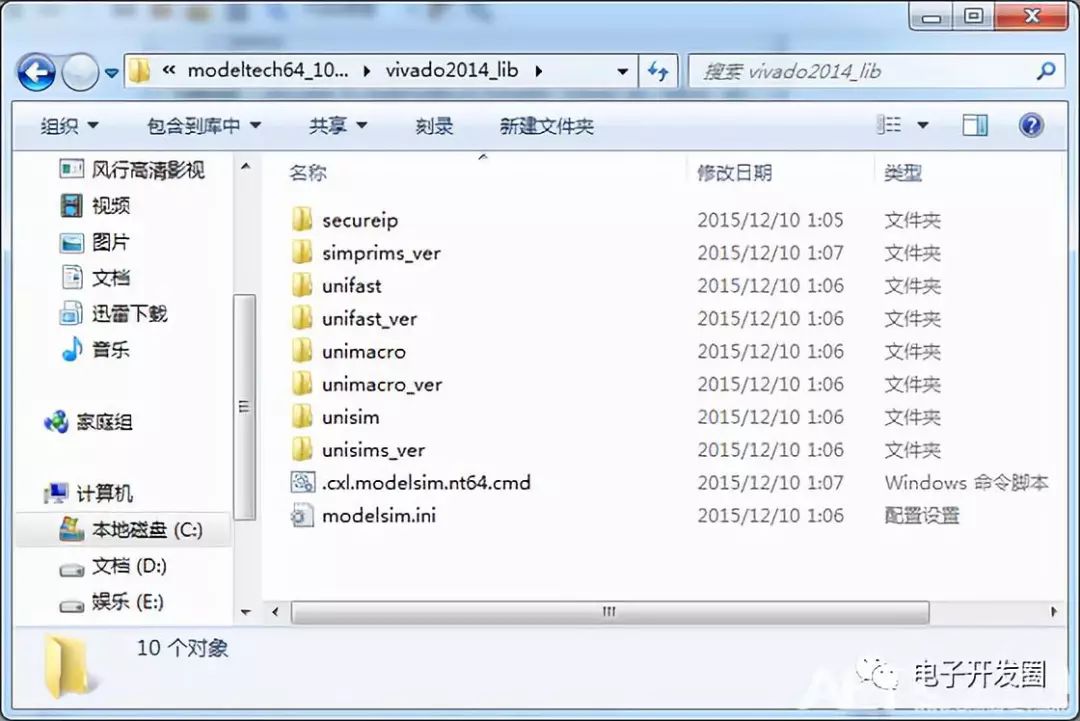

編譯結束后產生編譯報告 打開modelsim安裝路徑下的vivado2014_lib文件夾,便可以看到已經產生了器件庫,如圖7所示。

圖7 已在vivado2014_lib文件夾中生成器件庫

三、在vivado中關聯了modelsim軟件和編譯器件庫之后,就可以在vivado中調用modelsim軟件對設計進行仿真了。

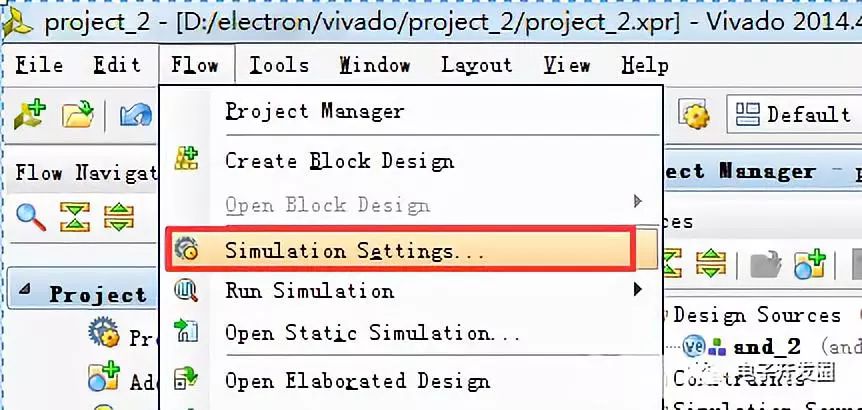

不過,在對每一個新建的工程設計進行仿真時需要進行一些設置。選擇vivado菜單“Flow”——》“Simulation Settings.。。”命令或點擊流程向導中選擇“Simulation Settings.。。”命令,分別如圖8和圖9所示。

圖8 從菜單選擇“Simulation Settings.。。”命令

圖9 從流程向導中選擇“Simulation Settings.。。”命令

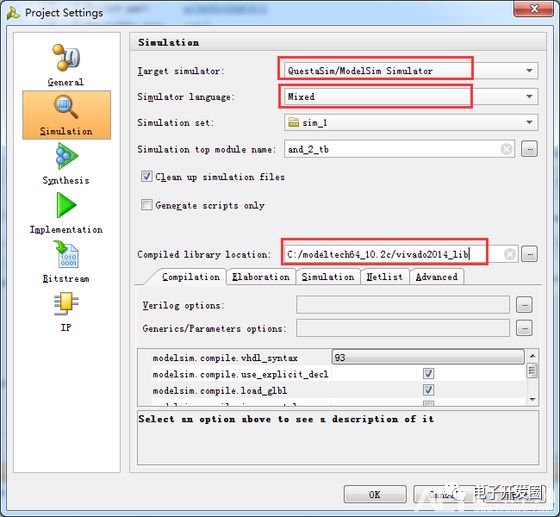

在彈出的對話框中,設置仿真工具為modelsim、仿真語言為verilog或VHDL或混合,當設計中用到vivado中自帶的仿真工具時,還要指定器件庫的路徑,如圖10所示。關于仿真的其他參數在這里就不作介紹了。

圖10 設置仿真參數

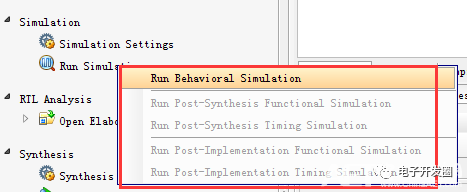

設置好仿真參數后,如果設計文件和仿真文件也準備好,那么就可以開始對設計的功能進行仿真了。選擇菜單“Flow”——》“Run Simulation”——》選相應的仿真類型或點擊流程向導中的“Run Simulation”——》選相應的仿真類型進行仿真,如圖11所示。

圖11 選擇相應的仿真類型進行仿真

編輯:lyn

-

ModelSim

+關注

關注

5文章

174瀏覽量

47952 -

Vivado

+關注

關注

19文章

831瀏覽量

68303

原文標題:Vivado與Modelsim關聯方法及器件庫編譯

文章出處:【微信號:zhuyandz,微信公眾號:FPGA之家】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

如何使用One Spin檢查AMD Vivado Design Suite Synth的結果

如何啟用32個MSI和MSI CPU關聯性?

一文詳解Vivado時序約束

每次Vivado編譯的結果都一樣嗎

使用modelsim時的問題分析

Vivado使用小技巧

淺談Vivado編譯時間

ad怎么把原理圖和pcb相關聯

linux開發板如何編譯curl

linux驅動程序的編譯方法是什么

linux驅動程序的編譯方法有哪兩種

ElfBoard技術貼|如何將libwebsockets庫編譯為x86架構

詳解Vivado與Modelsim關聯方法及器件庫編譯

詳解Vivado與Modelsim關聯方法及器件庫編譯

評論