說明:若有考慮不周,歡迎留言指正。

原子層沉積在半導(dǎo)體先進(jìn)制程的應(yīng)用

隨著集成電路工藝技術(shù)的不斷提高,晶體管的特征尺寸及刻蝕溝槽不斷減小,溝槽及其側(cè)壁的鍍膜技術(shù)面臨嚴(yán)峻的挑戰(zhàn),物理氣相沉積(PVD)及化學(xué)氣相沉積(CVD)工藝已經(jīng)無法滿足極小尺寸下良好的臺階覆蓋要求,而控制納米級別厚度的高質(zhì)量超薄膜層制備也成為技術(shù)難點。

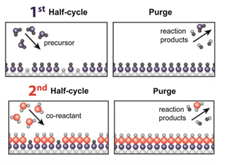

原子層沉積(ALD)是一種可以將物質(zhì)以單原子膜的形式,一層一層鍍在基底表面的先進(jìn)沉積技術(shù)。一個ALD循環(huán)包括兩個先后進(jìn)行的半反應(yīng)(圖1)。在一定的真空環(huán)境下,前驅(qū)體和共反應(yīng)物交替地通入反應(yīng)腔體,飽和吸附并在襯底表面發(fā)生化學(xué)反應(yīng)形成單原子層。每個半反應(yīng)間通入惰性氣體進(jìn)行清洗,確保完全除去過量的反應(yīng)物和生成的小分子副產(chǎn)物。理論上,經(jīng)過一個循環(huán)工藝,基底表面便鍍上了一層單原子膜。通過增加循環(huán)次數(shù),原子層將依次沉積在表面上,形成薄膜。

由于前驅(qū)體和共反應(yīng)物的化學(xué)吸附(化學(xué)反應(yīng))自限制性,運(yùn)用ALD技術(shù)可以大面積沉積均勻無孔的超薄膜,在亞納米尺度上精確控制膜厚,并且在高深寬比、形狀復(fù)雜的結(jié)構(gòu)中具有優(yōu)異的保形性。ALD沉積薄膜的溫度窗口很寬,反應(yīng)對生長溫度并不敏感,因此它可以適應(yīng)不同溫度環(huán)境下的薄膜制備。鑒于ALD的工藝特點和沉積薄膜的諸多優(yōu)勢及特征,近年來獲得了研究人員和企業(yè)各界的廣泛關(guān)注,尤其是在半導(dǎo)體產(chǎn)業(yè)發(fā)揮越來越重要的作用。

圖1 單個原子層沉積工藝的循環(huán)過程[1]

目前,對于金屬、金屬氧化物、氮化物、碳化物、硫化物、氟化物的原子層沉積研究卓有成效。ALD在半導(dǎo)體先進(jìn)制程中主要的應(yīng)用包括金屬柵、柵介質(zhì)層和互連線擴(kuò)散阻擋層加工工藝三個方面。

金屬柵:

在新一代制程中,原有的半導(dǎo)體多晶硅柵極將被金屬取代以消除層間損耗,而此處金屬沉積可選用ALD工藝完成。

P型半導(dǎo)體

1.1 Ru

Ru作為P型半導(dǎo)體柵極的ALD工藝相對成熟,主要是在NH3等離子體的還原作用下將前驅(qū)體材料包括RuCp2(Cp=環(huán)戊二烯基)、Ru(EtCp)2(Et=乙基)還有Ru(od)2(od=辛二酮)、Ru(thd)3(thd=2,2,6,6-四甲基-3,5-庚二酮)在NH3還原作用下生成金屬Ru或者是在O2的作用下將前驅(qū)體氧化為RuOx[1-2]。雖然Ru前驅(qū)體種類眾多,但是由于Ru金屬本身屬于惰性材料,所以一旦吸附在硅片背面會很難除去。然而在實際生產(chǎn)中,CMP過程會不可避免地誘導(dǎo)金屬柵極在背面的污染,對CMOS生產(chǎn)的前端非常不友好,所以Ru作為金屬柵極的應(yīng)用受到了限制。

1.2TiN

TiN是P型半導(dǎo)體柵極的理想材料,不僅電阻率低、工藝兼容性好,而且還和柵極介質(zhì)層HfO2有良好的熱穩(wěn)定性。1988年,Hiltunen等人率先對ALD沉積TiN的工藝進(jìn)行了研究,通過使用TiCl4作為前驅(qū)體NH3做共反應(yīng)物,500℃下能夠在玻璃上均勻沉積多晶TiN,但是沉積速率只有0.02nm/循環(huán)[3]。此外,還有研究使用TiI4作為前驅(qū)體,和TiCl4相比其沉積溫度能夠下降至350℃,其沉積速率也有明顯改善[4]。但是如果要實際應(yīng)用在CMOS的工藝,以上的沉積速率還遠(yuǎn)遠(yuǎn)不夠,主要原因在于共反應(yīng)物NH3提供的N成分遠(yuǎn)遠(yuǎn)不夠Ti-N鍵的連接,所以研究者們開發(fā)了作為TEMAT(Ti[N(C2H5CH3)2]4)新型前驅(qū)體,使反應(yīng)窗口能夠降低至150-220℃,沉積速率也提高為原先的10倍[5]。以上的研究為TiN作為金屬柵極提供了良好的技術(shù)基礎(chǔ),迄今仍然主要使用上述提到的前驅(qū)體作為研究方向。

2. N型半導(dǎo)體

和P型半導(dǎo)體相比,用ALD沉積N型半導(dǎo)體更為困難,最早的研究開始于2007年,Triyoso等人用PEALD沉積了TaCy薄膜,在此基礎(chǔ)上開展了對TiAlC和TaAlC的研究。

TiAlC一般是以TiCl4作為作為Ti前驅(qū)體,以TMA (三甲基鋁)作為Al前驅(qū)體,一個完整的沉積過程由脈沖TiCl4--吹掃N2--脈沖TMA--吹掃N2組成,最終能夠形成粗糙度只有0.33nm的無定形膜層,通過C-V測試可知缺陷很少,唯一的缺點是和高性能nMOSFETs相比,這種方法得到的EWF shift很小。通過把Al前驅(qū)體從TMA更換為TEA(三乙基鋁),TEA提供了更多的β-H能夠有效清除H2,提高Al的生成效率,因而被廣泛使用[6]。

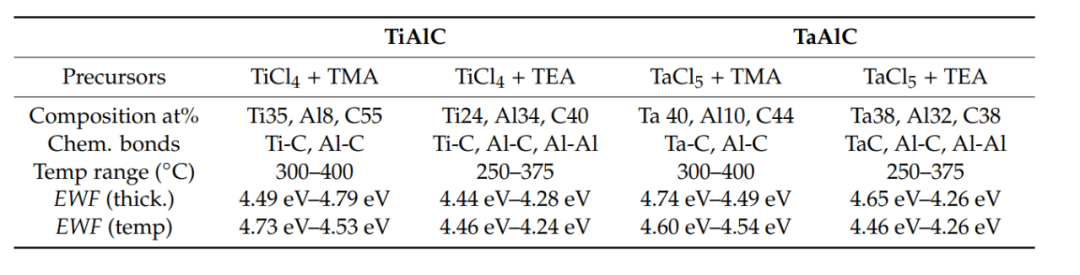

TaAlC一般是用TaCl5作為作為Ti前驅(qū)體,TMA、TEA作為Al前驅(qū)體,從表一可看出,兩種材料的沉積工藝和性能都非常相似[7-8]。

表一:TiAlC和TaAlC層的工藝對比

參考文獻(xiàn):

[1]Aaltonen,T. Atomic Layer Deposition of Noble Metal Thin Films. Ph.D. Thesis, Universityof Helsinki,

Helsinki, Finland, 2005.

[2]Park, K.J.The Atomic Layer Deposition of Noble Metals for Microelectronics Applications.Ph.D. Thesis,

North Carolina State University, Raleigh, NC, USA, 2010.

[3]Ritala,M.; Leskel?, M.; Rauhala, E.; Haussalo, P. Atomic Layer Epitaxy Growth of TiNThin Films.

J. Electrochem. Soc. 1995, 142, 2731–2737.

[4]Ritala, M.;Leskel?, M.; Rauhala, E.; Jokinen, J. Atomic Layer Epitaxy Growth of TiN ThinFilms from Til4 and NH3. J. Electrochem. Soci. 1998, 145, 2914–2920.

[5]Jeon, H.;Lee, J.-W.; Kim, Y.-D.; Kim, D.-S.; Yi, K.-S. Study on the characteristics ofTiN thin film deposited by the atomic layer chemical vapor deposition method.J. Vac. Sci. Technol. A 2000, 18, 1595–1598.

[6]Triyoso,D.H.; Gregory, R.; Schaeffer, J.K.; Werho, D.; Li, D.; Marcus, S.; Wilk, G.D.Atomic layer deposited TaCy metal gates: Impact on microstructure, electricalproperties, and work function on HfO2 high-k

dielectrics. J. Appl. Phys. 2007, 102, 104509

[7]Xiang, J.; Li, T.; Wang, X.; Du, L.; Ding, Y.; Wang, W.; Li,J.; Zhao, C. Thermal Atomic Layer Deposition of TaAlC with TaCl5 and TMA asPrecursors. ECS J. Solid State Sci. Technol. 2016, 5, P633–P636.

[8]145. Xiang, J.; Wang, X.; Li, T.; Gao, J.; Han, K.; Yu, J.; Wang, W.; Li,J.; Zhao, C. Investigation of Thermal Atomic Layer Deposited TaAlC with LowEffective Work-Function on HfO2 Dielectric Using TaCl5 and TEA as Precursors.ECS J. Solid State Sci. Technol. 2017, 6, P38–P41.

柵介質(zhì)層:

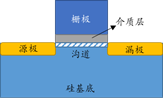

在集成電路產(chǎn)業(yè)史上,為了追逐摩爾定律,MOSFET(圖2)的特征尺寸不斷縮小,工作電壓也不斷降低。為了抑制短溝道效應(yīng),減小柵介質(zhì)層對提高柵電容以提高柵對溝道的控制能力,調(diào)節(jié)閾值電壓起著至關(guān)重要的作用[2]。在傳統(tǒng)MOS器件中,通過簡單的氧化工藝可以在Si襯底上得到一層所需厚度的SiO2層作為柵介質(zhì)層。當(dāng)集成電路器件特征尺寸進(jìn)入180nm時,柵氧化層的厚度小于3nm。由于P型摻雜多晶硅柵的硼穿透效應(yīng)日益嚴(yán)重(硼在SiO2介質(zhì)中屬于快擴(kuò)散物質(zhì)),半導(dǎo)體業(yè)界在氧化工藝中加入NO、N2O和NH3等含氮氣體以形成更致密的SiON介質(zhì)層改善純SiO2的不足。

隨著技術(shù)節(jié)點的跟進(jìn),當(dāng)制程工藝特征線寬要求小于45nm,相應(yīng)的SiO2層厚度將縮小至1nm以下,此時量子隧穿效應(yīng)的影響將急劇增加——以NMOS為例,襯底的電子以量子形態(tài)大概率地穿過柵介質(zhì)層進(jìn)入柵,導(dǎo)致柵漏電十分嚴(yán)重。通過改善氧化工藝提高介質(zhì)層氮含量以及減小SiO2厚度的方法繼續(xù)縮小MOS器件難以為繼,開發(fā)新工藝制備新材料以代替SiO2和SiON十分重要。

在集成電路的發(fā)展歷程中,選用比SiO2介電常數(shù)(3.9)更高的高k材料成為解決這一技術(shù)瓶頸的關(guān)鍵一招。高k材料的選擇除了具有高的介電常數(shù)外,還需滿足寬禁帶、與襯底材料間足夠的能帶偏移量和低的界面態(tài)。

絕大多數(shù)高k材料的加工工藝都依賴于原子層沉積技術(shù)。此前,基于ALD沉積的一些重要研究包括TiO2、HfO2、Al2O3、ZrO2、Ta2O5,稀土元素氧化物和一些硅酸鹽混合的納米層狀結(jié)構(gòu)材料[3]。Si3N4、Al2O3介電常數(shù)仍較低。TiO2雖然介電常數(shù)很高(80),但禁帶寬度小且與襯底明顯的界面缺陷限制了其作為柵介質(zhì)的應(yīng)用[4]。HfO2的介電常數(shù)為25,具有適合的禁帶寬度(5.8eV),綜合各方面性能要求,高k材料HfO2作為柵介質(zhì)層得到了業(yè)內(nèi)廣泛的認(rèn)可和應(yīng)用。

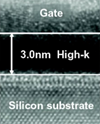

英特爾公司在90nm技術(shù)節(jié)點上,柵氧化層采用了1.2nm的SiO2(圖3);而在32nm技術(shù)代,采用原子層沉積技術(shù)引入了HfO2(圖4)作為柵介質(zhì)材料解決了柵漏電和硼穿透的問題。3nm的HfO2層的等效氧化層厚度為0.8nm,也就是說3nmHfO2與0.8nmSiO2對于柵電容的貢獻(xiàn)、調(diào)節(jié)閾值電壓的效果相同,而實際物理厚度的增加大大減弱了量子隧穿效應(yīng)的影響。

圖2 MOSFET結(jié)構(gòu)示意圖

圖3 英特爾 90nm 技術(shù)節(jié)點采用1.2nm SiO2柵介質(zhì)層(來源于網(wǎng)絡(luò))

圖4 英特爾32nm 技術(shù)節(jié)點采用3.0nmHfO2柵介質(zhì)層(來源于網(wǎng)絡(luò))

利用高k材料代替常規(guī)的SiO2(或SiON)作為柵介質(zhì)層,以及采用金屬柵代替多晶硅柵的工藝稱為HKMG技術(shù),可見原子層沉積在MOSFET的HKMG技術(shù)革新中發(fā)揮了巨大的作用。

參考文獻(xiàn):

[1] Xuefeng Xu, Jingang Wang, Mengtao Sun. Spectralanalysis on CoOx films deposited by atomic layer deposition[J].Chemical Physics Letters,2020,742:137159

[2]溫德通。集成電路制造工藝與工程應(yīng)用[M]。北京:機(jī)械工業(yè)出版社,2018.

[3]付盈盈。高介電薄膜材料的原子層沉積技術(shù)制備、表征及其在微電子領(lǐng)域的應(yīng)用[D]。南京:南京大學(xué)碩士學(xué)位論文,2012.

[4]王蝶.MOS器件堆棧柵結(jié)構(gòu)設(shè)計、界面及電化學(xué)性能優(yōu)化[D]。合肥:安徽大學(xué)碩士學(xué)位論文,2020.

互連線擴(kuò)散阻擋層:

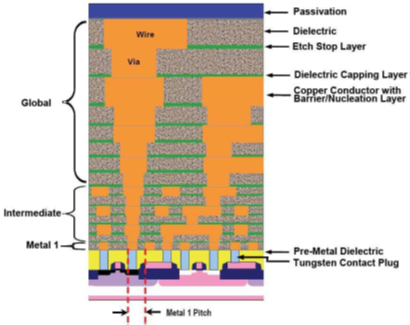

摩爾定律導(dǎo)致芯片中功能密度的增加,定義了每個芯片區(qū)域中互連設(shè)備的數(shù)量。隨著IC的最小特征尺寸減小,有源器件密度增加。由于芯片表面上互連線所占據(jù)的面積比容納有源器件所需的面積擴(kuò)展得更快,因此器件集成變得更加苛刻。最終,最小的芯片面積受限于互連技術(shù)。這一問題是通過多層互連系統(tǒng)解決的,其中互連線所需的區(qū)域在兩個或更多層之間共享(圖5)。

微處理器單元(MPU)中有源器件的功能密度非常高,金屬級的數(shù)量有望達(dá)到1216。此外,隨著柵極數(shù)量增多,柵極之間需要更多的連接,互連線的平均長度將增加。如果不包括全局電線,則MPU中互連的總長度預(yù)計將超過2 km / cm2。在1990年代后期,很明顯地發(fā)現(xiàn),互連長度的增加導(dǎo)致互連的電阻乘以電容(RC)時間延遲的增加,并且在四分之一微米的設(shè)備節(jié)點中,傳播延遲超過了固有延遲。

除RC延遲外,由于鋁對電遷移的敏感性強(qiáng),隨著電流密度的增加,傳統(tǒng)的鋁金屬化也面臨著巨大的挑戰(zhàn)。因此,銅因其較高的電遷移電阻和低電阻率逐漸取代鋁工藝稱為互聯(lián)技術(shù)的主流技術(shù)[1]。

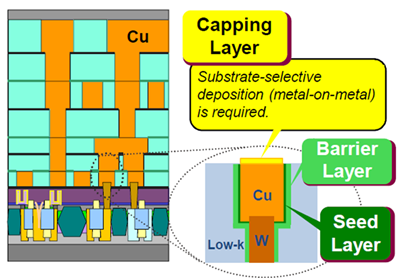

互連工藝中需要使用一層阻擋層金屬,它可以增強(qiáng)鋁銅合金互連線附著在硅化物上的力,減小互連線與接觸孔之間的接觸電阻和應(yīng)力,氮化鈦還可以防止硅與鋁之間相互擴(kuò)散,避免鋁穿刺。鋁工藝中的阻擋層金屬是鈦(Ti)和氮化鈦(TiN)。高溫時Cu在Si中擴(kuò)散系數(shù)較高,銅原子一旦進(jìn)入硅器件,便會成為深能級受主雜質(zhì)產(chǎn)生復(fù)合中心,使載流子壽命降低,從而導(dǎo)致器件失效。因此在銅互連結(jié)構(gòu)中阻擋層金屬更為必須[2]。銅的阻擋層金屬是鉭(Ta)和氮化鉭(TaN)。

隨著工藝技術(shù)的不斷發(fā)展,線寬的減小使得銅線的阻抗上升,電路的RC特性降低,RC延時增加。解決這一問題的最簡單辦法就是降低擴(kuò)散阻擋層的厚度。阻擋層金屬的厚度不斷變薄,鉭和氮化鉭作為阻擋層金屬的阻擋性能比鈦和氮化鈦好,所以在銅工藝中利用氮化鉭代替氮化鈦。利用PVD技術(shù)沉積的氮化鉭是工業(yè)上應(yīng)用最多的技術(shù),它能較好地控制N/Ta比。

但是由于PVD沉積流量的方向性和對多數(shù)金屬的高粘結(jié)系數(shù),導(dǎo)致制備薄膜不連續(xù),臺階覆蓋率低。CVD存在鍍制薄膜較厚,成分不純等內(nèi)在缺陷。通過ALD過程,在器件尺寸小于100nm和較低的溫度下,能夠得到階梯覆蓋率高,原子層厚度較薄且可精確控制的銅擴(kuò)散阻擋層[3]。

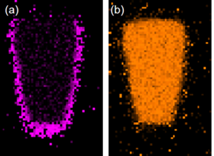

目前ALD TaN技術(shù)用于銅互連阻擋層被廣泛的研究。早在2002年,Kim等人[4]利用plasma-enhancedALD的方法用TaCl5,氫氣和氮氣等離子體在硅基底上沉積TaN薄膜。隨后Kim等人[5]使用Ta金屬有機(jī)物前驅(qū)體和氫等離子體技術(shù)生成了堅固且超薄的TaNx銅擴(kuò)散阻擋層,定量研究了擴(kuò)散阻隔性能,并且提出該層優(yōu)異的阻擋性能歸因于膜的納米晶體微觀結(jié)構(gòu)。

Furuya等人[6]用Ta(N(CH3)2)5和He/H2等離子體沉積了富Ta的TaN粘合層,克服了由于ALD阻擋層金屬與Cu之間低粘附性導(dǎo)致的通孔產(chǎn)量低的問題。Dey等人[7]研究發(fā)現(xiàn),在10nm節(jié)點以下的工藝技術(shù)中,當(dāng)其他的金屬如釕取代銅作為互聯(lián)金屬,ALDTaN仍能表現(xiàn)出優(yōu)異的阻擋層性能。但是由于ALD存在生長速度較慢等問題,目前半導(dǎo)體產(chǎn)業(yè)中銅互連阻擋層仍然采用PVD的方法。但是由于ALD技術(shù)擁有PVD和CVD所無法比擬的優(yōu)勢,在科技工作者的共同努力下,ALD擴(kuò)散阻擋層最終會被大規(guī)模應(yīng)用。

圖5 MPU器件分級放大橫截面圖[1]

圖6 淺綠色部分(barrierlayer)為阻擋層

圖7(a)為Ta阻擋層的能量色散X射線光譜儀(EDX)圖像,(b)為Cu的EDX圖像[8]

參考文獻(xiàn)

[1]Kai-Erik Elers. Copper Diffusion BarrierDeposition on Integrated Circuit Devices by Atomic Layer Deposition Technique.Helsinki, 2008

[2]申燦,劉雄英,黃光周。原子層沉積技術(shù)及其在半導(dǎo)體中的應(yīng)用[J]。真空,2006(04):1-6.

[3]李惠琴,陳曉勇,王成,穆繼亮,許卓,楊杰,丑修建,薛晨陽,劉俊。原子層沉積技術(shù)在微納器件中的應(yīng)用研究進(jìn)展[J]。表面技術(shù),2015,44(02):60-67.

[4]H. Kim, A. J. Kellock, S. M. Rossnagel. Growthof cubic-TaN thin films by plasma-enhanced atomic layer deposition[J]。 Journalof Applied Physics, 2002,92:7080-7085.

[5] H. Kim, C. Detavenier, O. van der Straten,, etal., Robust diffusion barrier for Cu-interconnect technology with subnanometerthickness by metal-organic plasma-enhanced atomic layer deposition[J]。 Journalof Applied Physics, 2005,98:014308.

[6] Akira Furuya, Hiroshi Tsuda, and ShinichiOgawa. Ta-rich atomic layer deposition TaN adhesion layer for Cu interconnectsby means of plasma-enhanced atomic layer deposition[J]。 Journal of VacuumScience & Technology B,2005,23:979-983.

[7] Sonal Dey, Kai-Hung Yu, Steven Consiglio etal., Atomic layer deposited ultrathin metal nitride barrier layers forruthenium interconnect applications[J]。 Journal of Vacuum Science &Technology A,2017,35:03E109.

[8] C.-C.Yanga, F.Baumannb, P.-C.Wang et al.,Dependence of Cu electromigration resistance on selectively deposited CVD Cocap thickness[J]。 Microelectronic Engineering 2013,106:214–218

編輯:jq

-

半導(dǎo)體

+關(guān)注

關(guān)注

335文章

28666瀏覽量

233304 -

RC

+關(guān)注

關(guān)注

0文章

236瀏覽量

49560 -

MPU

+關(guān)注

關(guān)注

0文章

409瀏覽量

49689

原文標(biāo)題:ALD在半導(dǎo)體先進(jìn)制程的應(yīng)用 | 技術(shù)專欄

文章出處:【微信號:TruthSemiGroup,微信公眾號:求是緣半導(dǎo)體聯(lián)盟】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

半導(dǎo)體制冷機(jī)chiller在半導(dǎo)體工藝制程中的高精度溫控應(yīng)用解析

瑞樂半導(dǎo)體——On Wafer WLS-WET 濕法無線晶圓測溫系統(tǒng)是半導(dǎo)體先進(jìn)制程監(jiān)控領(lǐng)域的重要創(chuàng)新成果

愛發(fā)科發(fā)布多款半導(dǎo)體制造利器,引領(lǐng)先進(jìn)制程技術(shù)革新

芯和半導(dǎo)體將參加重慶半導(dǎo)體制造與先進(jìn)封測產(chǎn)業(yè)發(fā)展論壇

SEMI-e 2025:聚焦半導(dǎo)體制造與先進(jìn)封裝領(lǐng)域,探索行業(yè)發(fā)展新路徑

臺積電加速美國先進(jìn)制程落地

半導(dǎo)體薄膜沉積技術(shù)的優(yōu)勢和應(yīng)用

三星SF4X先進(jìn)制程獲IP生態(tài)關(guān)鍵助力

半導(dǎo)體制造里的ALD工藝:比“精”更“精”!

臺積電美國芯片量產(chǎn)!臺灣對先進(jìn)制程放行?

環(huán)球晶獲4.06億美元補(bǔ)助,用于12英寸先進(jìn)制程硅晶圓等擴(kuò)產(chǎn)

半導(dǎo)體晶圓測試中的關(guān)鍵之“手”,看陶瓷基板作用何處?

喆塔科技先進(jìn)制程AI賦能中心&amp;校企聯(lián)合實驗室落戶蘇州

淺談ALD在半導(dǎo)體先進(jìn)制程的應(yīng)用

淺談ALD在半導(dǎo)體先進(jìn)制程的應(yīng)用

評論