1 概述

CY7B923是CYPRESS半導體公司推出的一種用于點對點之間高速串行數據通信的發送芯片。CY7B923采用的是基帶傳輸通信方式,并支持帶電插拔(熱接插)。其內部電路主要包括時鐘產生器、輸入寄存器、編碼器、移位寄存器、三對差分PECL輸出對以及測試邏輯等。該芯片外轉帳電路比較簡單,不需單片機或微機控制,并且內置有自測試電路,因此使用比較方便。CY7B923的最大傳輸速率可達400Mbps,有三種傳輸速率的器件可供選擇:標準系列的器件有CY7B923-JC、CY7V923-JI、 CY7B923-SC及CY7B923-LMB四種型號,它們的傳輸速率為160~330Mbps;高速系列器件有CY7B923-400JC和CY7B923-400JI兩種型號,傳輸速率可達160~400Mbps;對一些傳輸速率要求不高的場合,可采用較低價格的CY7B923-155JC或CY7V923-155JI,其傳輸速率為150~160Mbps。CY7B923采用單一的+5V電源供電,功耗僅 350mW。可兼容光纖、IBM ESCON、DVB-ASI及SMPTE-259M等多種傳輸協議,適用于光纖、同軸電纜和雙絞線等傳輸媒介。

2 引腳功能及內部結構

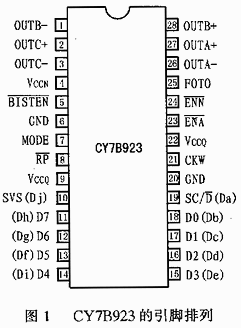

CY7B923有28腳SOIC、PLCC和LCC三種封裝形式,采用 0.8μBiCMOS工藝,其此腳排列如圖1所示(SOIC封裝),引腳功能如表1所列。

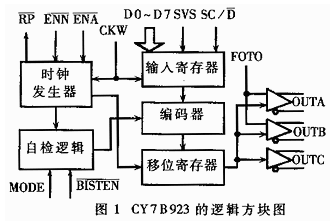

CY7B923的內部結構如圖2所示,其內部主要包括時鐘產生器、輸入寄存器、編碼器、移位寄存器、三對差分PECL輸出對(OUTA±、OUTB±及OUTC±)及測試邏輯等電路。

輸入寄存器的數據輸入時序和標準FIFO的數據輸出時序相一致,因而不需外加邏輯電路,便可知同步FIFO芯片或異步FIFO芯片直接連接并將FIFO芯片中的數據讀入到輸入寄存器中,然后再發送出去。在BIST方式下,借助于內部邏輯電路,并行輸入寄存器又可作為線性反饋移位寄存器,用于產生一串511字節的包含有數據、特定的有效字符碼以及設定的違例碼等一串偽隨機序列。

編碼器用于將保存在輸入寄存器的數據轉換為適合串行口輸出的數據形式。由SC/D的輸入狀態來決定其編碼方式:SC/D=1(高電平)時,按控制碼表轉換輸入的數據為控制碼;SC/D=0(低電平)時,按數據碼表轉換輸入的8位數據為10位數據碼。當設定MODE為高電平時,可將編碼器的8B/10B編碼功率屏蔽掉。

CY7B923的OUTA±和OUTB±受FOTO控制,OUTC±則不受FOTO影響,OUTC±能連續輸出數據流,適用于系統進行自環測試。為減少功耗,不用的輸出端均應接VCC(+5V電源),以禁止相應的輸出電路工作。

3 工作原理及操作方式

3.1 工作原理

CY7B923作為點對點串行通訊中的發送芯片,其數據傳輸速率可達33M字節/秒(對CY7B923-400系列的芯片可達40M字節/秒)。當ENA或ENN有效(低電平)時,在CKW的上升沿,用戶的8位數據或協議信息將讀入發送器的輸入寄存器中。然后由編碼器編碼后送到移位寄存器,最后在位時鐘的控制下通過三對差分PECL對串行輸出。

3.2 操作方式

CY7B923的發送操作方式有兩種:正常使用操作方式和測試方式。正常使用操作方式又分為編碼方式和直通方式(非編碼方式)。測試方式用于芯片的測試、發送電路的測試和整個系統的測試。測試方式也分為內置自測試方式(BIST方式)和工廠測試方式(芯片測試方式)。下面分別給以介紹。

a.編碼操作方式

在這種方式下,允許用戶發送8位的數據和控制字符。譯碼器根據輸入的8位數據(D0~D7)、數據類型控制碼(SC/D)及系統測試輸入位(SVS)的狀態等對輸入數據進行譯碼,若數據的內容為正常的數據碼,則SC/D為低電平,且應該使用有效數據碼表中的數據字符壽終正寢組來對輸入數據進行編碼。若輸入數據的內容為控制碼或協議信息,則SC/D應為高電平,且應按照有效特殊字符碼和碼系列等表中的字符碼或碼組來對輸入的數據編碼。

測試字符和測試碼系列中包含有測試光纖通路連接的碼組,這些碼組也可用于測試系統連接在傳輸誤碼與定時之間的響應關系。違例字符也可以作為用戶數據包的一部分發送出去(例如:發送C0.7,D7~0=11100000,SC/D),或者由外部系統通過改變SVS輸入電平(SVS置為低電平)來發送違例字符。測試時,無需對系統的傳輸接口電路作任何改動即可使其產生傳輸誤碼,因而允許系統測試邏輯按照確定的方式來評估系統的誤碼率。

b.直通操作方式

在此方式下,輸入的數據是已譯碼的10位數據即D0~9(Db-h)、(Da)、和SVS(Dj)等數據,SC/D和SVS分別作為Da和Dj的數據輸入腳。這10位數據經直接串行化后即可發送出去。數據譯碼方式的選擇可由設計者決定,對數據的譯碼也可通過外加電路來實現。需要注意的是:所選擇的譯碼方式必須保證譯碼后數據位之間有適當的變化,以使接收器中的鎖相環電路能與輸入數據同步(至少每10位必須有一個數據位是變化的),但這種方式并不常用。

4 CY7B923構成發送電路設計實例

圖3為由CY7B923構成的一個實際的發送應用電路。該電路主要由CY7B923發送芯片、IDT7200(FIFO)芯片、阻抗變換匹配線圈及相關的電阻和電容等組成。FIFO芯片的讀信號由CY7B923的RP腳提供。CY7B923的發送控制由外部提供的ENAC和FIFO芯片的SEF信號來共同完成。通過設置拔碼開關U7的相關位置可以將CY7B923發送芯片的工作方式設置在正常發送方式或內置測試方式。具體的操作方法如下;

(1)SBIST=0時,設置為內置自測試方式

此時,若ENA=1,發送器開始發送…1010…交替變化的位系列。如果用示波器測試輸出端,則可看到一個近似的正弦波。

若ENA=0,則發送器開始重復發送一組測試系列碼。在每一個BIST測試循環中,RP腳都將產生一個負脈沖。因而可由外部計數器或示波器來監測發送測試碼組的循環次數。

(2)SBIST=1時,設置為正常使用方式

在正常使用方式時,ENA應和ENAU相連接。其工作過程為:首先用戶將需要發送的一幀數據(包括用戶協議和用戶數據信息)寫入FIFO芯片,然后再啟動發送器CY7B923并由CY7B923發送出去。CY7B923在從FIFO芯片中讀出數據后,先進行串-并轉換,然后才將數據發送出去。當一幀數據發送完畢后,由FIFO芯片中的EP信號自動控制CY7V923,以使其停止讀取FIFO芯片中的數據。此時用戶可通過測試TENAS端的狀態來了解FIFO芯片中的數據是否已發送完畢。若發送完畢,則可將下一幀數據寫入FIFO芯片,再啟動另一次發送過程。

CY7V923的應用比較簡單,其發送數據率也比較高。可廣泛應用于工作站、服務器、大存儲器之間的互連或視頻傳輸等領域。

責任編輯:gt

-

電源

+關注

關注

185文章

18297瀏覽量

255192 -

芯片

+關注

關注

459文章

52252瀏覽量

436912 -

半導體

+關注

關注

335文章

28666瀏覽量

233290

發布評論請先 登錄

高速串行數據通信發送芯片CY7B923的原理及應用

雙口RAM CY7C025 實現DSP間的高速數據通信

MATLAB環境下的串行數據通信系統設計

CY7B923用作ECL時鐘源

介紹(HOTLink)CY7B933 RDY引腳在編碼、旁路

連接CY7B923和CY7B933(HOTlink器件)至定

連接CY7B923和CY7B933(HOTlink器件)至寬

如何用Cypress的CY7B923 CY7B933替換Am

在CY37032 CPLD中,用CY7B933 HOTLin

基于Matlab環境的串行數據通信

基于CY68013的數據通信系統設計

基于CY7C68013的高速數據通信接口設計

基于USB2.0芯片CY7C68013的高速數據通信接口設計

數據收發器CY7B923/933的性能特點和應用范圍

高速串行數據通信CY7B923芯片的性能特點及設計實例

高速串行數據通信CY7B923芯片的性能特點及設計實例

評論