在本文中,我們將高層次地了解模擬集成電路的設計過程。

1模擬ICVS數字IC

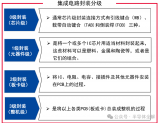

首先模擬IC設計與數字IC設計上有很大的不同。數字IC的設計大多是在抽象的層次上完成的,這些層次的系統和過程決定了門/晶體管級的布局和走線的細節,而模擬IC的設計通常涉及到每個電路更多的個性化焦點,甚至是每個晶體管的尺寸和細節。

此外,許多制造工藝主要是針對具有模擬功能的數字IC開發的,這就要求模擬IC設計人員應對工藝限制和更適合數字IC的功能進行工作。

1設計規格

模擬設計團隊通常從一組規格和特性開始,就像數字集成電路設計一樣。從那里,各種功能的功能模型被用來進一步縮小約束,并導致關于設備大小、類型和其他過程特性的決策。這可能包括晶體管的選擇,高層次的布局規劃,包括電感和電容技術,以及 IC 和子電路的期望值。

體系結構硬件描述語言(AHDL) ,如 VHDL-AMS,用于在高層進行仿真,并確定子塊的約束。在這個階段也可以開發一個測試臺,這個測試臺后來用于仿真,盡管模擬設計人員也經常為他們的子電路設計開發測試臺。

2分電路設計,物理布局和模擬

有了這些細節,并根據模擬電路的復雜性,模擬設計團隊通常將子電路設計分配給個人。理想化的宏觀測量進一步確定子電路的約束條件和性能期望。

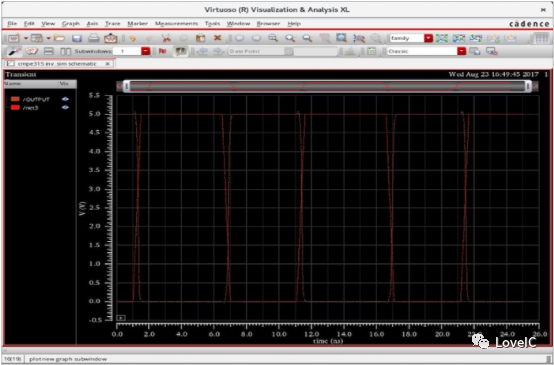

接下來,這些宏示意圖被分解為示意圖與電路元件模型從鑄造過程。對這些電路進行了仿真和優化,然后開始物理布局過程。布局和路由之后的設計規則檢查(DRC)和電路佈局驗證是在寄生提取和布局后仿真之前完成的。

版圖后仿真可能會揭示設計中的缺陷,需要一個迭代的重新設計、版圖設計和仿真過程,以滿足最終的設計目標,并提交芯片進行輸出。在整個芯片布局和仿真之前,子電路也可能經歷它們自己的設計、布局和仿真過程,不過這兩種方法都可能導致需要在tape-out之前重新設計電路。

Cadence 模擬設計環境的波形窗口實例

文章出處:【微信公眾號:FPGA開源工作室】

責任編輯:gt

-

芯片

+關注

關注

459文章

52253瀏覽量

436979 -

集成電路

+關注

關注

5420文章

11971瀏覽量

367378 -

IC

+關注

關注

36文章

6102瀏覽量

178537

原文標題:什么是模擬IC設計?

文章出處:【微信號:leezym0317,微信公眾號:FPGA開源工作室】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

電機控制專用集成電路PDF版

中國集成電路大全 接口集成電路

基于運算放大器和模擬集成電路的電路設計(第3版)

法動科技EMOptimizer解決模擬/射頻集成電路設計難題

集成電路設計中靜態時序分析介紹

集成電路封裝的發展歷程

模擬集成電路的設計是什么 設計過程如何

模擬集成電路的設計是什么 設計過程如何

評論