用國產(chǎn)EDA工具做芯片是什么樣的體驗(yàn)(route篇)

05 Route

接下來進(jìn)入繞線部分,route的部分跟place和cts一樣,也是分成布線和優(yōu)化兩部分,route常用到的操作有三部分:

繞線時需要用到一些特殊的繞線規(guī)則,我們舉例說明:

實(shí)際調(diào)用這些特定的繞線規(guī)則時,把command中的set替換為assign即可。 在AG里的route部分,route和opt被整合成了一個超級命令route_optimize 一如USB接口的發(fā)展史一樣,從早先的Type A/B傻大粗笨易插錯。到現(xiàn)在Typc-c一統(tǒng)天下,連喜歡自己搞一套的Apple都慢慢轉(zhuǎn)向Type-c。 EDA的各個工具廠商也是一樣,都喜歡使用超級命令來控制各個步驟的運(yùn)行,原因主要是精簡流程和減少人為干涉造成的問題。帶來的問題就是一出錯Debug原因就變得比較復(fù)雜(當(dāng)然對于購買的正版的公司可以祭出召喚AE的終極大招)。 理論上route_optimize完的數(shù)據(jù)基本接近signoff,加上filler,分析完時序、設(shè)計規(guī)則等等signoff標(biāo)準(zhǔn)后,直接輸出各類交付數(shù)據(jù)。 上面大致就是拿國產(chǎn)APR工具Aguda去做Verilog2Gds的過程。

一點(diǎn)感想

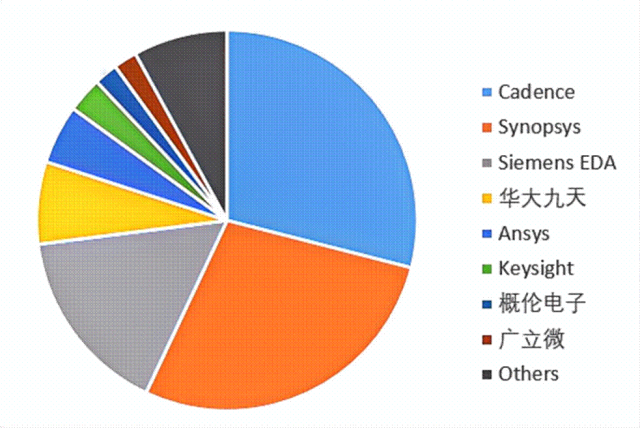

在這次完整走完國產(chǎn)工具的APR flow后,有了真實(shí)體驗(yàn)才有發(fā)言權(quán),來講一講對于EDA甚至半導(dǎo)體行業(yè)的看法。從ZTE被制裁開始,到華為等一眾上了“實(shí)體名單”后,媒體們開始狂轟濫炸,半導(dǎo)體相關(guān)的標(biāo)簽映入各位看客的眼簾。

“新冠”疫情后的消費(fèi)電子品需求暴增更是直接引起了“缺芯”狂潮,甚至隔壁熱心大媽第一次搞清楚我是造芯片的而不是干挨踢的(IT),然后一個勁問我“缺鋅”補(bǔ)哈爾濱制藥的藍(lán)瓶管不管用。環(huán)境造就了這么一鍋熱湯,真正身處其中的“IC牛蛙”們才真的冷暖自知。媒體們天天喊“卡脖子”,嚴(yán)重了講幾乎是“卡身子”,卡得巧手硅農(nóng)難為無米之炊;BAT玩剩下的人均百萬,跑到IC圈來還未綻放已然萎縮,然后留下996和007的“福報”。 我不喜歡喋喋不休地討論分析說我們沒有這個那個,所以做不了一二三四然后挨了揍;我喜歡說手頭有點(diǎn)啥先做點(diǎn)啥,別把“彎道超車”這種交通法明確規(guī)定違法的行為,當(dāng)成了蛇精的如意反復(fù)念叨“快快顯靈”。

沒有的東西我們一時半會兒也不會馬上有,有的東西可以大膽嘗試用起來,尤其像APR這種可以通過時序分析、形式驗(yàn)證、后端仿真、物理驗(yàn)證等工具進(jìn)一步驗(yàn)證其結(jié)果的正確性的工具。可以用大的格局說我們要做完整的數(shù)字電路設(shè)計的全流程工具,但突破點(diǎn)可以是APR、可以是ECO甚至更細(xì)節(jié)的某個步驟中的點(diǎn)工具,知微見著,不積“硅”步無以至千里,半導(dǎo)體發(fā)展的鐵律早就寫死在古書里了。

所以,如果上天給我再來一次的機(jī)會的話,我會對Aguda說三個字:“再試試 !”

往期回顧

DataPrep 篇

FloorPlan 篇

Place&CTS篇

點(diǎn)擊閱讀原文 加入鴻芯微納

原文標(biāo)題:用國產(chǎn)EDA工具做芯片是什么樣的體驗(yàn)

文章出處:【微信公眾號:鴻芯微納】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

審核編輯:湯梓紅

-

芯片

+關(guān)注

關(guān)注

459文章

52323瀏覽量

438207 -

半導(dǎo)體

+關(guān)注

關(guān)注

335文章

28736瀏覽量

234643 -

eda

+關(guān)注

關(guān)注

71文章

2906瀏覽量

176841

原文標(biāo)題:用國產(chǎn)EDA工具做芯片是什么樣的體驗(yàn)

文章出處:【微信號:giga-da,微信公眾號:鴻芯微納】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

九霄智能國產(chǎn)EDA工具的突圍之路

TSolidX應(yīng)用:液晶掩膜結(jié)構(gòu)GDSⅡ文件的生成和導(dǎo)出

DLPC3478怎么去做ini配置文件和firmware呢 ?

Verilog中signed和$signed()的用法

Verilog 電路仿真常見問題 Verilog 在芯片設(shè)計中的應(yīng)用

Verilog 與 ASIC 設(shè)計的關(guān)系 Verilog 代碼優(yōu)化技巧

Verilog 測試平臺設(shè)計方法 Verilog FPGA開發(fā)指南

Verilog與VHDL的比較 Verilog HDL編程技巧

GDS文件在芯片制造流程中的應(yīng)用

Verilog vhdl fpga

Verilog硬件描述語言參考手冊

如何利用Verilog-A開發(fā)器件模型

如何用國產(chǎn)APR工具Aguda去做Verilog2Gds

如何用國產(chǎn)APR工具Aguda去做Verilog2Gds

評論