在上篇文章《FPGA工程師的核心競(jìng)爭(zhēng)力-方法篇(一)》中,針對(duì)UltraFast設(shè)計(jì)方法論進(jìn)行了概述,并根據(jù)設(shè)計(jì)指南UG949介紹了前面三章的主要內(nèi)容,本篇將重點(diǎn)學(xué)習(xí)解讀后面三章內(nèi)容:設(shè)計(jì)約束、設(shè)計(jì)實(shí)現(xiàn)和設(shè)計(jì)收斂。

設(shè)計(jì)約束

設(shè)計(jì)約束用于定義各項(xiàng)要求,編譯流程必須滿足這些要求才能在硬件中正常運(yùn)行設(shè)計(jì)。對(duì)于較為復(fù)雜的設(shè)計(jì),這些約束通常用于定義工具指南,以幫助實(shí)現(xiàn)收斂。并非所有約束都要在編譯流程中的所有步驟中使用。例如,物理約束僅在執(zhí)行實(shí)現(xiàn)步驟(最優(yōu)化、布局和布線)期間使用。

由于綜合與實(shí)現(xiàn)算法均由時(shí)序驅(qū)動(dòng),因此必須創(chuàng)建正確的時(shí)序約束。對(duì)設(shè)計(jì)進(jìn)行過(guò)約束或欠約束都會(huì)導(dǎo)致難以實(shí)現(xiàn)時(shí)序收斂。為了方便設(shè)計(jì)分析,Xilinx官方指南給出的《Vivado Design Suite 用戶指南:設(shè)計(jì)分析與收斂技巧》(UG906)可以參照。

5.1 對(duì)設(shè)計(jì)約束進(jìn)行組織

通常約束按類別和/或按設(shè)計(jì)模塊組織到 1 個(gè)或多個(gè)文件中。無(wú)論采用何種組織方式,都必須了解其整體依賴關(guān)系,并在載入存儲(chǔ)器后復(fù)查其最終時(shí)序。

如何進(jìn)行約束組織和管理呢?有的工程很小、簡(jiǎn)單,幾個(gè)模塊就完成了,這時(shí)候約束文件不多,不復(fù)雜。但很多時(shí)候,系統(tǒng)很復(fù)雜,幾十個(gè)模塊,多個(gè)時(shí)鐘,管腳也多,約束文件最好根據(jù)類別放幾個(gè),管理起來(lái)也方便。對(duì)于IP,通常采用OOC方式進(jìn)行綜合,并形成獨(dú)自的約束文件。

(1)建議的約束文件

根據(jù)工程大小和復(fù)雜性,有多種適用于約束組織的方法可供選擇。Xilinx給出的建議是:

對(duì)于小型設(shè)計(jì)團(tuán)隊(duì)開(kāi)發(fā)的簡(jiǎn)單設(shè)計(jì):

? 1 個(gè)文件存儲(chǔ)所有約束

? 1 個(gè)文件存儲(chǔ)物理約束 + 1 個(gè)文件存儲(chǔ)時(shí)序約束

? 1 個(gè)文件存儲(chǔ)物理約束 + 1 個(gè)文件存儲(chǔ)時(shí)序(綜合)+ 1 個(gè)文件存儲(chǔ)時(shí)序(實(shí)現(xiàn))

對(duì)于復(fù)雜設(shè)計(jì)(含多個(gè) IP 核或多個(gè)設(shè)計(jì)團(tuán)隊(duì)):

? 1 個(gè)文件存儲(chǔ)頂層時(shí)序 + 1 個(gè)文件存儲(chǔ)頂層物理 + 1 個(gè)文件對(duì)應(yīng) 1 個(gè) IP 或主塊

(2)驗(yàn)證讀取順序

完成工程約束文件的組織后,必須根據(jù)文件內(nèi)容驗(yàn)證文件讀取順序。在“工程模式”下,可在 Vivado? IDE 中或者使用 reorder_files Tcl 命令來(lái)修改約束文件的順序。在“非工程模式”下,順序直接由編譯流程 Tcl 腳本中的read_xdc 命令(針對(duì) XDC 文件)和 source 命令(針對(duì)由 Tcl 腳本生成的約束)來(lái)定義。

(3)建議的約束順序

約束語(yǔ)言 (XDC) 基于 Tcl 語(yǔ)法和解讀規(guī)則。與 Tcl 一樣,XDC 屬于順序語(yǔ)言:

? 必須先定義變量,然后才能加以使用。同樣,必須先定義時(shí)序時(shí)鐘,然后才能將其用于其它約束中。

? 對(duì)于覆蓋相同路徑并具有相同優(yōu)先級(jí)的等效約束,適用最后一項(xiàng)約束。

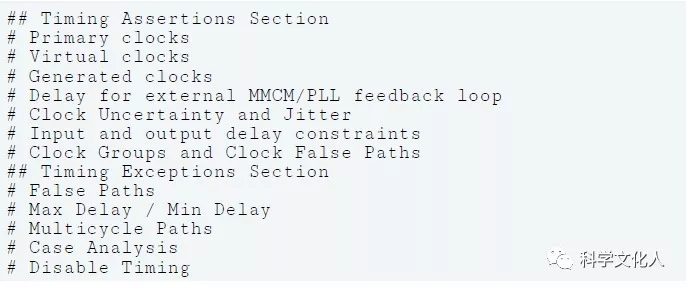

當(dāng)考慮以上優(yōu)先規(guī)則時(shí),時(shí)序約束總體上應(yīng)遵循以下順序:

當(dāng)使用多個(gè) XDC 文件時(shí),必須特別留意時(shí)鐘定義,并驗(yàn)證從屬關(guān)系排序是否正確。比如主時(shí)鐘、生成時(shí)鐘關(guān)系。

物理約束可能位于任意約束文件中的任意位置。綜合工具一般會(huì)自動(dòng)放在時(shí)鐘約束后面,XDC文件也可手動(dòng)編寫(xiě),也可由工具生成。Tcl命令也能用于創(chuàng)建約束文件。

(4)創(chuàng)建綜合約束

綜合將提取設(shè)計(jì)的 RTL 描述,并使用時(shí)序驅(qū)動(dòng)的算法將其變換為經(jīng)優(yōu)化的技術(shù)所映射的網(wǎng)表。結(jié)果質(zhì)量受 RTL 代碼質(zhì)量和提供的約束的影響。在編譯流程的這個(gè)階段,信號(hào)線延遲建模采用近似法,無(wú)法反映布局約束或復(fù)雜影響(例如擁塞)。建模的主要目的是通過(guò)真實(shí)且簡(jiǎn)單的約束獲取滿足時(shí)序約束要求或者接近滿足要求的網(wǎng)表。

重要提示!與實(shí)現(xiàn)階段不同,綜合可能會(huì)將用于定義時(shí)序約束的 RTL 網(wǎng)表對(duì)象優(yōu)化掉以便實(shí)現(xiàn)更好的面積QoR。一般這不會(huì)導(dǎo)致問(wèn)題,前提是對(duì)約束進(jìn)行更新和驗(yàn)證以滿足實(shí)現(xiàn)要求。但如果需要,仍可使用 KEEP 約束來(lái)保留任何對(duì)象以便在綜合和實(shí)現(xiàn)期間應(yīng)用約束。

(5)創(chuàng)建實(shí)現(xiàn)約束

實(shí)現(xiàn)約束必須準(zhǔn)確反映最終應(yīng)用的要求。物理約束(例如 I/O 位置和 I/O 標(biāo)準(zhǔn))取決于開(kāi)發(fā)板設(shè)計(jì)(包括開(kāi)發(fā)板走線延遲)以及源自總體系統(tǒng)要求的設(shè)計(jì)內(nèi)部要求。物理約束就是對(duì)管腳進(jìn)行約束,包括管腳位置和電壓配置等。

多數(shù)情況下,在綜合與實(shí)現(xiàn)階段可以使用相同的約束。但是,由于設(shè)計(jì)對(duì)象在綜合階段可能消失或發(fā)生名稱變化,因此必須確認(rèn)所有綜合約束都可正確應(yīng)用于實(shí)現(xiàn)網(wǎng)表。

(6)創(chuàng)建塊級(jí)約束

開(kāi)發(fā)多團(tuán)隊(duì)工程時(shí),為方便起見(jiàn),可為頂層設(shè)計(jì)的每個(gè)主要塊創(chuàng)建獨(dú)立的約束文件。通常每個(gè)主要塊都會(huì)先獨(dú)立開(kāi)發(fā)并驗(yàn)證,最后再整合到 1 個(gè)或多個(gè)頂層設(shè)計(jì)中。

塊級(jí)約束必須獨(dú)立于頂層約束單獨(dú)開(kāi)發(fā),并且必須盡可能采用通用設(shè)計(jì)以便應(yīng)用于各種環(huán)境中。此外,這些約束不得影響塊邊界外的任何邏輯。

當(dāng)實(shí)現(xiàn)子塊時(shí),最好在時(shí)序分析中包含全時(shí)鐘網(wǎng)絡(luò),以確保偏差和時(shí)鐘域交匯分析的準(zhǔn)確性。這可能需要 1 個(gè)包含時(shí)鐘組件的 HDL 封裝器和另一個(gè)約束文件以便復(fù)制頂層時(shí)鐘約束。它僅用于子模塊的時(shí)序驗(yàn)證。

這么做的主要原因,我們可以將其叫做“去耦合”,保持相對(duì)獨(dú)立性。

5.2 定義時(shí)序約束的四個(gè)步驟

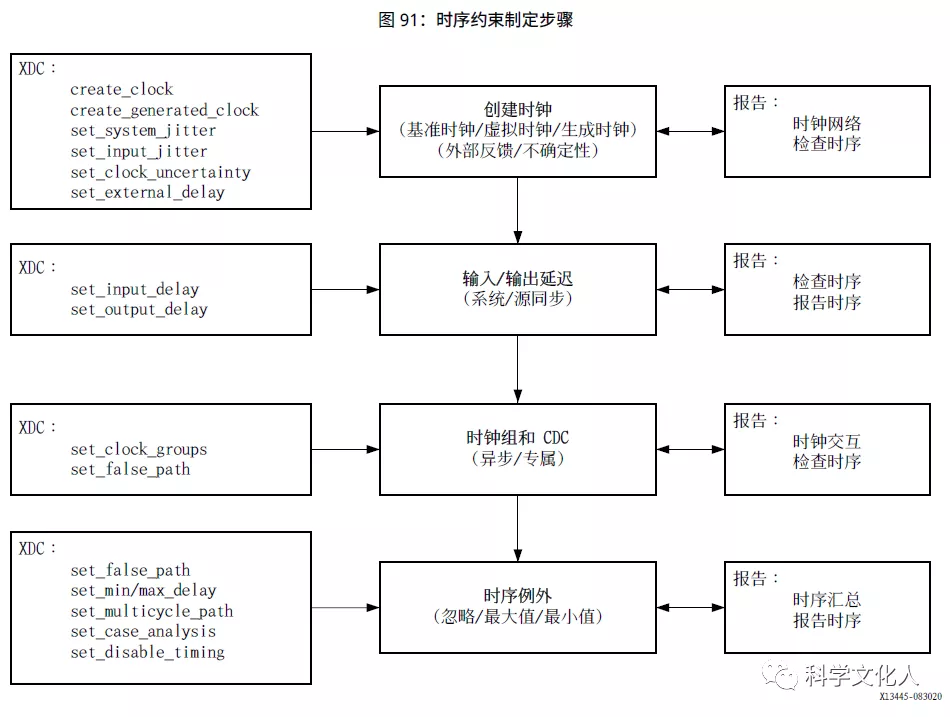

合格的約束的定義過(guò)程分為四個(gè)主要步驟,如下圖所示。這些步驟遵循時(shí)序約束先后順序和從屬關(guān)系規(guī)則,并采用符合邏輯的方式來(lái)向時(shí)序引擎提供信息以執(zhí)行分析。

? 前 2 個(gè)步驟與時(shí)序斷言有效有關(guān),期間將從時(shí)鐘波形和 I/O 延遲約束中衍生出默認(rèn)時(shí)序路徑要求。

? 在第 3 個(gè)步驟中,將對(duì)至少共享 1 條邏輯路徑的異步或?qū)贂r(shí)鐘域之間的關(guān)系進(jìn)行審核。根據(jù)關(guān)系的性質(zhì),可輸入時(shí)鐘組或偽路徑約束以忽略這些路徑上的時(shí)序分析。

? 最后一個(gè)步驟對(duì)應(yīng)于時(shí)序例外,設(shè)計(jì)人員可在此判定如何更改默認(rèn)時(shí)序路徑要求,包括利用特定約束來(lái)忽略、放寬或收緊時(shí)序要求。

從邏輯上講,完成這四步,我們的時(shí)序約束就完成了。關(guān)于這四步詳細(xì)的約束文件創(chuàng)建,可參考UG949第四章的4.3節(jié)至4.6節(jié)。另外,針對(duì)多周期路徑約束和物理約束,可參考4.7和4.8節(jié)。

設(shè)計(jì)實(shí)現(xiàn)

選定器件、選擇并配置 IP 且編寫(xiě) RTL 和約束條件后,下一步即為實(shí)現(xiàn)。實(shí)現(xiàn)通過(guò)綜合和布局布線來(lái)編譯設(shè)計(jì),然后生

成用于對(duì)器件進(jìn)行編程的文件。實(shí)現(xiàn)過(guò)程可能包含一些迭代循環(huán)。

6.1 運(yùn)行綜合

綜合步驟將采用 RTL 和時(shí)序約束,并生成功能上等同于 RTL 的最優(yōu)化網(wǎng)表。通常,綜合工具可以采用任何合法 RTL,并為其創(chuàng)建邏輯。綜合需要現(xiàn)實(shí)的時(shí)序約束。

(1)綜合流程

a.全局綜合

在全局綜合流程中,整個(gè)設(shè)計(jì)通過(guò)單次運(yùn)行來(lái)完成綜合,其優(yōu)勢(shì)如下:

? 允許綜合工具執(zhí)行最大程度地最優(yōu)化。由于綜合工具已發(fā)現(xiàn)整個(gè)設(shè)計(jì),該工具可在層級(jí)間進(jìn)行最優(yōu)化,這是其它流

程無(wú)法做到的。

? 簡(jiǎn)化綜合運(yùn)行后的分析操作。

此流程的缺點(diǎn)在于編譯時(shí)間較長(zhǎng)。每次運(yùn)行綜合后,都會(huì)重新運(yùn)行整個(gè)設(shè)計(jì)。但可通過(guò)使用增量綜合來(lái)緩解此缺點(diǎn)的不

利影響。

b.非關(guān)聯(lián)綜合

在非關(guān)聯(lián)綜合流程中,某些層級(jí)與頂層分離,單獨(dú)進(jìn)行綜合。非關(guān)聯(lián)層級(jí)首先進(jìn)行綜合。然后,運(yùn)行頂層綜合,并且每次非關(guān)聯(lián)運(yùn)行都作為黑盒來(lái)處理。這就是我們所說(shuō)的OOC綜合方式,通常對(duì)IP和無(wú)需改動(dòng)的模塊采用這種方式。

此流程具有以下優(yōu)點(diǎn):

?縮短后續(xù)綜合運(yùn)行的編譯時(shí)間。僅對(duì)您指定的運(yùn)行進(jìn)行重新綜合,其它運(yùn)行保持不變。?確保進(jìn)行設(shè)計(jì)更改時(shí)的穩(wěn)定性。僅對(duì)包含更改的運(yùn)行進(jìn)行重新綜合。

此流程的缺點(diǎn)在于需要額外進(jìn)行設(shè)置。您必須謹(jǐn)慎選擇將哪些模塊設(shè)置為非關(guān)聯(lián)綜合模塊。任何額外 XDC 約束都必須單獨(dú)定義,并且僅限用于非關(guān)聯(lián)綜合運(yùn)行。

c.塊設(shè)計(jì)綜合

塊設(shè)計(jì)綜合流程支持您使用定制 IP 和賽靈思 IP 創(chuàng)建復(fù)雜系統(tǒng)。在此流程中,將使用 Vivado IP integrator 創(chuàng)建塊設(shè)計(jì)(BD) 文件。賽靈思 IP 或定制 IP 將被添加到此 .bd 文件中并作為系統(tǒng)進(jìn)行連接。此流程具有以下優(yōu)點(diǎn):

? 將大量功能封裝到小型設(shè)計(jì)中。

? 支持集中精力處理整個(gè)系統(tǒng),而不是系統(tǒng)的各部分。

? 簡(jiǎn)化并加速設(shè)計(jì)的設(shè)置和綜合。

塊設(shè)計(jì)中,主要涉及調(diào)用處理器,設(shè)計(jì)完成后,一般不會(huì)再去修改,在頂層文件中直接調(diào)用。

d.增量綜合流程

您可使用增量綜合來(lái)復(fù)用現(xiàn)有綜合結(jié)果。此方法具有以下優(yōu)點(diǎn):

? 將典型綜合編譯時(shí)間縮短 50%。

? 配合增量實(shí)現(xiàn)流程一起使用時(shí),可縮短總體編譯時(shí)間并提升時(shí)序收斂一致性。

當(dāng)頂層設(shè)計(jì)為 RTL 并且 RTL 在設(shè)計(jì)中所占比重較大時(shí),增量綜合將具有最高的價(jià)值。在此模式下,綜合編譯時(shí)間將得到最優(yōu)化,并將復(fù)用結(jié)果。對(duì)于包含大量塊設(shè)計(jì)和/或 IP 的設(shè)計(jì),Vivado Design Suite 會(huì)在這些塊上自動(dòng)拆分綜合,并以非關(guān)聯(lián)模式運(yùn)行綜合。因此,增量綜合對(duì)這些設(shè)計(jì)的價(jià)值較小。

增量綜合可通過(guò)復(fù)用來(lái)自參考綜合運(yùn)行的未經(jīng)修改的層級(jí)來(lái)縮短編譯時(shí)間。要使增量綜合發(fā)揮作用,設(shè)計(jì)必須包含至少5 個(gè)分區(qū),每個(gè)分區(qū)至少 10,000 個(gè)實(shí)例。此外,必須盡可能減少任何設(shè)計(jì)更改所影響的分區(qū)數(shù)量,并且不得在設(shè)計(jì)頂層執(zhí)行更改。

注意:某些更改可能會(huì)影響跨邊界最優(yōu)化,從而導(dǎo)致其它分區(qū)需要重新進(jìn)行綜合。

所以,當(dāng)改動(dòng)很小,不影響跨邊界優(yōu)化時(shí),可采用增量綜合。

(2)綜合最優(yōu)化

默認(rèn)情況下,Vivado 綜合將應(yīng)用能夠?yàn)樽畲罅康脑O(shè)計(jì)產(chǎn)生最佳結(jié)果的最優(yōu)化措施。大部分情況下,我們都按默認(rèn)綜合進(jìn)行優(yōu)化,當(dāng)然,也可根據(jù)實(shí)際需要進(jìn)行綜合設(shè)置。

很多時(shí)候,我們比較關(guān)注有些關(guān)鍵信號(hào)是否被優(yōu)化掉,需要使用相關(guān)綜合屬性。使用 KEEP、DONT_TOUCH 和 MAX_FANOUT 屬性時(shí),需要特別注意對(duì)綜合帶來(lái)的影響。

6.2 綜合后的步驟

確保綜合過(guò)程中您已獲得的網(wǎng)表質(zhì)量?jī)?yōu)良,這樣它就不會(huì)在下游造成問(wèn)題。

(1)檢查和清理 DRC

report_drc 命令可運(yùn)行設(shè)計(jì)規(guī)則檢查 (DRC) 以尋找常見(jiàn)設(shè)計(jì)問(wèn)題和錯(cuò)誤。默認(rèn)規(guī)則檢查如下:

? 綜合后網(wǎng)表

? I/O、BUFG 和其它特定的布局需求。

? 屬性和 MGT、IODELAY、MMCM、PLL 的連線以及其它原語(yǔ)。

(2)運(yùn)行 Report Methodology

Vivado 工具中提供了“方法論報(bào)告 (Report Methodology)”,專用于檢查是否符合方法論指南要求。這些工具根據(jù)所處的設(shè)計(jì)進(jìn)程階段運(yùn)行不同的檢查。

? RTL 設(shè)計(jì):RTL lint 風(fēng)格檢查

? 綜合設(shè)計(jì)和實(shí)現(xiàn)設(shè)計(jì):網(wǎng)表、約束和時(shí)序檢查。

(3)復(fù)查綜合日志

必須復(fù)查綜合日志文件并確認(rèn)該工具提供的所有消息與您期望的設(shè)計(jì)用途相匹配。請(qǐng)?zhí)貏e關(guān)注“嚴(yán)重警告 (CriticalWarnings)”和“警告 (Warnings)”。大多數(shù)情況下,需修復(fù)“嚴(yán)重警告 (Critical Warnings)”才能實(shí)現(xiàn)可靠的綜合結(jié)果。

通常,在消息欄會(huì)給出錯(cuò)誤或警告提示,對(duì)于嚴(yán)重警告,必須進(jìn)行修復(fù)。

(4)檢查時(shí)序約束

您必須提供簡(jiǎn)單標(biāo)準(zhǔn)的時(shí)序約束以及時(shí)序例外(如果適用)。錯(cuò)誤的約束將導(dǎo)致編譯時(shí)間過(guò)長(zhǎng)、性能問(wèn)題以及硬件故障。

6.3 實(shí)現(xiàn)設(shè)計(jì)

Vivado Design Suite 實(shí)現(xiàn)包括在器件資源上對(duì)網(wǎng)表進(jìn)行布局布線,同時(shí)滿足設(shè)計(jì)的邏輯、物理和時(shí)序約束所需的所有步驟。

通常,我們使用默認(rèn)的實(shí)現(xiàn)策略,主要有以下三個(gè)過(guò)程:

? opt_design

? place_design

? route_design

在 Vivado Design Suite 中,可以使用增量實(shí)現(xiàn)來(lái)復(fù)用現(xiàn)有布局和布線數(shù)據(jù),從而縮短實(shí)現(xiàn)的編譯時(shí)間,并提升結(jié)果的可預(yù)測(cè)性。當(dāng)所處理的設(shè)計(jì)復(fù)用比例達(dá)到甚至超過(guò) 95% 時(shí),增量布局和布線編譯時(shí)間通常僅為正常布局和布線運(yùn)行時(shí)間的一半甚至更短,同時(shí)參考運(yùn)行的 WNS 仍保持不變。

設(shè)計(jì)收斂

設(shè)計(jì)收斂包括滿足所有時(shí)序、系統(tǒng)性能和功耗要求,并成功驗(yàn)證硬件中的功能。設(shè)計(jì)收斂通常需要在結(jié)果分析、設(shè)計(jì)修改和約束修改之間進(jìn)行幾次迭代。

7.1 時(shí)序收斂

時(shí)序收斂是指設(shè)計(jì)滿足所有的時(shí)序要求。針對(duì)綜合采用正確的 HDL 和約束條件就能更易于實(shí)現(xiàn)時(shí)序收斂。

要成功完成時(shí)序收斂,遵循下列常規(guī)準(zhǔn)則進(jìn)行操作:

? 最初不能滿足時(shí)序要求時(shí),請(qǐng)?jiān)谡麄€(gè)流程中評(píng)估時(shí)序。

? 集中精力解決每個(gè)時(shí)鐘的最差負(fù)時(shí)序裕量 (WNS) 是改進(jìn)總體時(shí)序負(fù)裕量 (TNS) 的主要途徑。

? 復(fù)查嚴(yán)重的最差保持時(shí)序裕量 (WHS) 違例 ( ? 重新評(píng)估設(shè)計(jì)選擇、約束和目標(biāo)架構(gòu)之間的利弊取舍。

? 了解如何使用工具選項(xiàng)和賽靈思設(shè)計(jì)約束 (XDC)。

? 請(qǐng)注意,滿足時(shí)序要求后,工具就不會(huì)再嘗試進(jìn)一步改進(jìn)時(shí)序(額外裕度)。

在實(shí)現(xiàn)完成后,會(huì)產(chǎn)生時(shí)序報(bào)告,要特別關(guān)注最差負(fù)時(shí)序裕量 (WNS)和總體時(shí)序負(fù)裕量 (TNS),需要檢查正時(shí)序裕量。

以下是指示存在時(shí)序違例的時(shí)序指標(biāo)。為了滿足時(shí)序要求,數(shù)字必須為正。

? 建立/恢復(fù)(最大延遲分析):WNS > 0 ns 且 TNS = 0 ns

? 保持/移除(最小延遲分析):WHS > 0 ns 且 THS = 0 ns

? 脈沖寬度:WPWS > 0 ns 且 TPWS = 0 ns

7.2 功耗分析與最優(yōu)化

鑒于功耗的重要性,Vivado 工具支持采用各種方法來(lái)獲取準(zhǔn)確的功耗估算以及各種功耗最優(yōu)化功能。

(1)估算整個(gè)流程的功耗

隨著設(shè)計(jì)流程進(jìn)入綜合與實(shí)現(xiàn)階段,必須定期監(jiān)控和檢查功耗以確保熱耗散保持在預(yù)算范圍內(nèi)。一旦功耗與預(yù)算值過(guò)于接近就可及時(shí)采取補(bǔ)救措施。

使用下列 XDC 約束指定功耗預(yù)算,以報(bào)告功耗裕度:

set_operating_conditions -design_power_budget

該值供 report_power 命令使用。計(jì)算所得片上功耗與功耗預(yù)算之差即為功耗裕度,超出功耗預(yù)算時(shí),該值在Vivado IDE 中將以紅色顯示。這樣更便于監(jiān)控整個(gè)流程中的功耗狀況。

功耗估算的精確性因估算時(shí)的設(shè)計(jì)階段而異。要通過(guò)實(shí)現(xiàn)來(lái)估算綜合后功耗,請(qǐng)運(yùn)行 report_power 命令,或者在Vivado IDE 中打開(kāi)“Power Report”。

(2)功耗最優(yōu)化

如果功耗估算超出預(yù)算,那么必要采取措施來(lái)降低功耗。

a.分析功耗估算和最優(yōu)化結(jié)果

使用 report_power 生成功耗估算報(bào)告后,賽靈思建議執(zhí)行以下操作:

? 在“Summary”部分中檢查總功耗。總功耗和結(jié)溫是否符合熱處理與功耗預(yù)算?

? 如果結(jié)果嚴(yán)重超出預(yù)算,應(yīng)根據(jù)塊類型和電源軌檢查功耗分布匯總情況。這樣便于您了解哪些塊功耗最高。

? 復(fù)查“Hierarchy”部分。按層級(jí)細(xì)分后,功耗最高的模塊將清晰可見(jiàn)。您可深入查看具體模塊,以確定塊的功能。

也可以在 GUI 中進(jìn)行交叉探測(cè),以確定模塊特定部分的編碼方式以及是否可通過(guò)能效更高的方法對(duì)其進(jìn)行重新編碼。

b.運(yùn)行功耗最優(yōu)化

功耗最優(yōu)化適用于整體設(shè)計(jì)或部分設(shè)計(jì)(使用set_power_opt),用于最大限度降低功耗。

c.使用功耗最優(yōu)化報(bào)告

為確定功耗最優(yōu)化的影響,在 Tcl 控制臺(tái)中運(yùn)行如下命令以生成功耗最優(yōu)化報(bào)告:

report_power_opt -file myopt.rep

7.3 配置與調(diào)試

成功完成設(shè)計(jì)實(shí)現(xiàn)后,下一步就是將設(shè)計(jì)加載到器件中并在硬件上運(yùn)行。配置是指將特定應(yīng)用的數(shù)據(jù)加載到器件內(nèi)部存儲(chǔ)器中的過(guò)程。

(1)配置

必須首先成功完成設(shè)計(jì)綜合與實(shí)現(xiàn),然后才能創(chuàng)建比特流鏡像。生成比特流并且對(duì)所有 DRC 都完成分析和更正后,即可使用以下任一方法將比特流加載到器件上:

? 直接編程:

通過(guò)線纜、處理器或定制解決方案將比特流直接加載到器件。

? 間接編程:將比特流加載到外部閃存。閃存再將比特流加載到器件。

可使用 Vivado 工具來(lái)完成下列操作:

? 創(chuàng)建比特流(.bit 或 .rbt)。

? 可選擇“Tools” → “Edit Device”以復(fù)查比特流生成的配置設(shè)置。

? 將比特流格式化為閃存編程文件 (.mcs)。

(2)調(diào)試

系統(tǒng)內(nèi)調(diào)試允許您在目標(biāo)器件上實(shí)時(shí)調(diào)試設(shè)計(jì)。遇到幾乎無(wú)法復(fù)制仿真器的情況時(shí),就需要執(zhí)行此步驟。在上板調(diào)試前,最好先對(duì)工程進(jìn)行仿真,起碼的功能驗(yàn)證要通過(guò),不然調(diào)試的結(jié)果并不理想。

調(diào)試步驟如下所述:

1. 探測(cè):確定設(shè)計(jì)中要探測(cè)的信號(hào)和探測(cè)的方法。

2. 實(shí)現(xiàn):完成設(shè)計(jì)實(shí)現(xiàn),包括連接到所探測(cè)的信號(hào)線上的其它調(diào)試 IP。

3. 分析:與設(shè)計(jì)中包含的調(diào)試 IP 進(jìn)行交互,以便對(duì)功能問(wèn)題進(jìn)行調(diào)試和驗(yàn)證。

4. 修復(fù)相位:修復(fù)所有缺陷,此步驟可按需重復(fù)。

a.使用ILA核

通常,我們會(huì)使用ILA核對(duì)待觀察信號(hào)進(jìn)行探測(cè),捕獲波形和數(shù)據(jù),進(jìn)行量化,導(dǎo)出.csv數(shù)據(jù)到MATLAB進(jìn)行數(shù)據(jù)分析。

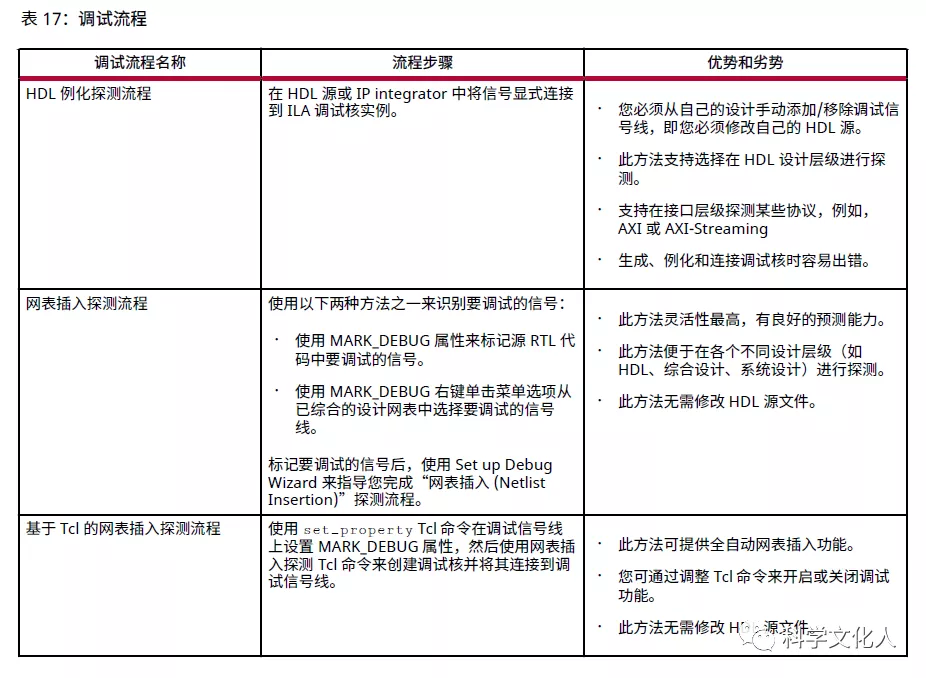

Vivado 工具提供了多種方法用于在設(shè)計(jì)中添加調(diào)試探針。下表逐一解釋了這些方法,并介紹每種方法各自的優(yōu)劣。

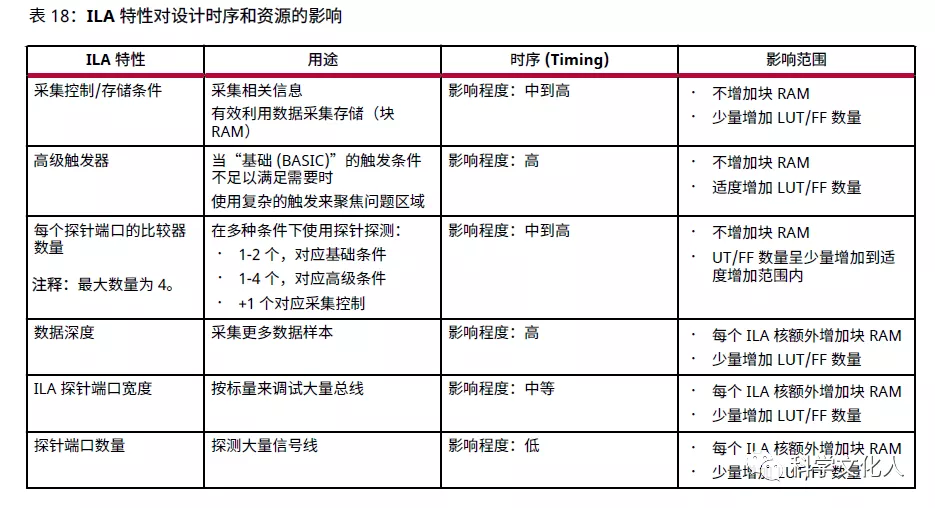

注意,ILA 核的配置會(huì)對(duì)能否滿足整體設(shè)計(jì)時(shí)序目標(biāo)產(chǎn)生影響。請(qǐng)根據(jù)下列建議進(jìn)行操作,以便最大程度減少對(duì)時(shí)序的影響:

? 請(qǐng)審慎選擇探針寬度。隨探針寬度增加,對(duì)資源利用率和時(shí)序的影響也會(huì)增大。

? 請(qǐng)審慎選擇 ILA 核數(shù)據(jù)深度。隨數(shù)據(jù)深度增加,對(duì)塊 RAM 資源利用率和時(shí)序的影響也會(huì)增大。

? 請(qǐng)確保為 ILA 核選擇的時(shí)鐘均為自由運(yùn)行的時(shí)鐘。否則可能造成在器件上加載設(shè)計(jì)時(shí)無(wú)法與調(diào)試核通信。

? 請(qǐng)確保提供給 dbg_hub 的時(shí)鐘為自由運(yùn)行的時(shí)鐘。否則可能造成在器件上加載設(shè)計(jì)時(shí)無(wú)法與調(diào)試核通信。可使用

connect_debug_port Tcl 命令將調(diào)試中心的 clk 管腳連接到自由運(yùn)行的時(shí)鐘。

? 在添加調(diào)試核之前完成設(shè)計(jì)上的時(shí)序收斂。賽靈思不建議使用調(diào)試核來(lái)調(diào)試時(shí)序相關(guān)問(wèn)題。

? 如果仍發(fā)現(xiàn)因添加 ILA 調(diào)試核而導(dǎo)致時(shí)序劣化,并且關(guān)鍵路徑位于 dbg_hub 中,請(qǐng)執(zhí)行以下步驟:

1. 打開(kāi)綜合設(shè)計(jì)。

2. 找到網(wǎng)表中的 dbg_hub 單元。

3. 轉(zhuǎn)至 dbg_hub 的“Properties”選項(xiàng)卡。

4. 找到 C_CLK_INPUT_FREQ_HZ 屬性。

5. 將其設(shè)置為鏈接到 dbg_hub 的時(shí)鐘頻率 (Hz)。

6. 找到 C_ENABLE_CLK_DIVIDER 屬性并將其啟用。

7. 重新執(zhí)行設(shè)計(jì)實(shí)現(xiàn)。

? 請(qǐng)確保輸入到 ILA 核的時(shí)鐘與正在探測(cè)的信號(hào)同步。否則在設(shè)計(jì)編程到器件中時(shí)會(huì)產(chǎn)生時(shí)序問(wèn)題并導(dǎo)致通信失敗。

? 在硬件上運(yùn)行設(shè)計(jì)之前請(qǐng)確保設(shè)計(jì)已滿足時(shí)序要求。否則會(huì)導(dǎo)致探測(cè)到的波形不可靠。

下表列出了在設(shè)計(jì)時(shí)序和資源時(shí)使用特定 ILA 特性的影響。

對(duì)于高速時(shí)鐘設(shè)計(jì),請(qǐng)注意如下事項(xiàng):

? 限制調(diào)試的信號(hào)數(shù)量和寬度。

? 將輸入探針通過(guò)流水線輸送到 ILA (C_INPUT_PIPE_STAGES),可增加流水線階段的層級(jí)。

b.使用VIO核

Virtual Input/Output (VIO) 核支持實(shí)時(shí)監(jiān)控和驅(qū)動(dòng)內(nèi)部器件信號(hào)。如果需要啟動(dòng)或監(jiān)控低速信號(hào)(如復(fù)位信號(hào)或狀態(tài)信號(hào)),請(qǐng)使用此核。VIO 調(diào)試核必須在設(shè)計(jì)中例化,并且可在 Vivado IP integrator 塊和 RTL 中使用。在 IP 目錄中包含 VIO 核,可在基于 RTL 的設(shè)計(jì)和 IP integrator 中使用。

關(guān)于UltraFast設(shè)計(jì)方法論中的主要內(nèi)容,就到此結(jié)束了,里面還有更詳細(xì)的描述,有助于FPGA工程師進(jìn)行更好的工程設(shè)計(jì)。總結(jié)一下:

(1)我們初步了解了什么是UlraFast設(shè)計(jì)方法論,及其包含的設(shè)計(jì)目與主要內(nèi)容;

(2)重要參考文檔有:UG949、UG1231、UG1292、UG1046、UG835、UG903等;

(3)我們重點(diǎn)學(xué)習(xí)了利用RTL創(chuàng)建設(shè)計(jì)、如何進(jìn)行設(shè)計(jì)約束、如何設(shè)計(jì)實(shí)現(xiàn)以及如何實(shí)現(xiàn)設(shè)計(jì)收斂;

(4)設(shè)計(jì)方法論可進(jìn)行實(shí)踐指導(dǎo),我們?cè)诰唧w工程項(xiàng)目中,需要靈活使用這些設(shè)計(jì)方法,以便高效設(shè)計(jì),進(jìn)而縮短開(kāi)發(fā)周期,盡快推出產(chǎn)品。

后記:

花了一天的時(shí)間,粗略地把UltraFast設(shè)計(jì)方法過(guò)了一遍,說(shuō)實(shí)話,挺累的。看文獻(xiàn)和碼字,除了體力勞動(dòng),還有腦力勞動(dòng)。不管你能不能看懂,總會(huì)有一點(diǎn)點(diǎn)收獲吧。

歡迎大家留言,如果覺(jué)得有所幫助,那今天的勞動(dòng)也沒(méi)有白費(fèi),你說(shuō)呢。

參考文獻(xiàn)

[1]Xilinx ,《UltraFast設(shè)計(jì)方法指南》(UG949)。

審核編輯:符乾江

-

FPGA

+關(guān)注

關(guān)注

1643文章

21985瀏覽量

615092 -

編程

+關(guān)注

關(guān)注

88文章

3686瀏覽量

94951

發(fā)布評(píng)論請(qǐng)先 登錄

硬件工程師看了只會(huì)找個(gè)角落默默哭泣#硬件工程師 #MDD #MDD辰達(dá)半導(dǎo)體 #產(chǎn)品經(jīng)理 #軟件工程師

機(jī)械工程師的九個(gè)段位,你現(xiàn)在處于哪一層?

物聯(lián)網(wǎng)工程師為什么要學(xué)Linux?

電子工程師自學(xué)速成 —— 提高篇

電子工程師自學(xué)速成——入門篇

【社區(qū)之星】張飛:做技術(shù)值不值錢,核心競(jìng)爭(zhēng)力在于精

嵌入式軟件工程師就業(yè)好不好?

如何成為嵌入式開(kāi)發(fā)工程師?

芯和半導(dǎo)體榮獲2024上海軟件核心競(jìng)爭(zhēng)力企業(yè)

中國(guó)AI企業(yè)創(chuàng)新降低成本打造競(jìng)爭(zhēng)力模型

Keysight助力提升工程師的測(cè)試測(cè)量知識(shí)水平

硬件工程師VS軟件工程師|硬件工程師看到這都淚目了!#硬件設(shè)計(jì) #硬件工程師 #電子工程師 #軟件工程師

FPGA算法工程師、邏輯工程師、原型驗(yàn)證工程師有什么區(qū)別?

學(xué)習(xí)SOLIDWORKS提高學(xué)生的就業(yè)競(jìng)爭(zhēng)力

FPGA工程師的核心競(jìng)爭(zhēng)力 — 方法篇(二)

FPGA工程師的核心競(jìng)爭(zhēng)力 — 方法篇(二)

評(píng)論