近日獲悉,華為日前又公開了2項(xiàng)芯片相關(guān)的發(fā)明專利。“一種多芯片堆疊封裝及制作方法”和“芯片堆疊封裝結(jié)構(gòu)及其封裝方法、電子設(shè)備”。。。

華為此前4月5日公開“一種芯片堆疊封裝及終端設(shè)備”專利引起了廣泛關(guān)注,也透露了其從2019年就對(duì)芯片堆疊技術(shù)進(jìn)行布局。近日,華為又公開了2項(xiàng)芯片相關(guān)的發(fā)明專利。

國際電子商情9日國家知識(shí)產(chǎn)權(quán)局網(wǎng)站查詢發(fā)現(xiàn),華為公開了申請(qǐng)的2項(xiàng)芯片相關(guān)專利——“一種多芯片堆疊封裝及制作方法”和“芯片堆疊封裝結(jié)構(gòu)及其封裝方法、電子設(shè)備”,申請(qǐng)公布號(hào)分別為CN114450785A和CN114450786A。

圖源:國家知識(shí)產(chǎn)權(quán)局網(wǎng)站(下同)

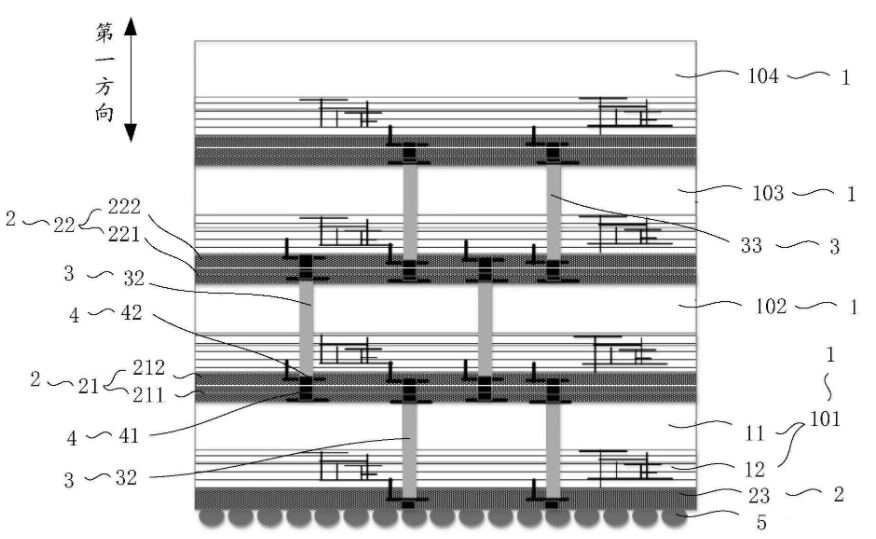

“一種多芯片堆疊封裝及制作方法”

據(jù)公開的專利摘要顯示,該專利涉及芯片技術(shù)領(lǐng)域,不僅能夠解決多芯片的應(yīng)力集中問題,還能夠以進(jìn)行更多層芯片的堆疊。

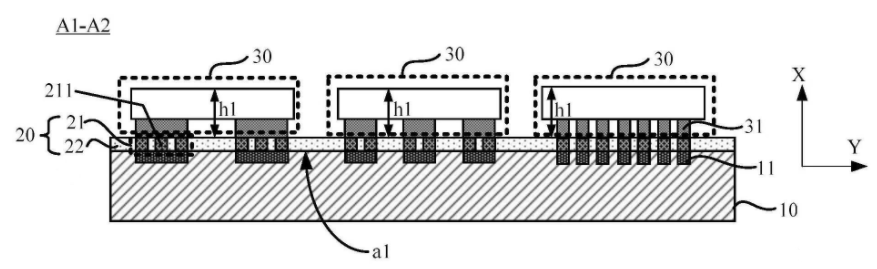

“芯片堆疊封裝結(jié)構(gòu)及其封裝方法、電子設(shè)備”

專利摘要顯示,該專利為一種芯片堆疊封裝結(jié)構(gòu)(100)及其封裝方法、電子設(shè)備(1),涉及電子技術(shù)領(lǐng)域,用于解決如何將多個(gè)副芯片堆疊單元(30)可靠的鍵合在同一主芯片堆疊單元(10)上的問題。

布局造芯已久

雖然本次公開的兩項(xiàng)專利與4月5日公開專利申請(qǐng)時(shí)間均為2019年,但早在2012年,華為便向國家知識(shí)產(chǎn)權(quán)局申請(qǐng)了一項(xiàng)名為“芯片堆疊封裝結(jié)構(gòu)”的發(fā)明專利。這意味著,華為對(duì)芯片堆疊封裝的研究在2012年甚至更早的時(shí)間就已開始。而華為官方首次公開確認(rèn)芯片堆疊技術(shù)則是在今年3月28日舉行的華為2021年年報(bào)發(fā)布會(huì)上。華為輪值董事長(zhǎng)郭平當(dāng)時(shí)表示,未來華為可能會(huì)采用多核結(jié)構(gòu)的芯片設(shè)計(jì)方案,以提升芯片性能,同時(shí)采用面積換性能,用堆疊換性能,使得不那么先進(jìn)的工藝也能持續(xù)讓華為在未來的產(chǎn)品里面,能夠具有競(jìng)爭(zhēng)力。

關(guān)于芯片堆疊技術(shù):1+1不一定等于2!

國際電子商情了解到,堆疊技術(shù)也可以叫做3D堆疊技術(shù),是利用堆疊技術(shù)或通過互連和其他微加工技術(shù)在芯片或結(jié)構(gòu)的Z軸方向上形成三維集成,信號(hào)連接以及晶圓級(jí),芯片級(jí)和硅蓋封裝具有不同的功能,針對(duì)包裝和可靠性技術(shù)的三維堆疊處理技術(shù)。

該技術(shù)用于微系統(tǒng)集成,是在片上系統(tǒng)(SOC)和多芯片模塊(MCM)之后開發(fā)的先進(jìn)的系統(tǒng)級(jí)封裝制造技術(shù)。 在傳統(tǒng)的SiP封裝系統(tǒng)中,任何芯片堆棧都可以稱為3D,因?yàn)樵赯軸上功能和信號(hào)都有擴(kuò)展,無論堆棧位于IC內(nèi)部還是外部。

目前,3D芯片技術(shù)的類別包括:基于芯片堆疊的3D技術(shù),基于有源TSV的3D技術(shù),基于無源TSV的3D技術(shù),以及基于芯片制造的3D技術(shù)。目前臺(tái)積電、英特爾、三星等國際半導(dǎo)體廠商都開發(fā)了自己的3D芯片封裝技術(shù)。

-

華為

+關(guān)注

關(guān)注

216文章

35070瀏覽量

255210 -

芯片堆疊

+關(guān)注

關(guān)注

0文章

19瀏覽量

14702

發(fā)布評(píng)論請(qǐng)先 登錄

華為公布兩項(xiàng)關(guān)于芯片堆疊技術(shù)專利

華為公布兩項(xiàng)關(guān)于芯片堆疊技術(shù)專利

評(píng)論