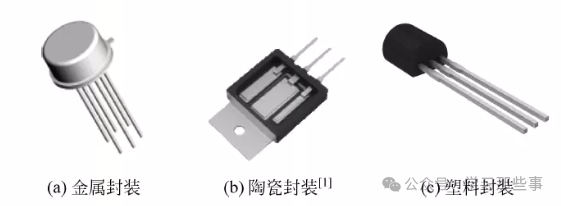

隨著科技的發展,全球的芯片封裝工藝正在由雙列直插的通孔插裝型,逐漸轉向金譽半導體今天要講的表面貼裝的封裝形式(SMT)。

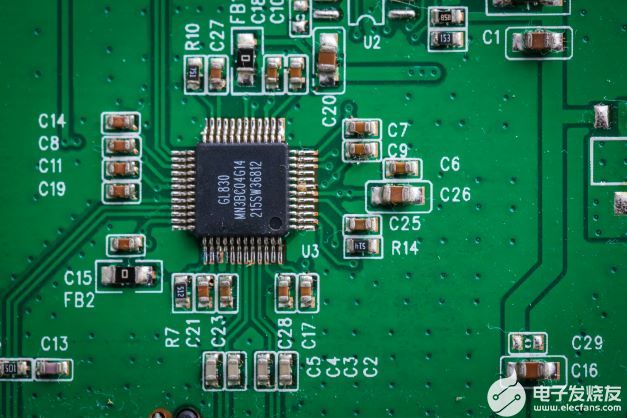

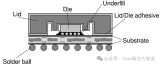

SMT是表?貼裝技術(表?組裝技術)(Surface Mounted Technology的縮寫),是電?組裝?業?最流?的?種技術和工藝。電?電路表?組裝技術(Surface Mount Technology,SMT),稱為表?貼裝或表?安裝技術。它是?種將無引腳或短引線表?組裝元器件(簡稱SMC/SMD,中?稱?狀元器件)安裝在印制電路板(Printed Circuit Board,PCB)的表?或其它基板的表?上,通過再流焊或浸焊等?法加以焊接組裝的電路裝連技術。

區別于傳統的封裝形式,今天要聊的SMT(表?貼裝技術),對芯片封裝難度更大,要求更嚴,技術更嚴苛的封裝形式,包括晶圓級封裝(WLP)、三維封裝(3DP)和系統級封裝(SiP)三種。

什么是晶圓級封裝(WLP)?

晶圓級封裝(Wafer Level Packaging,縮寫WLP)是一種先進的封裝技術,因其具有尺寸小、電性能優良、散熱好、成本低等優勢,近年來發展迅速。

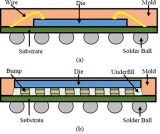

不同于傳統封裝工藝,晶圓級封裝是在芯片還在晶圓上的時候就對芯片進行封裝,保護層可以黏接在晶圓的頂部或底部,然后連接電路,再將晶圓切成單個芯片。

相比于傳統封裝,晶圓級封裝具有以下優點:

1.封裝尺寸小

由于沒有引線、鍵合和塑膠工藝,封裝無需向芯片外擴展,使得WLP的封裝尺寸幾乎等于芯片尺寸。

2.高傳輸速度

與傳統金屬引線產品相比,WLP一般有較短的連接線路,在高效能要求如高頻下,會有較好的表現。

3.高密度連接

WLP可運用數組式連接,芯片和電路板之間連接不限制于芯片四周,提高單位面積的連接密度。

4.生產周期短

WLP從芯片制造到、封裝到成品的整個過程中,中間環節大大減少,生產效率高,周期縮短很多。

5.工藝成本低

WLP是在硅片層面上完成封裝測試的,以批量化的生產方式達到成本最小化的目標。WLP的成本取決于每個硅片上合格芯片的數量,芯片設計尺寸減小和硅片尺寸增大的發展趨勢使得單個器件封裝的成本相應地減少。WLP可充分利用晶圓制造設備,生產設施費用低。

目前,晶圓級封裝技術已廣泛用于閃速存儲器、EEPROM、高速DRAM、SRAM、LCD驅動器、射頻器件、邏輯器件、電源/電池管理器件和模擬器件(穩壓器、溫度傳感器、控制器、運算放大器、功率放大器)等領域。

什么是三維封裝(3DP)?

三維封裝,英文簡稱(3DP),包括CIS發射器、MEMS封裝、標準器件封裝。是指在不改變封裝體尺寸的前提下,在同一個封裝體內于垂直方向疊放兩個以上芯片的封裝技術,從而實現大芯片的的功能和性能。它起源于快閃存儲器(NOR/NAND)及SDRAM的疊層封裝。

主要特點包括:多功能、高效能;大容量高密度,單位體積上的功能及應用成倍提升以及低成本。

什么是系統級封裝(SiP)?

系統級封裝,將多種功能芯片(包括處理器、存儲器等)集成在一個封裝內,集成組裝成為具有多層器件結構,并且可以提供多種功能的單個標準封裝件,形成一個系統或者子系統,以實現更高的性能、功能和處理速度,同時大幅降低電子器件內部的空間要求。即達到所謂的Convergent System的電子系統水平。

系統級封裝包含兩個非常重要的特征:

(1)將各種不同工藝、不同功能的芯片集成在一個封裝內實現強大的系統功能;

(2)將過去PCB版上的分立元件集成在多層集成結構中,使系統小型化,達到所謂的Convergent System 。

封裝主要是為了實現芯片內部和外部電路之間的連接和保護作用。這三種較為先進的封裝形式各有千秋,應用場合也有所不同,雖目前并未普及,但這一定是未來的發展方向,不久后的將來哪一個會成為最主流的方式,時間會給我們答案。

審核編輯 黃昊宇

-

芯片

+關注

關注

460文章

52520瀏覽量

441232 -

封裝

+關注

關注

128文章

8685瀏覽量

145544

發布評論請先 登錄

aQFN封裝芯片SMT工藝研究

芯片傳統封裝形式介紹

倒裝芯片的優勢_倒裝芯片的封裝形式

SMT里面區別于傳統的芯片封裝有哪些形式?

SMT里面區別于傳統的芯片封裝有哪些形式?

評論