消費(fèi)者和無線通信市場比以往任何時(shí)候都更具競爭力。公司聚合與分解之間的持續(xù)戰(zhàn)斗如火如荼。聚合的一個(gè)例子是決定通過將芯片設(shè)計(jì)引入內(nèi)部來擁有更多的垂直設(shè)計(jì)鏈。這有助于像 Apple 這樣的公司通過控制更多的整體產(chǎn)品設(shè)計(jì)來實(shí)現(xiàn)差異化,從而不受其他人可用的現(xiàn)成芯片的限制。

雖然蘋果已經(jīng)證明了垂直差異化的潛在回報(bào),但這種方法確實(shí)帶來了巨大的風(fēng)險(xiǎn),無論一家公司是否有設(shè)計(jì)芯片的經(jīng)驗(yàn)。具體來說,軟件團(tuán)隊(duì)如何開發(fā)與交付的硬件一起使用的軟件?

在等式的另一邊,完全分解是由軟件抽象層(如谷歌的 Android 操作系統(tǒng))實(shí)現(xiàn)的。它在某種程度上使設(shè)計(jì)空間民主化,允許所有系統(tǒng)公司參與并使用軟件實(shí)現(xiàn)差異化。Android 允許半導(dǎo)體供應(yīng)商通過提供支持硬件平等參與。同樣,軟件與硬件一起工作的方式?jīng)Q定了產(chǎn)品的成功。

這個(gè)問題的傳統(tǒng)解決方案在今天的市場上是行不通的。公司過去可以根據(jù)規(guī)范開始軟件開發(fā),并等待芯片原型可供測試。如果軟件非常簡單,獨(dú)立于硬件,并且有一個(gè)簡單的規(guī)范,那么它就可以工作,但對于今天需要所有東西都連接起來的消費(fèi)電子產(chǎn)品來說就不行了。

此外,等待很長時(shí)間才能開始測試會(huì)使調(diào)試周期在計(jì)劃中太晚。近年來,許多公司通過轉(zhuǎn)向標(biāo)準(zhǔn)的現(xiàn)成芯片來解決這個(gè)問題,但這種方法限制了差異化的能力。如果你想添加一個(gè)省電的睡眠模式但是沒有辦法關(guān)閉芯片怎么辦?

在綜合場景中,公司不僅在軟件和工業(yè)設(shè)計(jì)方面尋求差異化,而且在電子硬件方面也有所不同。進(jìn)行芯片設(shè)計(jì)項(xiàng)目會(huì)帶來風(fēng)險(xiǎn);再加上嵌入式軟件開發(fā),整體項(xiàng)目風(fēng)險(xiǎn)呈指數(shù)級上升。大多數(shù)公司都非常小心,會(huì)花大量時(shí)間預(yù)先構(gòu)建系統(tǒng)、對其進(jìn)行測試、將其劃分為軟件和硬件,并指定兩者的行為。但是一旦每個(gè)團(tuán)隊(duì)開始設(shè)計(jì),就會(huì)做出某些實(shí)現(xiàn)假設(shè),引入錯(cuò)誤,并且可以添加功能。

在一個(gè)分散的世界中,情況甚至更糟,因?yàn)樨?zé)任現(xiàn)在跨越了公司邊界。來自系統(tǒng)和半導(dǎo)體領(lǐng)域的公司可能會(huì)決定合作優(yōu)化硬件/軟件交互并創(chuàng)建針對系統(tǒng)需求進(jìn)行優(yōu)化的芯片。即使有持續(xù)的同步會(huì)議,設(shè)計(jì)更改也會(huì)在軟件團(tuán)隊(duì)不知情的情況下潛入,并且可能直到軟件第一次在實(shí)際硬件上運(yùn)行時(shí)才會(huì)被看到。這又回到了硬件不夠快可用的問題。工程師如何解決這個(gè)難題?

原型設(shè)計(jì)的黃金模型

以軟件模型形式出現(xiàn)的硬件虛擬原型(或虛擬平臺(tái))在流程的早期為軟件團(tuán)隊(duì)提供了系統(tǒng)硬件模型。這使開發(fā)人員能夠開始對硬件規(guī)范模型進(jìn)行測試。但是,它只是規(guī)范的模型。今天的大多數(shù)硬件設(shè)計(jì)都是從工程師閱讀和解釋規(guī)范開始的,然后用 Verilog 等硬件設(shè)計(jì)語言編寫低級寄存器傳輸語言 (RTL) 模型,以開始驗(yàn)證和實(shí)施過程。由于前面提到的因素,硬件行為可能會(huì)偏離規(guī)范。

解決方案是使用一個(gè)通用的“黃金模型”,軟件團(tuán)隊(duì)可以在該模型上進(jìn)行開發(fā),硬件團(tuán)隊(duì)可以使用該模型開始實(shí)施。現(xiàn)在,隨著開放系統(tǒng) C 倡議 (OSCI) 事務(wù)級建模 (TLM) 2.0 標(biāo)準(zhǔn)的可用性,這成為可能。

簡而言之,SystemC 是一個(gè)類庫,通過對硬件數(shù)據(jù)類型和并發(fā)性進(jìn)行建模,可以使用 C/C++ 進(jìn)行硬件設(shè)計(jì)。因?yàn)橛布F(xiàn)在可以用 C 語言建模,所以軟件團(tuán)隊(duì)可以運(yùn)行相同的模型。TLM 擴(kuò)展很重要,因?yàn)樗鼈兂橄蟪鲇布璧乃?a target="_blank">信號(hào)級協(xié)議細(xì)節(jié),以確保它與系統(tǒng)總線正確通信。過多的這些細(xì)節(jié)會(huì)使模型運(yùn)行軟件太慢。TLM 將這些細(xì)節(jié)抽象為更高級的模型,這些模型可以在高級綜合期間映射到詳細(xì)的硬件。

解決高級綜合限制

高級綜合提供了 C 模型和構(gòu)建的實(shí)際硬件之間的自動(dòng)鏈接。這消除了硬件設(shè)計(jì)人員解釋規(guī)范并手動(dòng)編寫自己的模型以開始構(gòu)建硬件的人為因素。直到最近,由于現(xiàn)在已經(jīng)解決了一些關(guān)鍵限制,這在實(shí)踐中很少使用:

結(jié)果質(zhì)量:前兩代高級綜合從未能夠生產(chǎn)出滿足手動(dòng)編寫 RTL 所能達(dá)到的相同性能、功耗和尺寸的硬件。現(xiàn)代高級合成技術(shù)已經(jīng)解決了這個(gè)問題。

細(xì)化方法:用于軟件開發(fā)的高級虛擬原型使用 SystemC TLM 描述,但仍需要硬件團(tuán)隊(duì)通過添加硬件架構(gòu)細(xì)節(jié)來對其進(jìn)行細(xì)化,以便高級綜合可以產(chǎn)生最佳的硬件微架構(gòu)。這些細(xì)節(jié)對于軟件測試來說太低級了,會(huì)減慢它的速度,但它們對于構(gòu)建高效的硬件很重要。這種方法現(xiàn)在已經(jīng)存在,并已被早期采用者客戶證明。

驗(yàn)證:直到最近,工程師還缺乏一種成熟的方法來驗(yàn)證 SystemC TLM 中硬件架構(gòu)和其余硬件實(shí)現(xiàn)流程的正確性。這主要是因?yàn)椴淮嬖趯?shí)現(xiàn)實(shí)現(xiàn)的自動(dòng)化路徑,因此大多數(shù)驗(yàn)證都是在較低級別完成的。因此驗(yàn)證成為硬件開發(fā)進(jìn)度的瓶頸。既然存在自動(dòng)化路徑,驗(yàn)證方法就已經(jīng)開發(fā)出來了。

硬件設(shè)計(jì)團(tuán)隊(duì)熟悉使用 SystemC TLM 設(shè)計(jì)和驗(yàn)證硬件的這些傳統(tǒng)障礙。然而,大多數(shù)人并不知道這些障礙已得到解決。那些意識(shí)到這一點(diǎn)的人現(xiàn)在享有顯著的競爭優(yōu)勢。他們可以更有效地描述他們的硬件,更快速地驗(yàn)證它,并更容易地在衍生芯片中重用它。

實(shí)踐中的虛擬平臺(tái)

硬件的通用模型現(xiàn)在可以更早地作為虛擬平臺(tái)的一部分使用,因此可以更快地解決硬件/軟件交互問題。這種通用模型可以作為虛擬平臺(tái)中更大系統(tǒng)的一部分在公司內(nèi)部的聚合開發(fā)場景中交付,也可以在分散的世界中跨公司交付。

系統(tǒng)概念首先被描述為 SystemC TLM 虛擬原型。在 Cadence 流程中,虛擬系統(tǒng)平臺(tái)使用此虛擬原型在此硬件模型上運(yùn)行軟件。同時(shí),硬件設(shè)計(jì)團(tuán)隊(duì)將完善 TLM,為 C-to-Silicon Compiler 高級綜合添加硬件架構(gòu)細(xì)節(jié),這是實(shí)現(xiàn)硅片的開始。

如果在測試過程中發(fā)現(xiàn)錯(cuò)誤,虛擬系統(tǒng)平臺(tái)將與 Incisive Verification Platform 集成,以便可以在軟件和硬件上進(jìn)行調(diào)試。這意味著無需繁瑣的固件補(bǔ)丁即可從源頭解決問題。隨著硬件實(shí)施過程的進(jìn)展,更詳細(xì)的 RTL 模型可用于在驗(yàn)證計(jì)算平臺(tái)中創(chuàng)建硬件仿真模型或在快速原型開發(fā)平臺(tái)中創(chuàng)建 FPGA 原型。

整個(gè)過程是一系列連續(xù)的改進(jìn),從快速 TLM 模型開始,在可用時(shí)添加更多硬件細(xì)節(jié),同時(shí)保持足夠快的運(yùn)行時(shí)以進(jìn)行軟件開發(fā)。這最終使軟件和硬件團(tuán)隊(duì)——甚至跨越公司邊界——擁有一個(gè)通用模型,可以實(shí)現(xiàn)更早的通信和持續(xù)的同步。這是與當(dāng)今消費(fèi)市場所需的創(chuàng)新和交付計(jì)劃保持同步所需的協(xié)作類型。只有硬件團(tuán)隊(duì)發(fā)展其設(shè)計(jì)和驗(yàn)證方法以包含 SystemC TLM,才能實(shí)現(xiàn)這一目標(biāo)。

審核編輯:郭婷

-

FPGA

+關(guān)注

關(guān)注

1632文章

21816瀏覽量

607038 -

芯片

+關(guān)注

關(guān)注

458文章

51418瀏覽量

428675 -

總線

+關(guān)注

關(guān)注

10文章

2910瀏覽量

88539

發(fā)布評論請先 登錄

相關(guān)推薦

如何確保云服務(wù)器上的DeepSeek-R1模型安全?

RAID 5 硬件與軟件 RAID 的區(qū)別

【「大模型啟示錄」閱讀體驗(yàn)】如何在客服領(lǐng)域應(yīng)用大模型

raid 硬件與軟件的區(qū)別

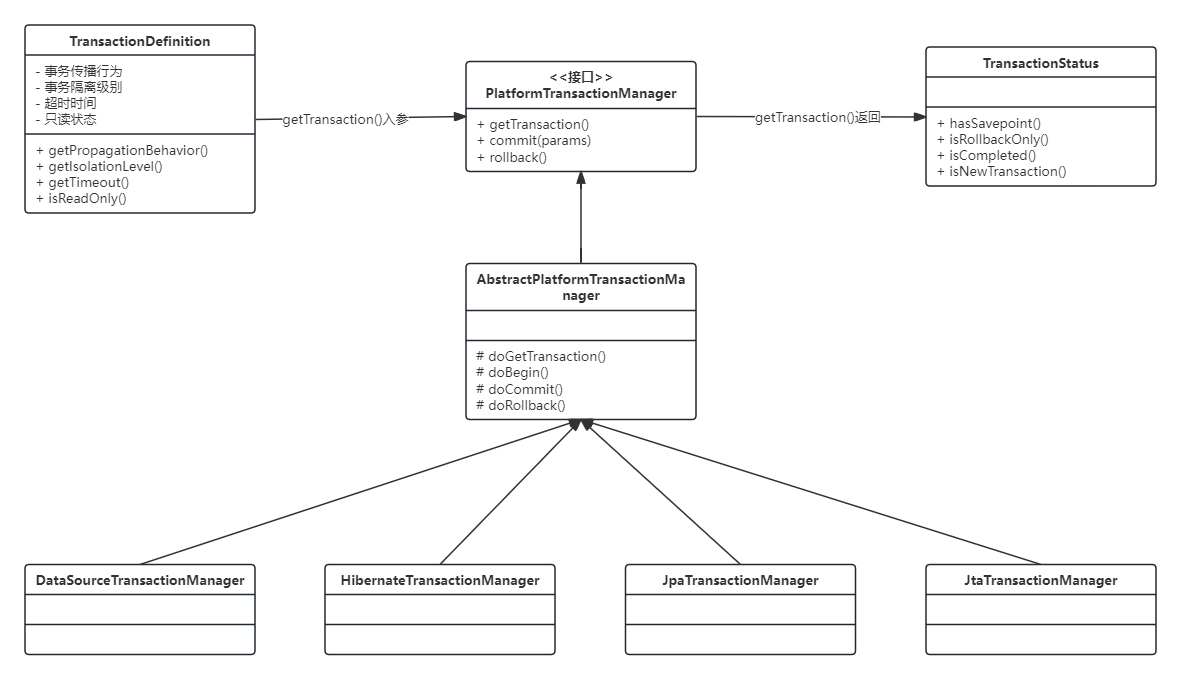

Spring事務(wù)實(shí)現(xiàn)原理

利用CLB實(shí)現(xiàn)基于硬件的同步整流控制

使用事務(wù)級模型確保硬件和軟件同步

使用事務(wù)級模型確保硬件和軟件同步

評論