首先,對“節點”的持續關注掩蓋了一個事實,那就是即使互補金屬氧化物半導體(CMOS)晶體管的幾何形狀無法再壓縮,半導體技術仍然能夠以切實可行的方式繼續推動計算能力的發展。此外,對半導體發展而言,持續的以節點為中心的看法不能像過去那樣以行業刺激的方式為其指明前進方向。最后,讓人難以釋懷的是,大量股票被投入到一個根本毫無意義的數字上。

我們已經開始有更好的替代方式來記錄該行業的里程碑了。可是在這個眾所周知的競爭行業里,專家會團結起來選擇其一嗎?希望他們會,這樣我們就能再次以有效的方式來衡量當今世界上最大、最重要和最具活力的產業之一的進步。

那么,對于這一項可以說是過去百年來最重要的技術,我們是怎樣讓它的進步仿佛是自然而然走到終點的?自1971年英特爾4004微處理器發布以來,金屬氧化物半導體(MOS)晶體管的體積縮小了大約1/1 000,而單塊芯片上的晶體管數量增加了約1 500萬倍。衡量這種集成密度上的極大進步的指標主要是尺寸,即金屬半節距和柵極長度。在很長一段時間里,它們的數字都差不多。金屬半節距是芯片上從一個金屬互連開始到下一個金屬互連開始的距離的一半。在近十年來仍占主導地位的二維晶體管或“平面”晶體管設計中,柵極長度表示晶體管的源極和漏極之間的空間。這個空間里有柵極堆棧,它控制著源極和漏極之間的電子流。從歷史上來看,它是決定晶體管性能最重要的標準,因為柵極較短的設備開關速度更快。

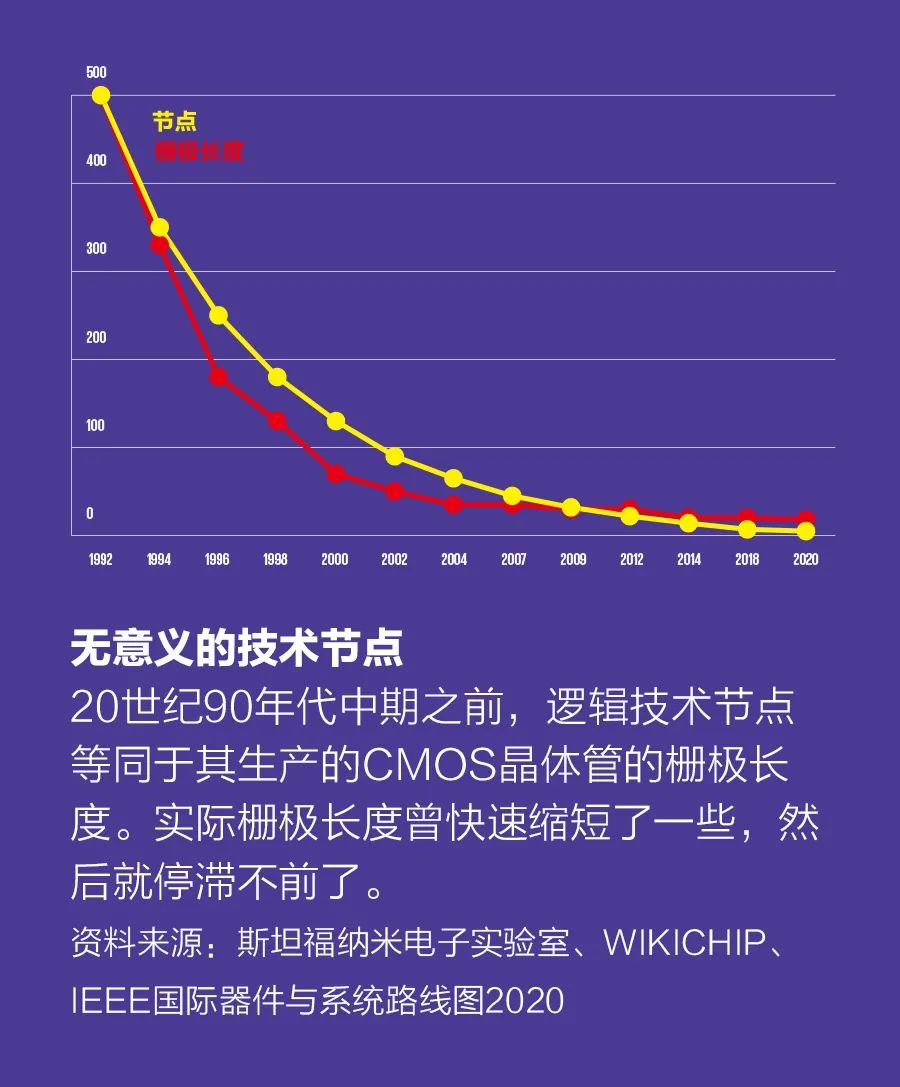

在柵極長度和金屬半節距大致相等的年代,它們代表了芯片制造工藝的關鍵特征,也就是節點數。通常每一代芯片上的這些特征會縮小30%。尺寸大大縮小能夠使晶體管密度增加1倍,因為矩形的x和y邊減小30%意味著其面積減半。

在20世紀70和80年代,使用柵極長度和半節距作為節點數一直很有用,但在90年代中期,這兩個特征開始剝離。為了繼續大幅度提高速度和硬件效率,芯片制造商在縮小柵極長度方面比處理硬件的其他特征更積極。例如,使用130納米節點制造的晶體管,其柵極實際上只有70納米。其結果是摩爾定律中的密度倍增延續下來,但柵極長度不成比例地縮小了。不過,業內在很大程度上還是延續著舊的節點命名慣例。

21世紀初的發展進一步拉大了這種差距,因為處理器遇到了耗電量的限制。工程師們還是在不斷改進硬件。例如,讓晶體管的一部分硅受到應力作用,使載流子在較低的電壓下更快地通過,從而提高CMOS設備的速度和功率效率,且不用大大縮短柵極長度。

當電流泄漏問題迫使人們調整CMOS晶體管結構時,情況更奇怪了。在2011年,英特爾在22納米節點上改用鰭式場效應晶體管(FinFET)時,設備的柵極長度為26納米,半節距為40納米,鰭片寬度為8納米。

該行業的節點數“那時絕對沒有意義,因為與你的任務真正有關的晶粒,其任何尺寸都與節點數無關”,IEEE終身會士、英特爾的老將保羅?加吉尼(Paolo Gargini)說,他正在負責提出新的衡量標準。

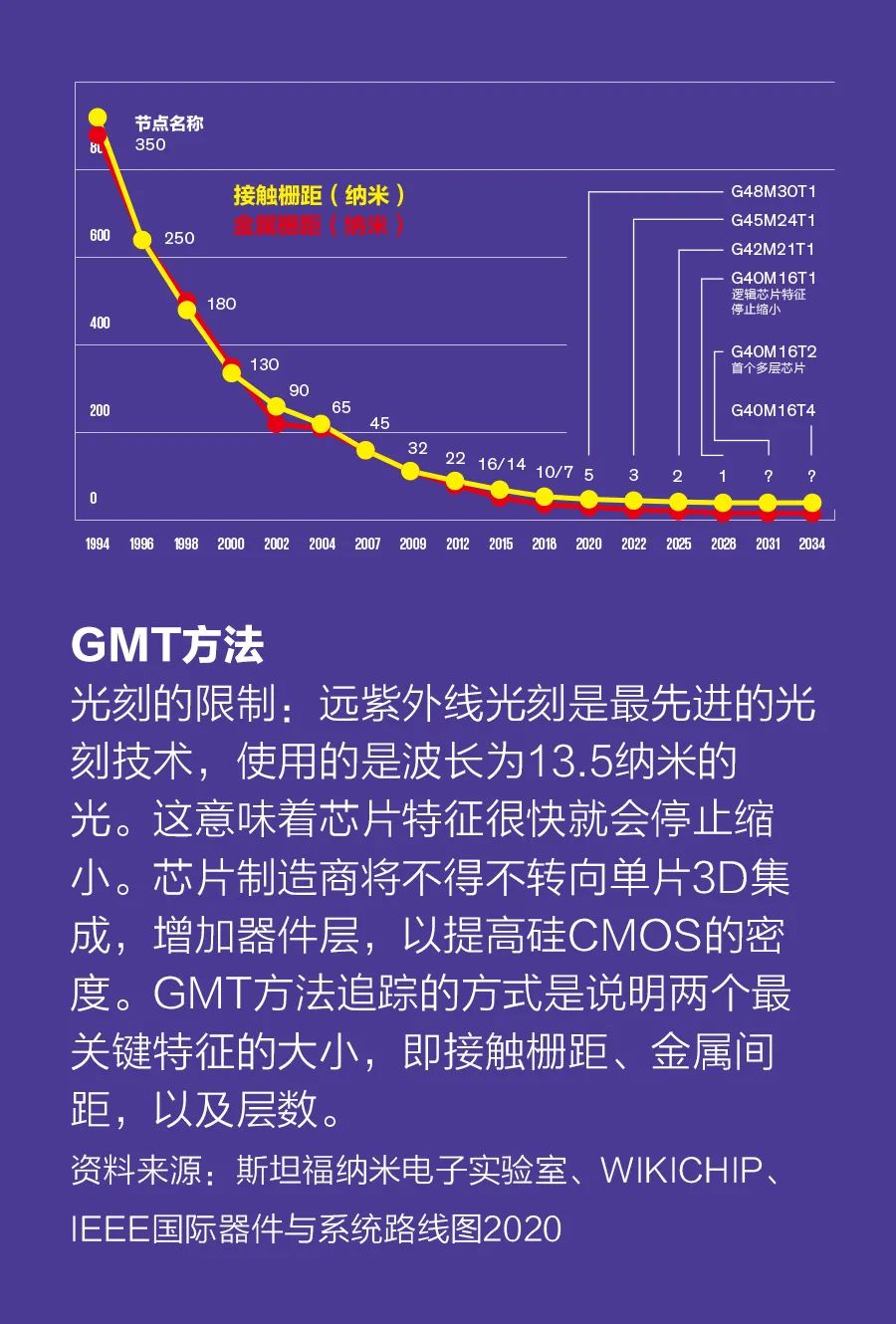

半導體行業需要更好的技術,這是一種廣泛的共識,雖然這種共識并不普遍。有一種解決方案是簡單地根據晶體管重要實際特征的尺寸來重新調整命名。這并非是指依據柵極長度調整,因為它已不是最重要的特征。相反,人們建議使用另外兩種參數,它們代表了制造邏輯晶體管所需區域的實際限制。一種參數叫接觸柵距,是指從一個晶體管的柵極到另一個晶體管柵極的最小距離。另一個重要的參數是金屬間距,是指兩個水平互連之間的最小距離。(沒有理由再將金屬間距分成兩半,因為柵極長度如今也不那么相關了。)安謀國際科技股份有限公司(Arm)的首席研究工程師布萊恩?克萊恩(Brian Cline)解釋說,這兩個值是創造新過程節點中的邏輯的“最小公分母”。這兩個值的乘積很好地估算了晶體管的最小可能面積。每一個其他設計步驟(形成邏輯或SRAM單元、電路模塊)都會增加這一最小可能面積。他說:“良好的邏輯過程加上深思熟慮的物理設計特性,將使該值得到最小程度的降低。”

2020年4月,IEEE國際器件與系統路線圖(IRDS)主席保羅?A. 加吉尼(Paolo A. Gargini)提出使用一種包含3個數字的指標讓該行業“回歸現實”,該指標結合了接觸柵距(G)、金屬間距(M)和芯片上器件的層數(T,該數字對未來的芯片至關重要)。IRDS的前身是國際半導體技術路線圖(ITRS),ITRS是一個持續了幾十年的行業級組織,目前已不復存在,它曾預測了未來節點的各個方面,使相關行業及其供應商有了統一的目標。

“評估晶體管密度時只需要知道這3個參數。”加吉尼說,他也曾是ITRS的負責人。

IRDS的路線圖顯示,即將推出的5納米芯片有著48納米的接觸柵距、36納米的金屬間距,且為單層,因此其指標為G48M36T1。雖然該命名尚未真正落實,但其傳達的信息比“5納米節點”更有用。

與節點命名法一樣,該GMT度量標準中的接觸柵距和金屬間距值會在10年里繼續縮小。不過其縮小速度會越來越慢,按照目前的發展速度,大約會在10年后達到終點。到那時,金屬間距將接近遠紫外線光刻能達到的極限。雖然上一代光刻機的成本效益遠遠超過了193納米波長的限制,但遠紫外線可能達不到這種程度。

“光刻工藝大約會在2029年達到極限。”加吉尼說,在那之后,“進步方式就是堆疊……這是提高密度的唯一方法。”

此時層數(T)開始變得重要。如今先進的硅CMOS是單層晶體管,這些晶體管由十多層金屬互連連接成電路。如果能制造出兩層晶體管,我們就能一舉將設備的密度提高1倍。

對于硅CMOS來說,相關技術目前還處于實驗室階段,但其問世的時間應該不會太遠。十年多來,工業研究人員一直在探索“整體式3D集成電路”芯片,它由一層層搭建的晶體管組成。這并不容易,因為硅處理溫度通常很高,建造一層可能會破壞另一層。盡管如此,一些工業研究機構(尤其是比利時的納米技術研究公司(Imec)、法國的CEA-Leti和美國的英特爾)正在開發一種可以在CMOS邏輯上疊加建造通道金屬氧化半導體(NMOS)和P溝道金屬氧化半導體(PMOS)這兩種晶體管的技術。

即將到來的非硅技術甚至可以更快地實現3D構建。例如,麻省理工學院的馬克斯?舒勒克(Max Shulaker)教授和他的同事已經在開發依靠碳納米晶體管層的3D芯片。由于可以在相對較低的溫度下加工這些器件,所以其多層搭建比硅設備中的多層搭建更容易。

另一些人則致力于在硅上的金屬互連層內構建邏輯或存儲單元,包括微型機械繼電器和薄如原子的半導體(如二硫化鎢)制成的晶體管。

大約1年前,一群著名的學者相聚在加州大學伯克利分校,提出了他們自己的度量標準。這個非正式小組的成員包括半導體研究領域的一些大名鼎鼎的人物。2019年6月會議上的3位加州大學伯克利分校工程師都參與了FinFET項目,分別是胡正明、金智杰(Tsu-Jae King Liu)、杰弗里?博科(Jeffrey Bokor)。博科是該校電氣工程系的主席,胡正明曾擔任世界上最大的半導體制造公司臺積電(TSMC)的技術總監,2020年獲得了IEEE榮譽勛章。金智杰是工程學院院長,也是英特爾董事會的董事。來自加州大學伯克利分校的與會者沙耶夫?薩拉赫丁(Sayeef Salahuddin)則是開發鐵電裝置的先驅。

斯坦福大學的小組成員包括黃漢森,他是教授,也是臺積電的企業研究副總裁;蘇哈西什?米特拉(Subhasish Mitra),發明了一項重要的自測技術,并與黃漢森合作開發了第一臺基于碳納米管的計算機;詹姆斯?D. 普盧默(James D. Plummer),英特爾的前董事會成員,也是斯坦福大學任職時間最長的工程系院長。此外,臺積電的研究員凱雷姆?阿卡爾瓦達爾(Kerem Akarvardar)和麻省理工學院的迪米特里?安東尼迪斯(Dimitri Antonidis)隨后也加入了該小組。

金智杰說,他們都感到自己所在的領域對優秀學生,尤其是美國學生的吸引力正在下降。這種現狀背后的邏輯似乎很簡單:如果一個領域從現在起的10年內都不可能取得進步,那么為什么還要花4~6年的時間來進行相關學習?她表示,當“我們需要越來越多的創新解決方案來繼續推動計算機技術的發展”時,這種對優秀學生缺乏吸引力的現象就出現了。

專家們希望能找到一種可以打破節點“末日時鐘氛圍”的度量標準。他們認為,最重要的是這個度量應該沒有自然終點。換句話說,數量應該隨著技術進步上升,而不是下降。它還必須簡單、準確,而且要與提高半導體技術的主要目的(即擁有更強大的計算系統)相關。

要實現該目標,他們希望不僅僅是像IRDS的GMT度量標準那樣只描述制造處理器所使用的技術。他們想要的指標不僅要能考慮處理器,還能考慮影響整個計算機系統性能的其他關鍵因素。這可能看起來過于雄心勃勃,但它卻與計算機正在發展的方向吻合。

打開英特爾Stratix 10現場可編程門陣列(FPGA)的封裝,你會發現它不僅僅是一個FPGA處理器。在封裝內,處理器晶粒被一系列“小芯片”包圍,值得注意的是,其中有兩個高帶寬動態隨即存取存儲器(DRAM)芯片。其中,一小片硅蝕刻了密集的互連線陣列,將處理器連接到存儲器。

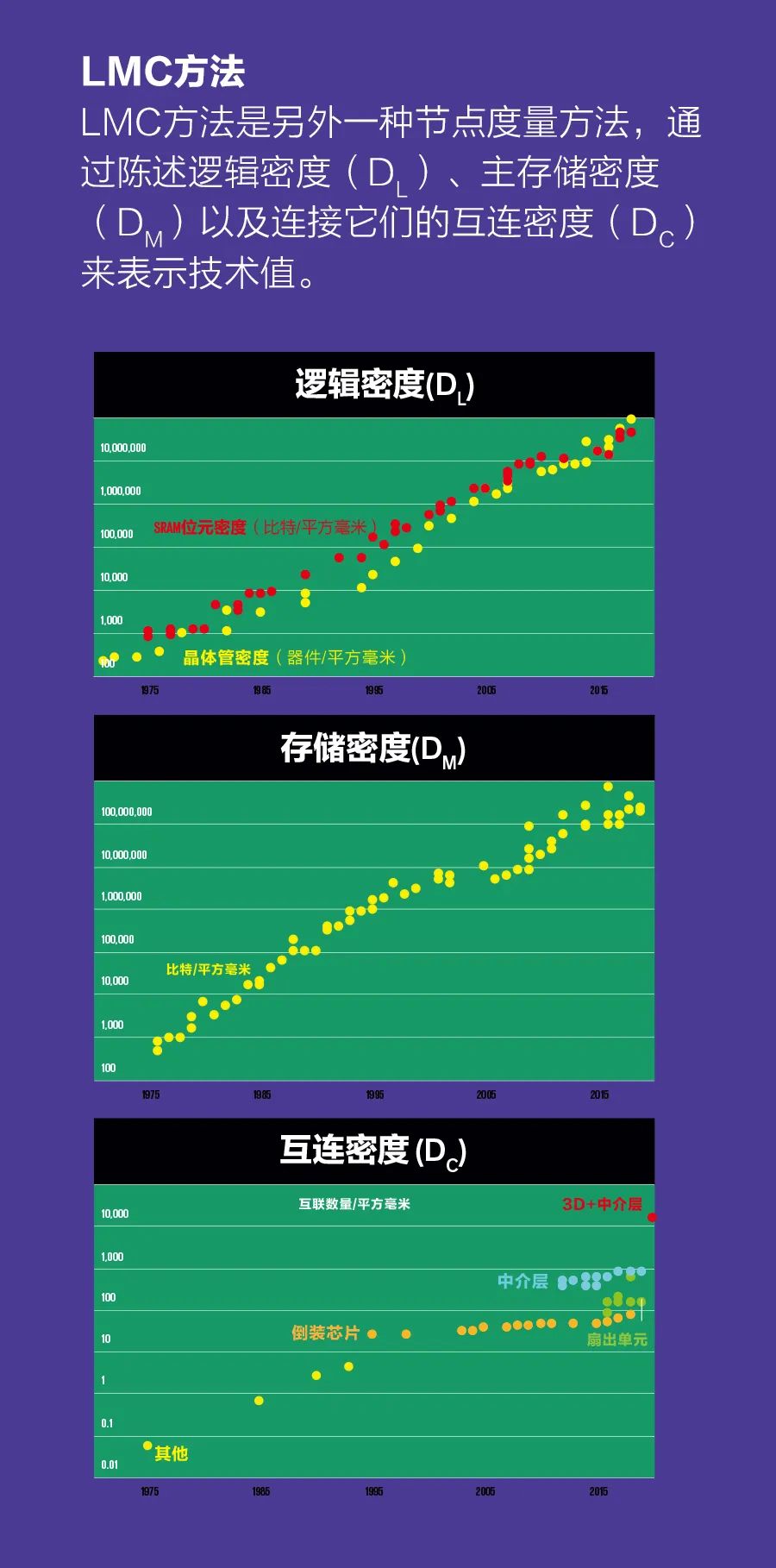

計算機最基本的就是邏輯、存儲以及它們之間的連接。為了形成新的度量方法,黃漢森和他的同事選擇將每個組件的密度作為參數,稱為DL、DM和DC,把腳注連在一起,稱其為LMC度量。

LMC度量的提出者表示,DL、DM和DC的改進共同對計算系統的總體速度和能源效率起主要作用,特別是在當今以數據為中心的計算時代。他們繪制了歷史數據,揭示了邏輯、存儲和連通性的增長之間的關聯,這種關聯表明DL、DM和DC的平衡增長已經持續了幾十年。他們認為,這種平衡隱含在計算機架構中,而且令人驚訝的是,它適用于復雜程度不同的各類計算系統(從移動和桌面處理器到世界上運行速度最快的超級計算機)。黃漢森說,這種均衡的增長表明,未來也需要類似的改善。

?在LMC度量中,DL是邏輯晶體管的密度,即每平方毫米的元件數量。DM是一個系統的主要存儲單元的密度,即每平方毫米的存儲單元,DC是邏輯與主存儲器之間的連接密度,即每平方毫米的互連數量。如果有多層器件或3D芯片堆棧,那么該平方毫米上的整個體積就顯得很重要。

?在LMC度量中,DL是邏輯晶體管的密度,即每平方毫米的元件數量。DM是一個系統的主要存儲單元的密度,即每平方毫米的存儲單元,DC是邏輯與主存儲器之間的連接密度,即每平方毫米的互連數量。如果有多層器件或3D芯片堆棧,那么該平方毫米上的整個體積就顯得很重要。

DL也許這三者中我們最熟悉的,因為自從第一個集成電路問世以來,人們就一直在計算芯片上的晶體管數量。這聽起來很簡單,其實不然。處理器上不同類型的電路密度不同,很大程度上是因為連接設備的互連。邏輯芯片最密集的部分通常是構成處理器緩存的靜態隨機存取存儲器(SRAM),它會存儲數據以便快速重復訪問。這些緩存是很大的六晶體管單元列陣,這些單元緊密地封裝在一起的一部分原因是它們很規則。按照這種衡量方法,目前最高的DL是一個135兆比特的SRAM陣列,它使用的是臺積電的5納米工藝,其封裝相當于每平方毫米2.86億個晶體管。按照擬議命名法,它稱為“286M”。

不過邏輯塊比嵌入其中的SRAM更復雜、更不統一,也更不密集。因此僅憑SRAM判斷一項技術可能不公平。2017年,時任英特爾高級研究員的馬克?波爾(Mark Bohr)提出了一個使用一些普通邏輯單元加權密度的公式。該公式考慮了一種簡單且普遍存在的雙輸入四晶體管NAND柵極和一種叫做掃描觸發器的常見但較復雜電路的單位面積晶體管計數。該公式根據典型設計中這種小柵極和大單元的比例來計算其重量,得出一個每平方毫米晶體管的結果。波爾當時說,SRAM的密度不同,所以應該分開測量。

根據超微半導體公司(AMD)高級研究員凱文?吉萊斯皮(Kevin Gillespie)的說法,AMD內部也使用了類似的方式。他說,如果一種衡量方式不考慮設備是如何連接的,那它就不準確。

幾位專家則單獨提出了另一種可能性,即測量一些互相認可的、大塊半導體設計的平均密度,如安謀的一種廣泛可用的處理器設計。

事實上,安謀的克萊因稱,安謀放棄了嘗試使用單一度量,轉而從完整的處理器設計中提取功能電路塊的密度。他說:“我認為不存在能夠適用于所有硬件應用的、一刀切的邏輯密度度量方法。”因為芯片和系統的類型多種多樣。他指出,不同類型的處理器(CPU、GPU、神經網絡處理器、數字信號處理器)具有不同的邏輯和靜態存儲器比率。

最后,LMC的發起者選擇不指定某種特定的度量方法測量DL,將其留給業內討論。

測量DM比較簡單。目前,主存儲通常指的是DRAM,因為它價格便宜、耐用、讀寫速度相對較快。一個DRAM單元包括控制著電容器訪問的單個晶體管,而電容器將比特存儲為電荷。電荷會隨著時間的推移而泄漏,因此必須定期刷新單元。如今,電容器建立在硅上方的互連層,因此密度不僅受晶體管尺寸的影響,還受互連的幾何形狀的影響。LMC小組在已出版文獻中能找到的最高DM值來自三星。2018年,該公司詳細介紹了DRAM技術,其密度為每平方毫米2億個單元(200M)。

DRAM可能也無法一直維持在主存儲器中的地位。可替代的存儲器技術(如磁阻RAM、鐵電RAM、電阻RAM和相變RAM)現在已經投入商業生產,有些是嵌入處理器的存儲器,有些是獨立芯片。

當今的計算系統中,在主存儲器和邏輯之間提供充足的連接是主要瓶頸。從歷史上來看,人們一直采用封裝級技術來制造處理器和存儲之間的互連(DC所衡量的內容),而不是采用芯片制造技術。與邏輯密度和存儲密度相比,幾十年來DC的改善并不穩定。相反,隨著新封裝技術的引入和精進,DC的提高呈現出非連續的特點。近十年來的變化尤其大,片上系統(SoC)已經開始給緊密結合在硅中介層(稱為2.5D系統)上或堆疊在3D結構上的小芯片讓路。目前已知的最高DC來自采用臺積電集成芯片系統3D芯片堆疊技術制造的系統,該系統每平方毫米有1.2萬個互連(12K)。

不過,DC不一定要將邏輯連接到一個單獨的存儲芯片上。在某些系統中,主存儲器是完全嵌入的。例如,Cerebras系統的機器學習大型芯片完全依賴嵌入在一塊巨大硅片上的邏輯磁芯附近的SRAM。

LMC的提出者建議,將結合DL、DM和DC這3個最佳參數的系統命名為260M、200M、12K。

英特爾的首席技術官邁克爾?梅伯里(Michael Mayberry)認為,用一個數字來描述半導體節點先進程度的時代已經一去不復返了。不過,原則上他還是贊成我們要有一個全面的系統級度量方式。他說:“選擇即使不完美但已經達成一致的方式,也比當前的節點命名法更有用。”他希望LMC能夠得到進一步的擴展,明確需要測量什么以及如何測量。例如,關于DM值,梅伯里說它可能需要與具體存儲器相關,該存儲器應與其服務的處理器位于相同的芯片封裝。他補充說,“主存儲器”的內容可能也需要微調。將來,處理器和數據存儲設備之間可能會存在多層存儲器。例如,英特爾和美光制造了3D XPoint存儲器,這是一種介于DRAM和存儲器之間的非易失系統。

進一步的批評之聲則提出,像LMC這種基于密度的度量標準和GMT這種基于光刻技術的度量標準都偏離了晶圓用戶和內存芯片制造商的需求。AMD的吉萊斯皮說:“除了面積(密度),還有性能、功率和成本。”每一個芯片設計都圍繞著這4個因素進行權衡,“沒有哪個單獨的數字能夠說明節點的好壞。”梅伯里補充道。

全球第三大DRAM制造商美光科技的高級研究員兼副總裁古特伊?辛格?桑杜(Gurtej Singh Sandhu)說:“內存和存儲最重要的衡量標準還是每比特的成本。其他幾個因素(包括基于特定市場應用的各種性能指標)也在密切考慮之內。”

還有人甚至認為目前無需新的度量標準。格羅方德公司負責工程和質量的高級副總裁格雷格?巴特利特(Gregg Bartlett)表示,這些措施“只對以規模化為主導的應用有用”,該公司于2018年放棄了對7納米工藝的追求。“只有少數幾家公司從事這方面的生產,客戶和應用的數量也有限,因此它與絕大多數半導體行業的關聯度較低。”只有英特爾、三星和臺積電在追求最后幾個CMOS邏輯節點,這幾家公司都不是小角色,它們在全球半導體生產中占有重要地位。

巴特利特的公司并不屬于這一行列,他認為,CMOS邏輯與專業技術(例如嵌入式非易失存儲器和毫米波無線電等)結合對該行業的未來比規模化更重要。

毫無疑問,持續的規模化對許多半導體消費者都很重要。LMC度量和GMT度量的提出者都有一種緊迫感,不過原因不同。對于黃漢森和LMC的支持者來說,在一個晶體管規模化不再那么重要的時代,該行業需要明確自己的長期未來,這樣他們才能招募到技術人才來實現這一領域的未來。

對于加吉尼和GMT的支持者來說,此舉是為了讓該行業步入正軌。在他看來,度量不同步,行業的效率就較低。“這會提高失敗的可能性。”他說。“再過10年”,硅CMOS的縮小就會完全止步,我們取得必要突破以繼續提高計算能力的時間“并不充裕”。

審核編輯 :李倩

-

CMOS

+關注

關注

58文章

6022瀏覽量

238845 -

摩爾定律

+關注

關注

4文章

640瀏覽量

79869 -

晶體管

+關注

關注

77文章

10019瀏覽量

141643

原文標題:我們有比摩爾定律更好的方法來衡量技術進步

文章出處:【微信號:HXSLH1010101010,微信公眾號:FPGA技術江湖】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

跨越摩爾定律,新思科技掩膜方案憑何改寫3nm以下芯片游戲規則

電力電子中的“摩爾定律”(1)

能效比和算力提升的衡量方法

使用ad9467-250來采集低頻信號,請問有什么方法來提高sfdr嗎?

瑞沃微先進封裝:突破摩爾定律枷鎖,助力半導體新飛躍

AI正在對硬件互連提出“過分”要求 | Samtec于Keysight開放日深度分享

混合鍵合中的銅連接:或成摩爾定律救星

石墨烯互連技術:延續摩爾定律的新希望

摩爾定律是什么 影響了我們哪些方面

后摩爾定律時代,提升集成芯片系統化能力的有效途徑有哪些?

CMOS 2.0:摩爾定律的新篇章

高算力AI芯片主張“超越摩爾”,Chiplet與先進封裝技術迎百家爭鳴時代

比摩爾定律更好的方法來衡量技術進步

比摩爾定律更好的方法來衡量技術進步

評論