下一代芯片會什么樣子,什么時候能實(shí)現(xiàn)?

芯片制造商正在為架構(gòu)、材料和基本結(jié)構(gòu)(如晶體管和互連器件)的根本性變革做好準(zhǔn)備。最終結(jié)果將是有更多的流程步驟、每個步驟的復(fù)雜性增加,以及全面成本上升。

在前沿,F(xiàn)inFET會在3nm節(jié)點(diǎn)之后的某個地方前進(jìn)困難。仍在這些節(jié)點(diǎn)工作的三家代工廠 ——臺積電,三星和英特爾,以及行業(yè)研究機(jī)構(gòu) imec正在尋求某種形式的柵極全能晶體管作為下一個晶體管結(jié)構(gòu) ,以便對柵極泄漏進(jìn)行更嚴(yán)格的控制。

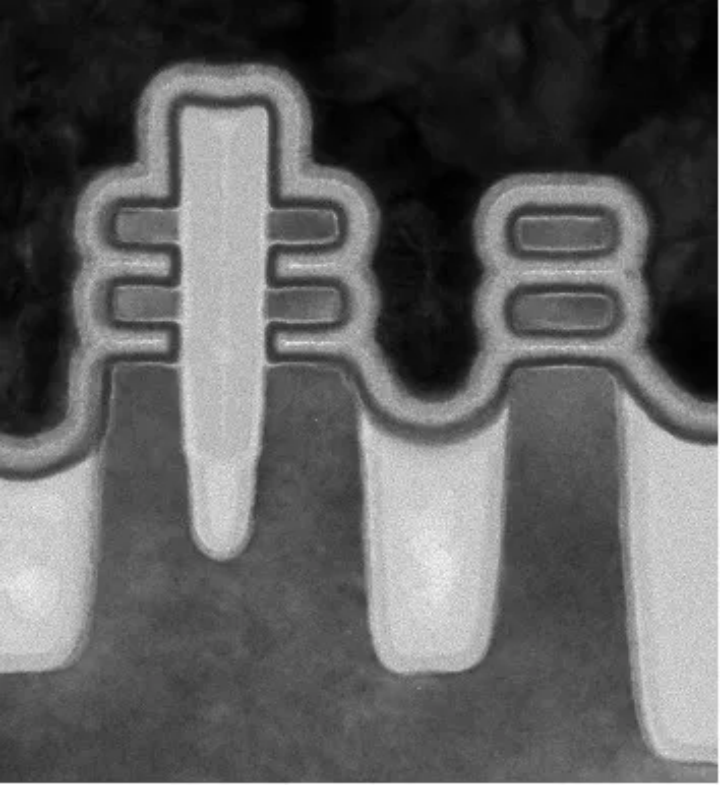

在此之后,這種方法可能至少適用于更多的節(jié)點(diǎn),并可能隨著由imec開發(fā)的中間步驟forksheet FET的推出而進(jìn)一步發(fā)揮作用。(見圖1)然而每家公司都在使用不同的命名,時間表和技術(shù)組合,因此很難確定哪個公司在什么時候處于技術(shù)領(lǐng)先地位。

圖1:N型和P型 forksheet FET對(左)

和nanosheet FET(右)。來源:imec

“回顧過去,我們從雙極器件開始,然后我們轉(zhuǎn)向平面CMOS和3D FinFET,”臺積電業(yè)務(wù)發(fā)展高級副總裁Kevin Zhang說。“現(xiàn)在我們正在轉(zhuǎn)向nanosheet柵極全能晶體管。但晶體管結(jié)構(gòu)將會演變。不是每一代或每一個節(jié)點(diǎn)都需要引入新的架構(gòu),因?yàn)樾碌木w管或架構(gòu)需要很長很長的時間。我們已經(jīng)投資nanosheet技術(shù)超過10年,以便有足夠的信心在2nm節(jié)點(diǎn)上引入它。”

代工廠將盡可能長時間地?cái)U(kuò)展現(xiàn)有技術(shù) ,因?yàn)槊看胃鼡Q升級都是昂貴的。除了代工廠開發(fā)的新制造工藝外,還需要微調(diào)涉及制造設(shè)備的數(shù)百個工藝步驟。這里的關(guān)鍵指標(biāo)是制造每個晶圓所花費(fèi)的時間,這會影響成本,以及獲得足夠良率的時間。每個步驟都需要更改所有內(nèi)容,從EDA工具(需要在每個節(jié)點(diǎn)和每個鑄造廠的半節(jié)點(diǎn)進(jìn)行認(rèn)證)到各種設(shè)備何時插入制造環(huán)流。復(fù)雜芯片可以有多個插入點(diǎn)。這使得實(shí)際的時間表難以確定,代工廠可能不會推到下一個技術(shù)節(jié)點(diǎn),直到他們使用現(xiàn)有技術(shù)進(jìn)行改進(jìn)。

臺積電是目前流程的領(lǐng)導(dǎo)者,也是唯一處于領(lǐng)先地位的純代工廠,計(jì)劃遷移到2nm的GAA FET。臺積電研發(fā)高級副總裁Yuh-jier Mii在最近的一次演講中表示,3nm的finFET在使用相同的功率時將速度提高18%,或在相同的性能下降低34%的功率。使用nanosheet,速度將提高約10%至15%,功耗降低25%至30%,密度增加1.1倍。他還指出,現(xiàn)有的設(shè)計(jì)規(guī)則將在N2兼容,這將降低IP的重用率。

英特爾將遵循類似的路徑,使用其版本的GAA FET,稱為帶狀FET。英特爾同樣表示,它的finFET技術(shù)還有足夠的改進(jìn),可以將finFET擴(kuò)展到另一個節(jié)點(diǎn)。

“我們在當(dāng)前的生產(chǎn)節(jié)點(diǎn)上提供先進(jìn)的 finFET ,”英特爾副總裁兼產(chǎn)品和設(shè)計(jì)生態(tài)系統(tǒng)支持總經(jīng)理Rahul Goyal說。“我們還在研究下一代節(jié)點(diǎn),它將在明年左右推出。然后,我們的sweet spot——這是最先進(jìn)的節(jié)點(diǎn),我們相信我們可以在這里實(shí)現(xiàn)差異化,目前正在與幾個客戶一起開發(fā)。這讓我們更好的規(guī)定好了2024年至2025年的發(fā)展歷程,并更好地了解了客戶的需求以及如何實(shí)現(xiàn)這一目標(biāo)。挑戰(zhàn)在于如何確保我們在早期階段與客戶合作,以盡可能加快我們的學(xué)習(xí)速度,然后使我們的生態(tài)系統(tǒng)和合作伙伴能夠?yàn)槲覀兊目蛻舴?wù)。”

與此同時,三星將在3nm引入GAA技術(shù),稱為多橋通道FET。該公司聲稱,與5nm FinFET相比,該技術(shù)可以將功耗降低45%,將性能提高23%,并將面積減少16%。下一代產(chǎn)品將降低高達(dá)50%的功耗,并將性能提高30%,占地面積減少35%。三星吹捧的關(guān)鍵改進(jìn)之一是可調(diào)節(jié)的通道寬度,它可以降低驅(qū)動信號所需的功率。

下一步是什么?

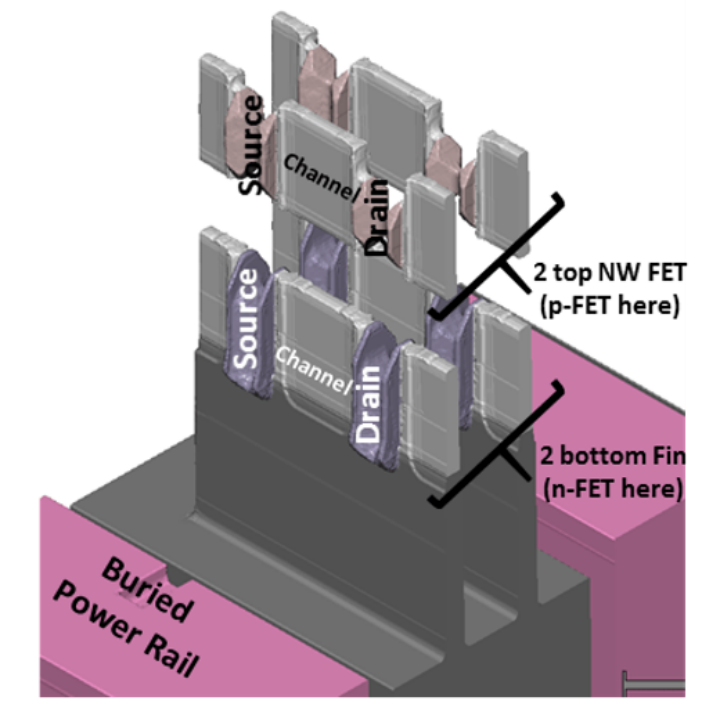

在GAA FET之后,下一個技術(shù)版本可能包括堆疊的GAA FET,也稱為complementary FET(CFET),可擴(kuò)展高達(dá)50%。這種變化至少將nanosheet擴(kuò)展了幾個節(jié)點(diǎn)。可以堆疊多少層可能決定了這項(xiàng)技術(shù)的可擴(kuò)展性。

“我們正在研究橫向nanosheet以及未來幾代技術(shù)中橫向nanosheet某種程度的堆疊,” Lam Research計(jì)算產(chǎn)品副總裁David Fried說。“每個人都喜歡調(diào)查先進(jìn)設(shè)備的完整列表,并查看垂直和橫向設(shè)備和堆棧,但是進(jìn)行任何這些更改所需的投資都非常巨大,以至于制造商必須確信,在他們進(jìn)行過渡之前,他們將從重大過渡中獲得至少幾個節(jié)點(diǎn)。你盡量不要一次一個節(jié)點(diǎn)地做出這些決定。”

預(yù)計(jì)CFET將開始出現(xiàn)在1.4nm左右。CFET已經(jīng)在繪圖板上存在了十多年,被認(rèn)為是nanosheet和forksheet FET的進(jìn)化步驟 。對于CFET,nFET和pFET導(dǎo)線采用單線或雙線配置,在提供面積和密度優(yōu)勢的同時,仍可限制柵極處的電流泄漏。這種泄漏就是即使設(shè)備關(guān)閉,電池也會耗盡或電力繼續(xù)流動的原因。

圖 2:CFET 架構(gòu)。來源:科文托,

Lam Research旗下研究公司

重新思考一些基礎(chǔ)知識

與過去不同,當(dāng)一個過程可以在數(shù)十億個相同設(shè)計(jì)的單元上完成時,最終用戶需要針對特定應(yīng)用的更定制的解決方案。在某些情況下,這些是為內(nèi)部消費(fèi)而設(shè)計(jì)的,例如超大規(guī)模數(shù)據(jù)中心。這限制了特定設(shè)計(jì)的行業(yè)體量,并進(jìn)一步減少了量。

更糟糕的是,其中一些設(shè)備正被用于安全和任務(wù)關(guān)鍵型應(yīng)用。因此,除了數(shù)量有限之外,還需要在更長的使用壽命內(nèi)提高可靠性。

為此,正在制定一些有趣的戰(zhàn)略來處理這些問題和相關(guān)問題。例如,與其期望設(shè)計(jì)中的每個晶體管或互連都能以100%的良率完美地工作, 不如期望能夠在芯片生命周期的任何時候識別出哪些是壞的。這里的重點(diǎn)是彈性。過去,這是通過冗余實(shí)現(xiàn)的,一般的態(tài)度是晶體管是免費(fèi)的。但是,在異構(gòu)設(shè)計(jì)中,這種方法太昂貴了,其中一些計(jì)算元素和內(nèi)存是由不同的供應(yīng)商創(chuàng)建的。

“有兩個問題,”PDF Solutions首席技術(shù)官 Andrzej Strojwas說。“首先,你如何很早就確定電路不起作用?其次,如何構(gòu)建可重配置的互連?可以使用有源電路來重新配置該互連。這樣做的標(biāo)準(zhǔn)方法是在制造過程結(jié)束后進(jìn)行測試,然后燒毀保險(xiǎn)絲。但是,如果通過低級金屬水平的電子束掃描將信息內(nèi)聯(lián)在內(nèi),則可以更有效地做到這一點(diǎn)。粒度是不同的。”

當(dāng)索尼在2000年推出基于IBM的Cell處理器的Playstation 2時,它被設(shè)計(jì)成六個內(nèi)核,盡管只需要五個。這種方法在當(dāng)時被認(rèn)為是革命性的。但是,可重構(gòu)性增加了對從設(shè)計(jì)到制造的應(yīng)用的能力,包括實(shí)時分析,根據(jù)需要重新路由信號的能力,以及更精確地劃分設(shè)計(jì)的能力。

光刻也即將經(jīng)歷一個重大而昂貴的轉(zhuǎn)變。EUV在經(jīng)過大約十年的延遲后,部署用于5nm的大批量生產(chǎn),已經(jīng)落后了。在3nm和2nm處,除非ASML(尖端光刻設(shè)備的唯一來源)能夠以合理的價(jià)格推出高數(shù)值孔徑EUV(HIGH NA EUV),否則將再次需要多圖案化。HIGH NA EUV的光圈為0.55,而EUV為0.33,它使用變形透鏡,能夠在晶片邊緣正確打印特征。但并非所有金屬層都需要HIGH NA EUV,這意味著它可能會作為一種點(diǎn)工具而不是一刀切地集成到制造流程中。

另一個正在獲得挑戰(zhàn)的策略是設(shè)計(jì)技術(shù)協(xié)同優(yōu)化,它將前端設(shè)計(jì)與制造聯(lián)系起來,比過去更緊密地聯(lián)系在一起。DTCO已經(jīng)存在多年,但它只在最先進(jìn)的節(jié)點(diǎn)上使用。

“在平面CMOS時代,設(shè)計(jì)師和技術(shù)可以預(yù)測節(jié)點(diǎn)將如何擴(kuò)展,”Synopsys硅工程集團(tuán)的產(chǎn)品營銷總監(jiān)Ricardo Borges說 。“隨著finFET的引入,這種預(yù)測變得不那么可信,F(xiàn)inFET在混合中引入了一些新事物,使得預(yù)測節(jié)點(diǎn)的特性變得更加困難。今天,有更多種類和更多的架構(gòu)需要探索。例如,在短期內(nèi),我們看到gate全能技術(shù)的早期發(fā)布。除此之外,還有幾種類型的器件,更多的晶體管架構(gòu),更多的材料和系統(tǒng)需要評估。在某些時候,可以用其他材料代替硅。我們已經(jīng)看到了新的金屬,如釕和鉬用于未來的互連,以及用于未來互連的鉍和銻,因?yàn)樗鼈兊?a target="_blank">電阻率較低。然后有一些結(jié)構(gòu),imec稱之為縮放助推器,這可能是一種新的過程技術(shù),以減少圖案化方法的可變性。”

然而,另一種方法是根本不擴(kuò)展到最先進(jìn)的節(jié)點(diǎn)。聯(lián)華電子(UMC)和GlobalFoundries等代工廠正在進(jìn)行大量投資,這些工廠正在使用替代方法來提高PPA。GlobalFoundries技術(shù)、工程和質(zhì)量高級副總裁Gregg Bartlett表示,目前使用的芯片中有80%是在成熟節(jié)點(diǎn)上制造的,他預(yù)計(jì)隨著先進(jìn)封裝、混合鍵合、小芯片和更多領(lǐng)域特定設(shè)計(jì)的增長,這一數(shù)字還會增加。

不過,這并沒有使成熟節(jié)點(diǎn)的設(shè)計(jì)變得不那么復(fù)雜。“我們從材料開始,然后設(shè)計(jì)芯片,而不是從 終端市場開始,弄清楚他們想用設(shè)計(jì)做什么,以及什么材料映射到其中,”Bartlett說。“SOITEC有27種不同類型的SOI(絕緣體上的硅)材料,具有不同的盒子厚度,不同的硅厚度和不同的晶體取向。了解為什么一種基板比另一種基材更好是一個非常重要的考慮因素。這并不是因?yàn)椴牧咸匦浴_@是因?yàn)楫?dāng)它完全集成到系統(tǒng)級別的性能中時,效果就是不同的。”

不同的選擇

令人驚訝的是,在所有工藝節(jié)點(diǎn)上都發(fā)生了多少研發(fā),而不僅僅是在前沿,而且隨著美國芯片與科學(xué)法案和歐洲芯片法案的通過,這項(xiàng)研究可能會爆炸式增長,這些法案將總共投入超過1000億美元用于各種相關(guān)領(lǐng)域的研究。

這包括用于多芯片和多模塊/封裝通信的硅光子學(xué),已在數(shù)據(jù)中心內(nèi)部廣泛用于將服務(wù)器連接到存儲器。它將越來越多地用于越來越短的距離。光速非常快,需要最少的能量來實(shí)際傳輸信號,并且它產(chǎn)生的熱量非常少。但它也需要監(jiān)測熱波動,這可能會將信號推到濾波器范圍之外,并檢查波導(dǎo)中的任何粗糙度,這會影響信號。與電子不同,光子不喜歡角落,這是將電音頻構(gòu)建成芯片的挑戰(zhàn)之一。

“對我們來說,我們希望能夠模擬以某種形狀或方式裝瓶在一起的兩個設(shè)備,并能夠模擬和模擬這兩者的組合,”Bartlett說。“EDA的工作人員在后臺做得很好。我們剛剛與一家EDA供應(yīng)商在我們的45CLO平臺上發(fā)布了一個公告(C,L和O是不同的波長波段,每個波長段都有不同的損耗)。這些都是處于行業(yè)前沿的領(lǐng)域,我們正在努力為客戶提供正確的設(shè)計(jì)工具。”

行業(yè)都在蓬勃發(fā)展。“強(qiáng)勁的晶圓需求使我們的晶圓廠保持滿負(fù)荷運(yùn)轉(zhuǎn),并且價(jià)格高于我們整體收入的平均混合定價(jià),”聯(lián)華電子總裁Jason Wang在最近的業(yè)績發(fā)布會上表示。“SoC技術(shù),如非易失性存儲器、電源管理、RF-SOI和OLED顯示驅(qū)動器,是5G、AIoT和汽車領(lǐng)域的必要應(yīng)用。我們專注于特種技術(shù)的戰(zhàn)略取得了成功,它現(xiàn)在貢獻(xiàn)了我們硅片收入的一半以上。”

Jason Wang指出,汽車的持續(xù)電氣化也是未來增長的催化劑。

其他選擇

也許最大的轉(zhuǎn)變來自封裝選項(xiàng)和小芯片。有許多方法可以將不同的部分放在一起,包括在最先進(jìn)的節(jié)點(diǎn)上開發(fā)的數(shù)字邏輯與其他邏輯、模擬和在成熟節(jié)點(diǎn)上開發(fā)出的各種類型的存儲器的混合。事實(shí)上,隨著設(shè)計(jì)變得越來越異構(gòu),并針對特定應(yīng)用和用例進(jìn)行定制,人們越來越需要為它們增加更大的靈活性。

“我們采訪的一位客戶有一個非常復(fù)雜的中斷控制器,”Flex Logix銷售、營銷和解決方案架構(gòu)副總裁Andy Jaros說。“他們需要預(yù)測客戶想要啟動芯片的所有不同排列,包括連接哪些外圍設(shè)備或使其可用于外部世界,他們正試圖在軟件控制下做到這一點(diǎn)。他們發(fā)現(xiàn),無論他們?nèi)绾闻渲盟蛘咧袛嗫刂破饔卸鄰?fù)雜,中斷控制器都不受支持。這就是嵌入式FPGA發(fā)揮作用的地方。你可以擁有一個更簡單的中斷控制器,并且該中斷控制器是針對每個客戶精心設(shè)計(jì)的。因此,現(xiàn)在不必預(yù)測每個潛在的引導(dǎo)情況或引導(dǎo)序列或組合變化。基本上,當(dāng)客戶需要它時,就會生成一些新的RTL,并將其放入該客戶的排序要求中。”

混合和匹配各種組件和過程也會產(chǎn)生一些意想不到的結(jié)果。考慮混合鍵合,它提供了一種比將它們焊接在一起更直接的方式來連接不同的組件。

“由于焊料的低溫工藝,它限制了許多下游應(yīng)用,”Brewer Science晶圓級加工業(yè)務(wù)部執(zhí)行董事Kim Yes說。“我們還看到客戶在進(jìn)行焊球集成的地方,有很多的變形或斷裂,他們現(xiàn)在正在考慮混合粘合。這將比真正的異構(gòu)集成更快。”

銅到銅混合鍵合是最遠(yuǎn)的,但目前正在進(jìn)行使用電介質(zhì)進(jìn)行鍵合的工作。“我們正在與聚合物電介質(zhì)并行工作,以做同樣的事情,” Brewer Science的科學(xué)家Dongshun Bai說。“它仍處于早期發(fā)展階段”。

混合鍵合的另一個優(yōu)點(diǎn)是它減少了粘接中的應(yīng)力點(diǎn),這可能導(dǎo)致焊球出現(xiàn)裂紋,特別是在拐角處。“我們聽說過橫向?qū)R等重大挑戰(zhàn),” Bai說。“如果對準(zhǔn)小于2微米,他們可能會有一些問題。如果微凸塊連接變小,穩(wěn)定性將是一個問題”。

未來

與過去不同,當(dāng)整個芯片行業(yè)步調(diào)一致地走向下一個工藝節(jié)點(diǎn)時,有許多可能的途徑在考慮之中。現(xiàn)有節(jié)點(diǎn)的工作是使用曲線掩模形狀在光掩模上更準(zhǔn)確地打印特征。“今天,即使你畫了一個圓圈,它最終也會在面具上扭曲,”D2S首席執(zhí)行官Aki Fujimura說。“為了每次都始終如一地做到這一點(diǎn),它必須大得多,而這不會有用。所以你必須走到生存能力的邊緣,但是如果根據(jù)常規(guī),想要可靠它必須更大。但你的工作是讓它盡可能小。”

這就是曲線面罩的適用范圍。使用多光束電子束,可以更準(zhǔn)確地打印掩模形狀,以基本上關(guān)閉為解釋這些不準(zhǔn)確而創(chuàng)建的空白。如果操作正確,這些技術(shù)可以幫助擴(kuò)展節(jié)點(diǎn)。

如果這還不夠,那么目前正在進(jìn)行開發(fā)工作,涉及碳納米管FET的2D材料,這些材料在所有領(lǐng)先的代工廠都受到關(guān)注。這些結(jié)構(gòu)是否真的會為主流應(yīng)用、特種芯片實(shí)現(xiàn),還是根本就要不會實(shí)現(xiàn),還有待觀察。雖然使用特殊材料對不同晶體管結(jié)構(gòu)的研究仍在繼續(xù),但領(lǐng)先的 代工廠正在尋求架構(gòu)和先進(jìn)封裝作為可能的前進(jìn)道路,無論是否有OSAT的幫助。

看起來,競爭正在升溫而不是消退,并且正在以盡可能低的成本和最大的可靠性快速“大規(guī)模定制”半導(dǎo)體。現(xiàn)在的問題是,哪條路是最好的前進(jìn)道路,這還有待證明。

審核編輯 :李倩

-

芯片

+關(guān)注

關(guān)注

459文章

52323瀏覽量

438243 -

晶體管

+關(guān)注

關(guān)注

77文章

9996瀏覽量

141058 -

繪圖板

+關(guān)注

關(guān)注

0文章

3瀏覽量

3020

原文標(biāo)題:根本性變革:芯片架構(gòu)、晶體管、材料的巨大變化

文章出處:【微信號:ICViews,微信公眾號:半導(dǎo)體產(chǎn)業(yè)縱橫】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

下一代高速芯片晶體管解制造問題解決了!

下一代PX5 RTOS具有哪些優(yōu)勢

納米壓印技術(shù):開創(chuàng)下一代光刻的新篇章

百度李彥宏談訓(xùn)練下一代大模型

使用下一代GaNFast和GeneSiC Power實(shí)現(xiàn)電氣化我們的世界

蘋果將推出M4 Ultra芯片,強(qiáng)化下一代Mac Pro與Mac Studio性能

西門子EDA發(fā)布下一代電子系統(tǒng)設(shè)計(jì)平臺

控制當(dāng)前和下一代功率控制器的輸入功率

通過電壓轉(zhuǎn)換啟用下一代ADAS域控制器應(yīng)用說明

實(shí)現(xiàn)下一代具有電壓電平轉(zhuǎn)換功能的處理器、FPGA 和ASSP

實(shí)現(xiàn)具有電平轉(zhuǎn)換功能的下一代無線信標(biāo)

通過下一代引線式邏輯IC封裝實(shí)現(xiàn)小型加固型應(yīng)用

IaaS+on+DPU(IoD)+下一代高性能算力底座技術(shù)白皮書

國科微AI首席科學(xué)家邢國良:打造全系邊端AI芯片,賦能下一代自動駕駛

下一代芯片會什么樣子,什么時候能實(shí)現(xiàn)?

下一代芯片會什么樣子,什么時候能實(shí)現(xiàn)?

評論