Integrity 3D-IC 平臺(tái)

提供了一系列三維堆疊設(shè)計(jì)流程,通過(guò)將二維芯片網(wǎng)表分解成雙層的三維堆疊結(jié)構(gòu),用戶可以探索三維堆疊裸片系統(tǒng)相對(duì)于傳統(tǒng)二維設(shè)計(jì)的性能優(yōu)勢(shì),改善內(nèi)存延遲,實(shí)現(xiàn)性能突破。

從二維設(shè)計(jì)中分離出存儲(chǔ)單元,并自動(dòng)將其劃分為兩個(gè)工藝層,上層放置存儲(chǔ)單元 Macro Cells,下層放置邏輯運(yùn)算單元 Standard Cells。該流程可以實(shí)現(xiàn)兩個(gè)裸片同時(shí)進(jìn)行的時(shí)序驅(qū)動(dòng)單元擺放。用戶還可以進(jìn)一步運(yùn)行標(biāo)準(zhǔn)的實(shí)現(xiàn)步驟,如時(shí)鐘樹(shù)綜合、時(shí)序優(yōu)化、布線等,將其作為傳統(tǒng)布局布線流程來(lái)完成三維堆疊設(shè)計(jì)實(shí)現(xiàn)。

今天我們來(lái)介紹 Integrity 3D-IC 的特色功能之一:

Memory-on-Logic 三維芯片堆疊設(shè)計(jì)流程

What is Memory-on-Logic?

Memory 指的是記憶存儲(chǔ)單元;Logic 指的是運(yùn)算單元或處理單元。

Memory-on-logic(MoL)堆疊顧名思義,就是將存儲(chǔ)單元通過(guò)三維堆疊的設(shè)計(jì)方式,放置在運(yùn)算單元所在裸片的上層裸片中,從而實(shí)現(xiàn)三維集成電路的三維堆疊結(jié)構(gòu)。

Why is Memory-on-Logic?

我們現(xiàn)在正處于高速發(fā)展的人工智能時(shí)代,對(duì)計(jì)算機(jī)算力的需求日益旺盛,同時(shí)也對(duì)相關(guān)的集成電路芯片提出了更高的性能要求。

然而算力需求的快速增長(zhǎng)和有限的算力提升速度形成了尖銳的矛盾,其具體表現(xiàn)在兩個(gè)方面:一是如今的摩爾定律越來(lái)越難以維系,器件尺寸微縮越來(lái)越困難;二個(gè)是現(xiàn)有的計(jì)算機(jī)架構(gòu)——馮諾依曼存算分離架構(gòu)的缺陷開(kāi)始凸顯,出現(xiàn)了所謂的內(nèi)存墻限制(Memory Wall Limitation)。

MoL 三維堆疊結(jié)構(gòu)為上述瓶頸提供了解決思路。對(duì)于后摩爾時(shí)代背景下的工藝瓶頸,三維堆疊可以有效提升單位投影面積中晶體管的數(shù)目,3D-IC 從方法學(xué)角度提供了一種延續(xù)摩爾定律的可能;對(duì)于存算分離所引起的內(nèi)存墻限制,通過(guò)把存儲(chǔ)單元通過(guò)三維堆疊放置到邏輯運(yùn)算單元的正上方,盡可能縮短數(shù)據(jù)傳輸距離,從而進(jìn)一步提升芯片性能,降低數(shù)據(jù)傳輸?shù)墓摹4送猓ㄟ^(guò) 3D-IC Memory-on-Logic 結(jié)構(gòu)還可以對(duì)上下裸片采用不同的工藝制程,從而降低整體芯片的制造成本。

How to do Memory-on-Logic?

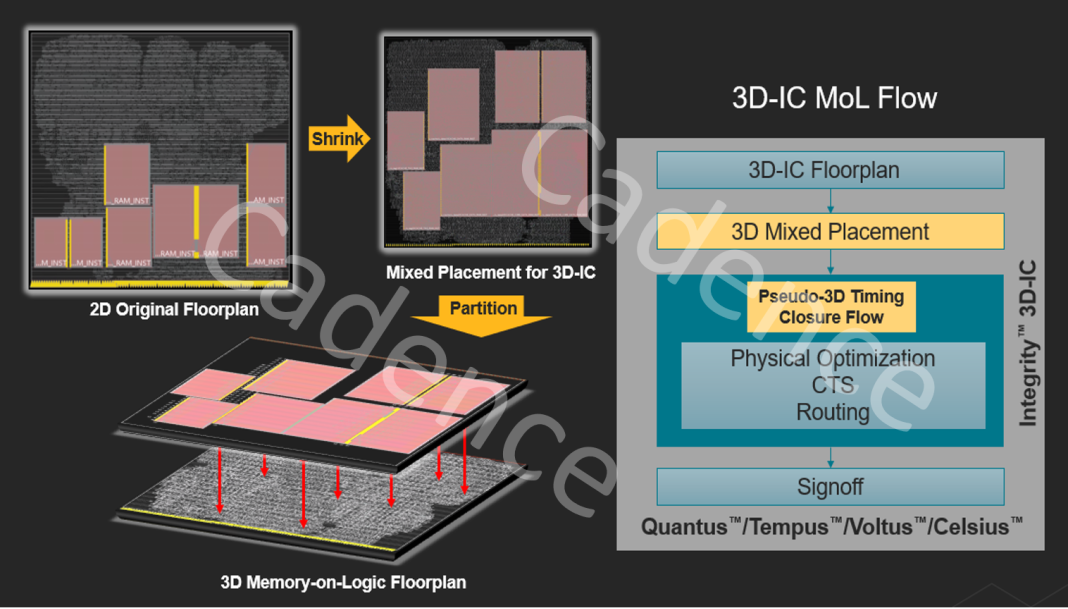

后端實(shí)現(xiàn)流程如下圖所示,對(duì)比傳統(tǒng)二維芯片,三維 MoL 芯片基于 3D-IC 專用物理后端實(shí)現(xiàn)平臺(tái)——Integrity 3D-IC,從 floorplan 階段開(kāi)始就加入 3D-IC 的設(shè)計(jì)方法,通過(guò) 3D Mixed Placer 引擎同時(shí)進(jìn)行 Macro Cells 和 Standard Cells 的自動(dòng)布局,建立 Pseudo-3D 時(shí)序收斂流程,從而實(shí)現(xiàn) 3D-IC MoL 的迭代優(yōu)化、時(shí)鐘樹(shù)綜合、自動(dòng)繞線等步驟,在簽核階段還可以通過(guò) Integrity 3D-IC 平臺(tái)來(lái)調(diào)用各類 Signoff 工具實(shí)現(xiàn)各項(xiàng)簽核。

1. 3D Mixed Placement

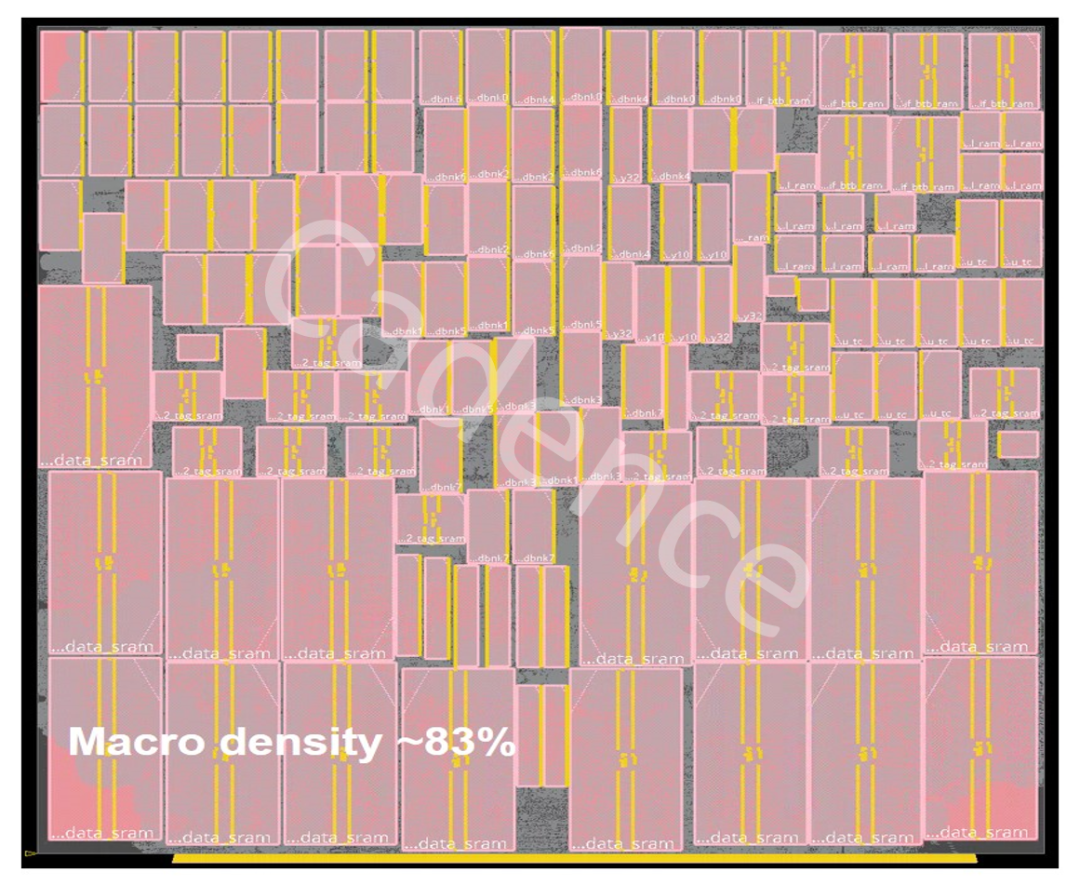

規(guī)劃 Floorplan 是傳統(tǒng)數(shù)字后端實(shí)現(xiàn)流程早期的一個(gè)重要階段,主要目標(biāo)之一便是 Macro Cells 的放置。傳統(tǒng) Floorplan 的規(guī)劃需要經(jīng)過(guò)設(shè)計(jì)工程師多次的設(shè)計(jì)迭代,從而獲得一個(gè)互連線長(zhǎng)盡量短、時(shí)序盡量收斂的 Floorplan 以供之后階段進(jìn)行自動(dòng)布局布線。如今,采用 Mixed Placement 實(shí)現(xiàn)流程,Macro Cells 和 Standard Cells 通過(guò)由擁塞、互連線長(zhǎng)和時(shí)序驅(qū)動(dòng)的 Mixed Placer 引擎同時(shí)進(jìn)行放置,與傳統(tǒng)流程相比,Mixed Placement 可以大量減少設(shè)計(jì)工程師的手動(dòng)工作量,從而實(shí)現(xiàn)更短的項(xiàng)目實(shí)現(xiàn)時(shí)間,并達(dá)到相當(dāng)甚至更好的性能質(zhì)量。而在最新的 Integrity 3D-IC 實(shí)現(xiàn)平臺(tái),Mixed Placement 功能可以完美繼承到 3D-IC MoL 實(shí)現(xiàn)流程中,在進(jìn)行 3D-IC Placement 的過(guò)程中幫助工程師用盡可能短的時(shí)間,獲得滿足要求的 Floorplan。3D-IC MoL Mixed Placement 引擎同樣由時(shí)序驅(qū)動(dòng),同時(shí)擺放 Macro Cells 和 Standard Cells,同時(shí)如圖中所示,還能支持在上層裸片中 80% 以上的高密度放置。

2. Pseudo-3D Timing Closure Flow

在完成初步的 3D-IC MoL Floorplan 之后,可以在 Integrity 3D-IC 平臺(tái)中通過(guò)命令來(lái)建立 Pseudo-3D 時(shí)序收斂流程,完成 3D-IC MoL 的版圖實(shí)現(xiàn)。主要分為 3D 層次化結(jié)構(gòu)的重建、Bump 物理位置分配、Pseudo-3D 自動(dòng)布局布線、以及 3D-IC 數(shù)據(jù)庫(kù)的建立。

01 重建 3D 層次化結(jié)構(gòu)

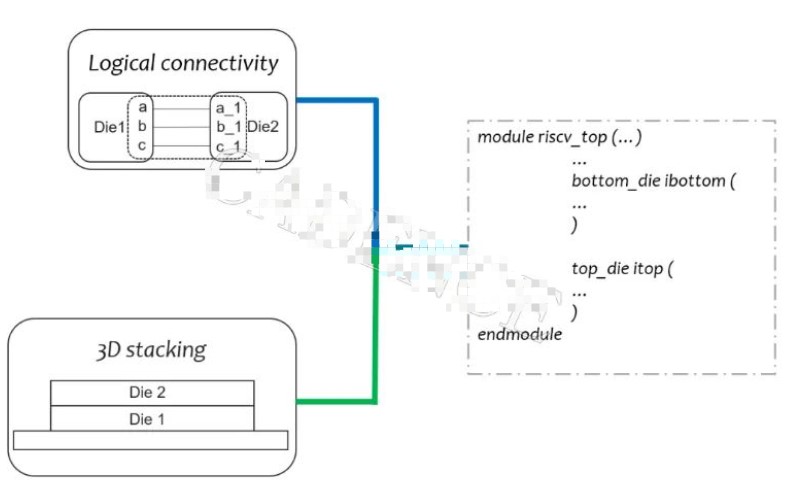

相較于傳統(tǒng)芯片的設(shè)計(jì),3D-IC 設(shè)計(jì)的層次化結(jié)構(gòu)的不同是顯而易見(jiàn)的。3D-IC 設(shè)計(jì)由于會(huì)將芯片分為上下兩個(gè)裸片—— Top Die 和 Bottom Die,天生就需要建立兩個(gè)單元模塊。工具會(huì)根據(jù)用戶的設(shè)定,建立兩個(gè)新的 Top-Level hInsts,隨后將所有設(shè)計(jì)中的 Macro Cells 歸入 Top hInst 中;剩下所有的 Standard Cells,在保留原有的層次化結(jié)構(gòu)的基礎(chǔ)上,全部歸入Bottom hInst 中,其下級(jí)可繼承保持原始設(shè)計(jì)中的所有層次化結(jié)構(gòu)。

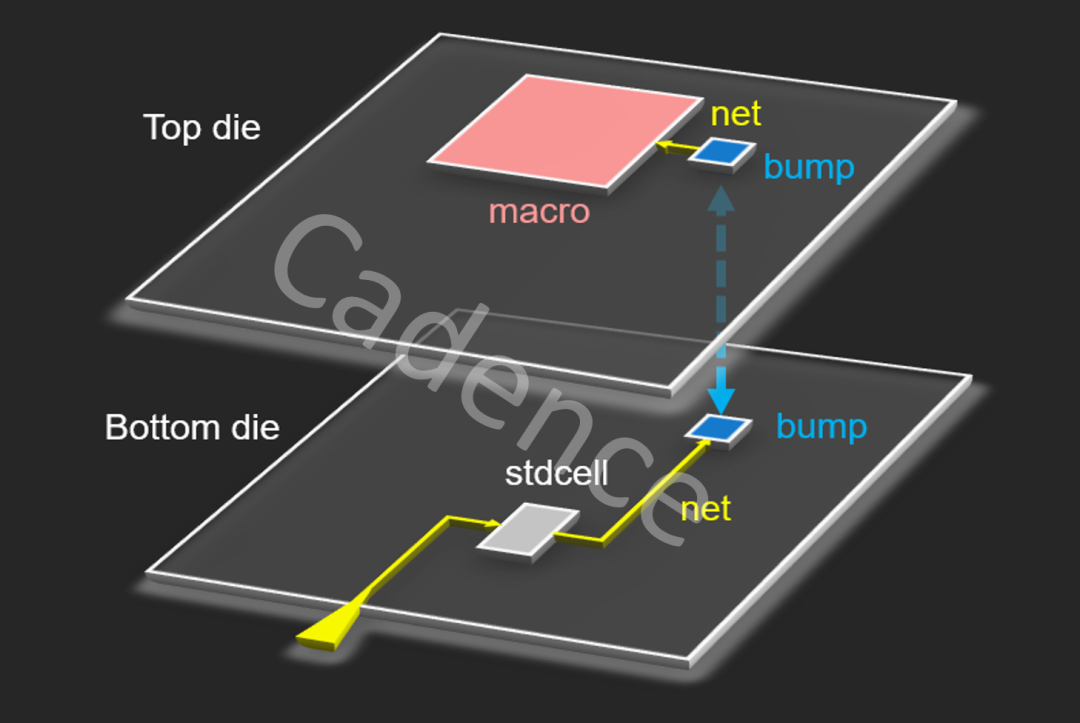

02 分配 Bump 物理位置

從結(jié)構(gòu)層面上實(shí)現(xiàn)三維分組之后,三維堆疊的互連問(wèn)題也必須考慮。為了將上下裸片連接起來(lái),最常用的方式是在頂部金屬層上通過(guò)微米量級(jí)尺寸的 Micro Bump 實(shí)現(xiàn)上下層“面對(duì)面”(Face-to-Face)的堆疊連接,由此實(shí)現(xiàn)數(shù)據(jù)和電源電信號(hào)跨層傳輸。在 Pseudo-3D 流程中,所選用的 Bump Cells 的物理位置需要在做實(shí)際繞線之前就固定好,并記錄其坐標(biāo)信息。設(shè)計(jì)者不需要手動(dòng)分配規(guī)劃 Bump 的位置,Integrity 3D-IC 可以自動(dòng)地將 Bump 邏輯連接關(guān)系插入跨層的時(shí)序路徑中,并能根據(jù)設(shè)計(jì)師提供的 Floorplan 中單元的已有位置,同時(shí)在上下兩個(gè)裸片上,智能地分配和優(yōu)化 Bump Cells 的物理位置,做到高效的流程,自動(dòng)的實(shí)現(xiàn),智能的優(yōu)化。

03 Pseudo-3D 自動(dòng)布局布線

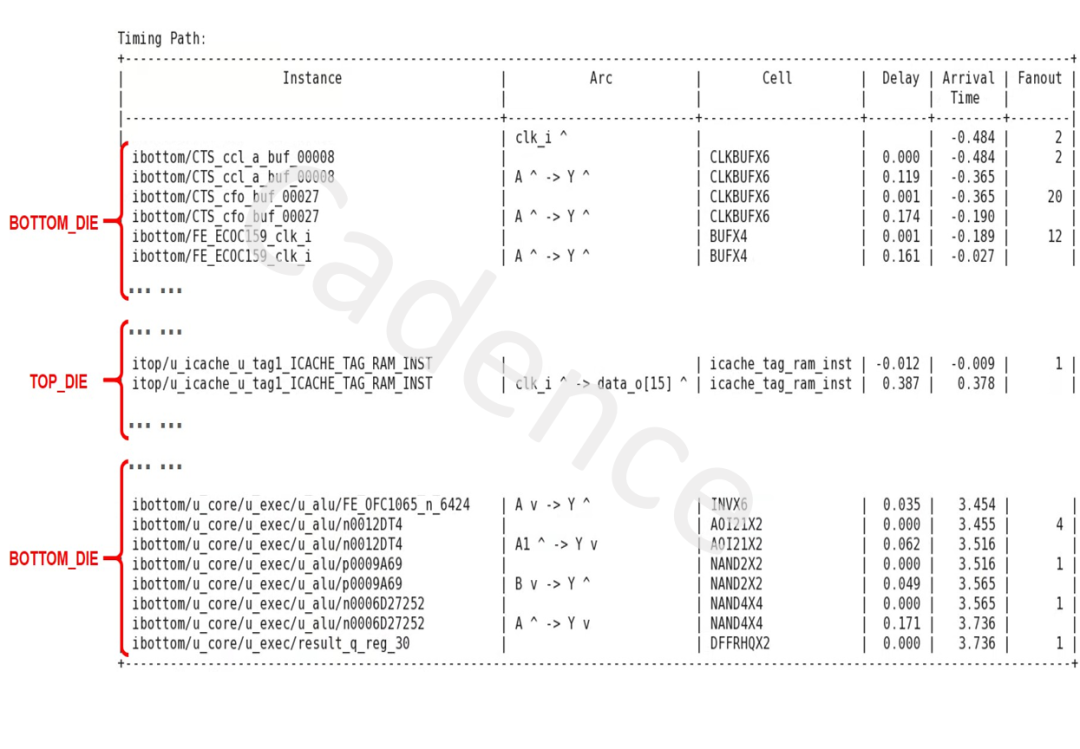

工作準(zhǔn)備就緒后,我們就可以利用帶有 Bump Cells 信息的 Pseudo-3D Floorplan 進(jìn)行自動(dòng)布局布線,Integrity 3D-IC 平臺(tái)可以調(diào)用各種相應(yīng)的傳統(tǒng)二維布局布線引擎,完成 Placement、CTS、Routing 以及相應(yīng)的設(shè)計(jì)優(yōu)化。同時(shí),Integrity 3D-IC 也可以支持跨層的時(shí)序路徑的報(bào)告分析,支持顯示例化單元 Instances 和路徑所在的結(jié)構(gòu)層級(jí),幫助工程師完成靜態(tài)時(shí)序分析。此外,Integrity 3D-IC 還支持跨層路徑的并行時(shí)序優(yōu)化,確保 3D-IC 設(shè)計(jì)的時(shí)序收斂。

04 建立 3D-IC 數(shù)據(jù)庫(kù)

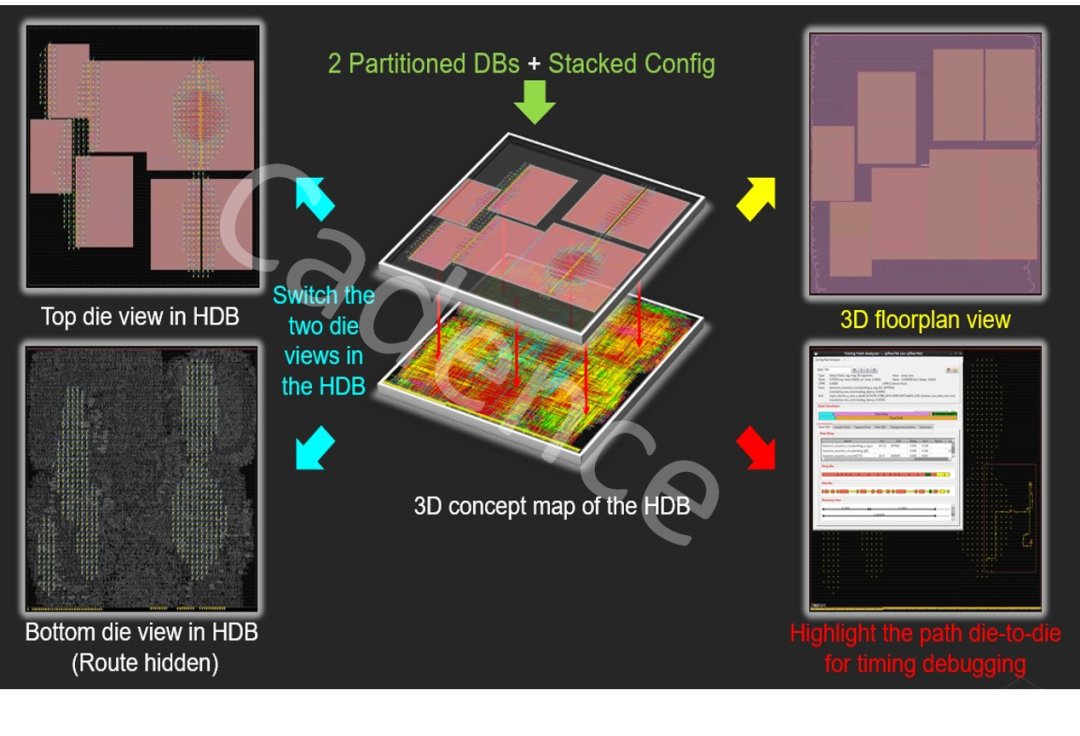

最后一步,根據(jù)優(yōu)化后的自動(dòng)布局布線結(jié)果,建立 3D-IC 專用數(shù)據(jù)庫(kù)——Hierarchical Database(HDB)。這個(gè)數(shù)據(jù)庫(kù)中就包含了包括整個(gè)設(shè)計(jì)的工藝庫(kù)信息,3D-IC 的堆疊信息,Bump 坐標(biāo)信息,物理布局布線等設(shè)計(jì)信息等等。在通過(guò)Integrity 3D-IC 創(chuàng)建好用以明確 3D-IC 的堆疊對(duì)應(yīng)信息的 Stacked Config 文件之后,需要將完成了布局布線的 pseudo-3D 數(shù)據(jù)庫(kù)進(jìn)行 Partition 拆分操作,將它按照上下裸片拆分成兩個(gè)數(shù)據(jù)庫(kù),即 Top Die Database 和 Bottom Die Database。

將這兩個(gè)完成 Partition 拆分的數(shù)據(jù)庫(kù)以及 Stacked Config 文件讀入 Integrity 3D-IC 中,合成創(chuàng)建 HDB 數(shù)據(jù)庫(kù)。在 Integrity 3D-IC 平臺(tái)中加載此數(shù)據(jù)庫(kù),就可以實(shí)現(xiàn) 3D-IC 設(shè)計(jì)的查看,包括可以實(shí)現(xiàn)在工具中上下兩層 Floorplan 視圖的切換,觀察每層中的單元擺放、繞線等后端實(shí)現(xiàn)細(xì)節(jié);也可以對(duì)包含三維堆疊信息的整體 3D Floorplan 視圖進(jìn)行直接查看;此外傳統(tǒng)的時(shí)序調(diào)試器(Timing Debugger)也支持在 3D-IC HDB 中高亮跨層的時(shí)序路徑,幫助工程師完成時(shí)序檢查和設(shè)計(jì)調(diào)整,也可以進(jìn)一步調(diào)用其他 Signoff 工具,完成后續(xù)簽核工作。

存算一體和近存計(jì)算是解決 CPU / GPU / NPU 總線和大規(guī)模片上網(wǎng)絡(luò)擁塞的有效手段。

通過(guò) Integrity 3D-IC 特有的內(nèi)存單元邏輯單元三維布局優(yōu)化,芯片設(shè)計(jì)師可以更容易的實(shí)現(xiàn)高性能高帶寬的系統(tǒng)設(shè)計(jì),從而或者縮小原有系統(tǒng)封裝面積或者進(jìn)一步提高原有系統(tǒng) PPA。

Cadence Integrity 3D-IC 平臺(tái)提供了一個(gè)高效的解決方案,用于部署 3D 設(shè)計(jì)和分析流程,以實(shí)現(xiàn)強(qiáng)大的硅堆疊設(shè)計(jì)。該平臺(tái)是 Cadence 數(shù)字和簽核產(chǎn)品組合的一部分,支持 Cadence 公司的智能系統(tǒng)設(shè)計(jì)戰(zhàn)略(Intelligent System Design),旨在實(shí)現(xiàn)系統(tǒng)驅(qū)動(dòng)的卓越 SoC 芯片設(shè)計(jì)。

-

芯片

+關(guān)注

關(guān)注

459文章

52306瀏覽量

437806 -

集成電路

+關(guān)注

關(guān)注

5420文章

11991瀏覽量

367566 -

三維

+關(guān)注

關(guān)注

1文章

517瀏覽量

29389

原文標(biāo)題:3D-IC 設(shè)計(jì)之 Memory-on-Logic 堆疊實(shí)現(xiàn)流程

文章出處:【微信號(hào):gh_fca7f1c2678a,微信公眾號(hào):Cadence楷登】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

如何建立正確的3D-IC設(shè)計(jì)實(shí)現(xiàn)流程和實(shí)現(xiàn)項(xiàng)目高效管理的挑戰(zhàn)

Cadence 憑借突破性的 Integrity 3D-IC 平臺(tái)加速系統(tǒng)創(chuàng)新

Cadence發(fā)布突破性新產(chǎn)品 Integrity 3D-IC平臺(tái),加速系統(tǒng)創(chuàng)新

Cadence Integrity 3D-IC平臺(tái)?支持TSMC 3DFabric技術(shù),推進(jìn)多Chiplet設(shè)計(jì)

Cadence Integrity 3D-IC平臺(tái)進(jìn)行工藝認(rèn)證

Integrity?3D-IC平臺(tái)助力設(shè)計(jì)者實(shí)現(xiàn)驅(qū)動(dòng)PPA目標(biāo)

Cadence Integrity 3D-IC自動(dòng)布線解決方案

Cadence擴(kuò)大與Samsung Foundry的合作,共同推進(jìn)3D-IC設(shè)計(jì)

Cadence Integrity 3D-IC Platform榮膺“年度EDA/IP/軟件產(chǎn)品”

3D-IC未來(lái)已來(lái)

聯(lián)華電子和Cadence共同合作開(kāi)發(fā)3D-IC混合鍵合(hybrid-bonding)參考流程

Cadence發(fā)布基于Integrity 3D-IC平臺(tái)的新設(shè)計(jì)流程,以支持TSMC 3Dblox?標(biāo)準(zhǔn)

Cadence 擴(kuò)大了與 Samsung Foundry 的合作,依托 Integrity 3D-IC平臺(tái)提供獨(dú)具優(yōu)勢(shì)的參考流程

3D-IC 以及傳熱模型的重要性

Integrity 3D-IC 的特色功能

Integrity 3D-IC 的特色功能

評(píng)論