摘要:針對 L頻段數字航空通信系統接收機 DME 信號干擾抑制算法缺乏真實驗證平臺這一問題,利用軟件無線電技術搭建 L?DACS1 的原型系統。按照 L?DACS1 系統前向鏈路的技術參數和超幀結構,設計實現了基于 Yun SDR320 和 Matlab的 L?DACS1 系統前向鏈路發射機和接收機的原型構建,在真實的無線信道環境下實現信號的發送與接收。測試結果表明,所設計的 L?DACS1系統前向鏈路平臺符合系統規范、工作穩定,該平臺可以用作未來 DME干擾抑制算法的驗證平臺。

0 引 言

為了保障民用航空器安全、可靠、高效的運行,提升空 域 容 量 ,國 際 民 航 組 織(International Civil AviationOrganization,ICAO)將L頻段數字航空通信系統(L?bandDigital Aeronautical Communication System,L?DACS)確立為未來航空移動通信主要依賴的技術手段之一[1]。目前,L?DACS 有兩種候選技術方案:一種是基于多載波調制技術的L?DACS1[2];另一種是基于單載波高斯最小頻移鍵控的 L?DACS2[3]。其中,L?DACS1因其具有傳輸容量大、抗多徑能力強、頻譜效率高的優點而獲得航空制造業和學術界的廣泛關注[4]。由于L?DACS1系統的工作頻譜與L頻段已 有 的 DME(Distance MeasureEquipment,DME)系統頻譜存在部分交疊[5],導致 DME信號對L?DACS1系統接收機產生了不可避免的干擾。

目前,國內外針對L?DACS1系統接收機如何抑制DME信號干擾的問題提出了很多算法,例如:脈沖熄滅與脈沖限幅干擾抑制算法[6]、壓縮感知信號重構干擾抑制算法[7]、判決反饋脈沖噪聲估計干擾抑制算法[8]等,這些干擾抑制算法的研究主要通過理論分析與仿真相結合的方式,并沒有搭建真實的測試平臺驗證其有效性。為了更深入地研究DME信號對L?DACS1系統接收機性能的影響,本文根據L?DACS1系統規范[2],基于軟件無線電 Yun SDR320平臺和Matlab軟件平臺設計實現了L?DACS1系統前向鏈路的發射機與接收機,發射機產生發射信號并經過真實的無線信道后由接收機接收。該平臺可以驗證L?DACS1系統發射機和接收機的性能,也為進一步驗證和比較不同DME干擾抑制算法的有效性提供了一個真實的環境平臺。

1 Yun SDR 軟件無線電平臺

軟件無線電是指在硬件條件不變的前提下,通過軟件編程對物理硬件進行配置來實現各種無線電功能[9]。利用軟件無線電技術,通過軟件平臺實現通信系統鏈路的各種功能,包括信號的產生、調制解調、編碼譯碼、濾波等。

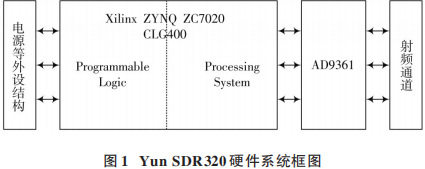

北京威視銳科技公司的產品Yun SDR320實驗平臺是專為無線通信系統研究而開發的一款便攜式軟件無線電平臺。Yun SDR320通過千兆以太網線與PC機進行數據交互,由于其具有更寬的頻譜范圍和模擬帶寬而受到廣泛應用。Yun SDR320實驗平臺的基本硬件結構由 ZYNQ 嵌入式處理器、AD9361[10]射頻前端和電源電路三部分構成。其中,嵌入式處理器采用 Xilinx ZYNQZC7Z020 CLG400型號的SoC芯片完成信源的數字基帶信號處理過程。射頻前端采用 ADI公司的 AD9361芯片實現數字信號處理、數字上/下變頻、數/模和模/數轉換、濾波、射頻收發等功能。Yun SDR320的硬件系統框圖如圖 1所示。

2 L?DACS1系統前向鏈路物理層傳輸特性

L?DACS1是一個基于正交頻分復用(OrthogonalFrequency Division Multiplexing,OFDM)多載波傳輸技術的航空移動通信系統,采用頻分雙工(Frequency ?Division Duplex,FDD)的通信方式[2]。系統前向鏈路采用OFDM傳輸技術,基本數據傳輸單元是超幀,工作頻段為985.5~1 085.5MHz,比特傳輸速率為303~1373Kb/s。

2.1 L?DACS1系統前向鏈路物理層技術參數

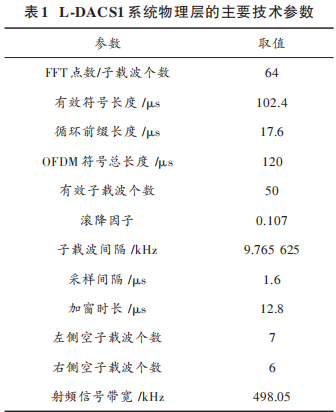

L?DACS1系統物理層的主要技術參數如表1所示。

L?DACS1系統前向鏈路OFDM系統子載波總數為64個,其中包含50個有效子載波,14個直流子載波和空子載波,子載波間隔為9.765 625 kHz,射頻信道帶寬為498.05kHz。OFDM 符號總長度為120 μs,其中有效符號長度為102.4 μs,循環前綴長度為17.6 μs。

2.2 L?DACS1系統前向鏈路幀結構

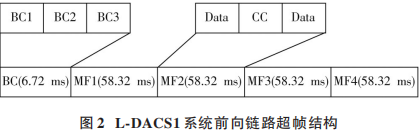

L?DACS1系統前向鏈路的超幀結構如圖2所示。每個超幀由1個廣播(BC)幀和4個多幀(MF)組成,其中,廣播幀用于傳輸前向鏈路的廣播信息,多幀用于承載高層的調制符號。每個廣播幀的持續時間為6.72ms,由3個子幀組成,分別是BC1、BC2和BC3,BC1和BC3子幀完全相同,持續時間為1.8 ms,BC2子幀的持續時間為3.12 ms。每個多幀的持續時間為58.32 ms,由9個長度可變的Data/CC子幀組成,Data/CC子幀的持續時間為6.48 ms。每個超幀的持續時間為240 ms,可以傳輸的OFDM符號總數為2000個。

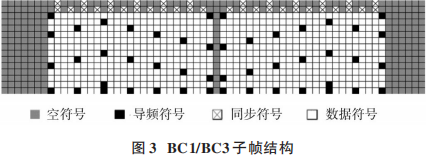

BC1/BC3子幀結構如圖3所示,每個子幀包含三部分:同步符號、數據符號和導頻符號。其中,同步符號用于接收機建立超幀同步,定位幀頭的準確起始位置;數據符號用于承載高層的比特信息;導頻符號用于接收機進行信道估計。

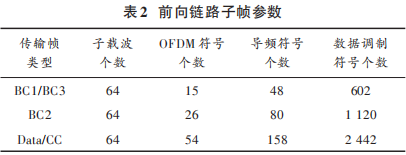

BC2、Data/CC 子幀結構與BC1/BC3子幀結構類似,其參數如表2所示。

3 系統設計與實現

3.1 系統平臺結構設計

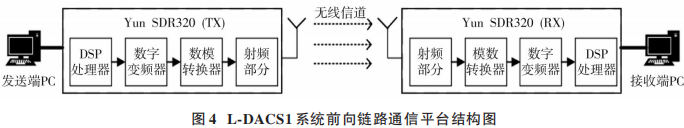

L?DACS1系統前向鏈路通信平臺主要包括兩個部分,即PC端和Yun SDR320設備,其結構示意圖如圖4所示。

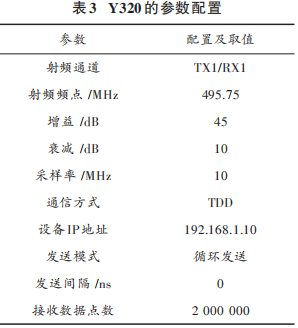

在發射端,由發送端PC產生的數字基帶信號通過千兆以太網線送入DSP處理器完成數字調制,再由數字上變頻器將基帶信號轉變為中頻信號,之后經過數模轉換器轉換為模擬信號,通過射頻部分將模擬信號放大到足夠功率,由天線發射到無線信道中。在接收端,由天線接收到的無線電信號經過射頻放大后對其進行模/數轉換,數字化之后的信號經過數字下變頻器將中頻信號轉變為基帶信號,然后將基帶信號送入DSP處理器完成數字解調,將解調后的信號通過千兆以太網線送入接收端PC恢復出原始發送序列。Y320的參數配置如表3所示。

3.2 發射機的實現

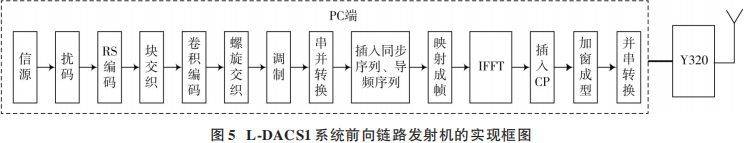

L?DACS1系統前向鏈路發射機主要由編碼交織、調制、映射成幀和加窗成型幾部分構成,其實現框圖如圖5所示。

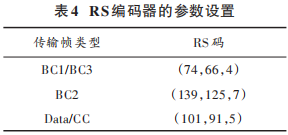

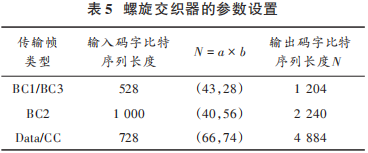

為了將傳輸的比特序列隨機化,信源產生的比特序列首先經過比特擾碼處理;選擇合適的編碼方式,其中,外編碼采用RS編碼,其參數設置如表4所示,內編碼采用(171,133,7)卷積碼;之后根據傳輸幀的類型選擇合適的交織方式,其中,廣播(BC)幀采用的交織方式為螺旋交織,Data/CC幀采用的交織方式為塊交織與螺旋交織,其參數設置如表5所示。

對編碼和交織后的比特序列進行符號調制;將符號調制后的序列與生成的導頻序列、同步序列分別映射到BC1、BC2、BC3子幀及Data/CC子幀;根據L?DACS1系統前向鏈路超幀結構將各子幀組合成為一個超幀,再將超幀通過IFFT完成OFDM符號調制;最后插入循環前綴(CP),進行時域加窗處理,通過并/串轉換將并行數據轉換為串行數據,通過千兆以太網線傳送到Y320。至此實現了L?DACS1系統前向鏈路的發射機部分設計。

3.3 接收機的實現

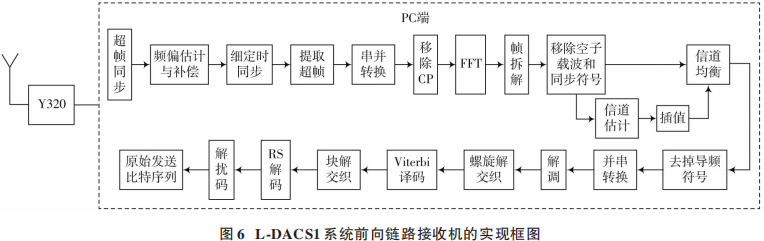

L?DACS1系統前向鏈路接收機主要由同步、信道估計、信道均衡和解調譯碼等部分構成,其實現框圖如圖6所示。

Y320接收到的信號經過千兆以太網線傳送到PC端,將得到的信號首先根據廣播(BC)幀的特定結構確定出超幀幀頭的大概起始位置,建立接收機的超幀同步,然后利用前向鏈路各數據幀的同步符號獲得接收信號的載波頻偏,并對其進行補償,之后利用同步符號進行細定時同步,確定出超幀幀頭的準確起始位置;從接收數據中提取出一個完整的超幀,并進行串并轉換,移除CP,之后通過FFT完成OFDM解調;將解調之后的超幀進行幀拆解,拆解出BC1、BC2、BC3子幀和Data/CC子幀;移除子幀中的空子載波和直流子載波,分別提取子幀中的導頻符號進行信道估計,并根據各個子信道的信道估計值進行一維線性插值,之后進行信道均衡;將信道均衡之后的數據移除導頻符號,進行并串轉換;根據傳輸幀的類型,對得到的串行數據進行解調、解交織和譯碼,其中解交織和譯碼的參數設置均與發射機保持一致;最后經過解擾恢復出原始發送比特序列。至此實現了L?DACS1系統前向鏈路的接收機部分設計。

4 測試及分析

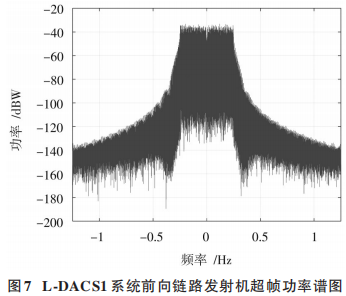

為了測試基于Y320的L?DACS1系統前向鏈路發射機與接收機設計的正確性,本文從發射機超幀功率譜圖、接收機接收信號功率譜圖和子幀星座圖的收斂程度三方面進行觀測。

L?DACS1系統前向鏈路發射機超幀功率譜圖如圖7所示。由發射機功率譜圖可以觀測出,L?DACS1系統前向鏈路的射頻信號帶寬接近0.5MHz,零頻處為直流,不傳輸任何信息,測試結果與L?DACS1系統前向鏈路發射機標準一致。

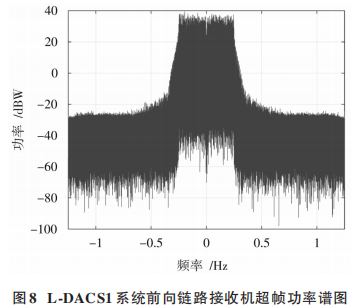

L?DACS1系統前向鏈路接收機超幀功率譜圖如圖8所示。

由接收機功率譜圖可以觀測出,接收機接收到的信號功率譜帶寬也接近0.5 MHz,零頻處為直流,證明了接收機成功接收到發射機發送在空中的調制信號。

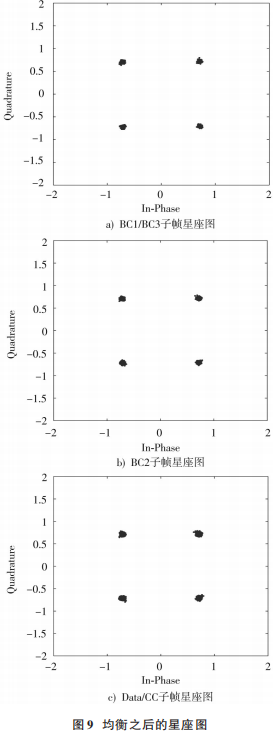

在L?DACS1系統前向鏈路發射機采用QPSK調制方式的情況下,利用子幀中的導頻符號進行信道估計和均衡之后的星座如圖9所示。

其中,圖9a)是BC1/BC3子幀均衡后的星座圖;圖9b)是BC2子幀均衡后的星座圖;圖 9c)是 Data/CC 子幀均衡后的星座圖。

由均衡之后的星座圖可以觀測出,BC1、BC2、BC3、Data/CC子幀的星座點收斂較好,滿足設計需求。

5 結 語本文按照L?DACS1系統協議規定的技術參數和超幀結構,基于軟件無線電Y320和Matlab設計實現了L?DACS1系統前向鏈路的發射機和接收機,并進行了發射機和接收機的聯調測試。通過測試發射機和接收機功率譜圖、觀測星座圖的收斂性,可以證明所設計的L?DACS1系統平臺運行有效,該平臺將用作后續算法研究的實際驗證平臺。 審核編輯 :李倩

-

接收機

+關注

關注

8文章

1219瀏覽量

54257 -

無線電

+關注

關注

60文章

2163瀏覽量

117696

原文標題:論文速覽 | 基于 Yun SDR 的 L?DACS1系統前向鏈路平臺的設計與實現

文章出處:【微信號:現代電子技術,微信公眾號:現代電子技術】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

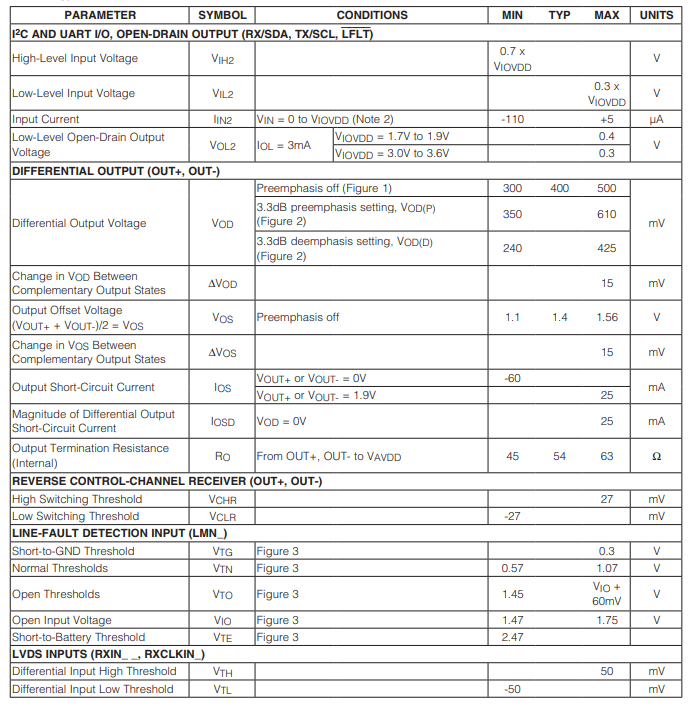

MAX9249多媒體串行鏈路串行器,帶有LVDS系統接口技術手冊

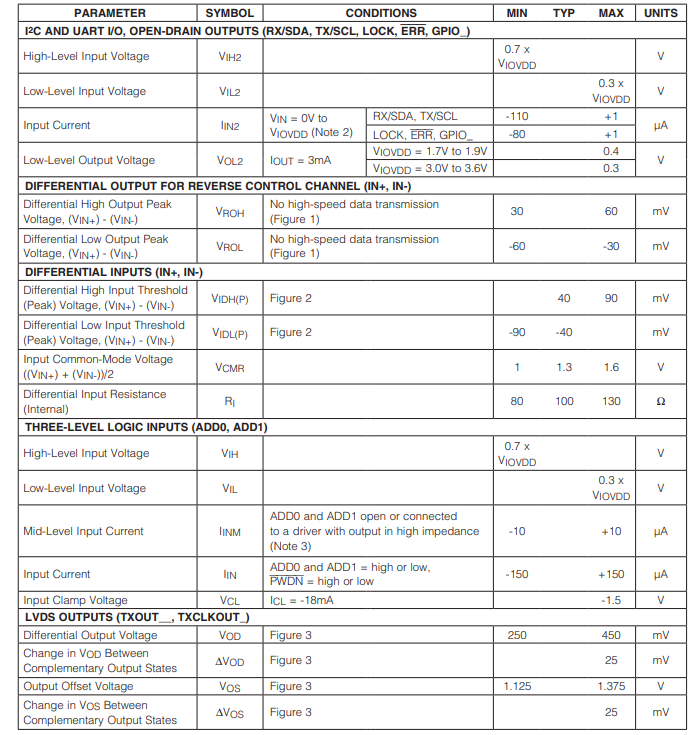

MAX9268多媒體串行鏈路解串器,具有LVDS系統接口技術手冊

基于Yun SDR的L?DACS1系統前向鏈路平臺的設計與實現

基于Yun SDR的L?DACS1系統前向鏈路平臺的設計與實現

評論