早在十幾年前,摩爾定律即將失效的消息就已經在業界鬧得沸沸揚揚,一晃眼,十幾年過去了,如今的芯片制程已經走到了3nm節點,并向著埃米時代邁進。看似一切都順風順水,但縱觀整個發展史,你就會發現,風生水起的背后充斥著“欺騙”、“謊言”、“混戰”、“掙扎”與“屈服”…

01陷入風波的先進工藝

有關臺積電和三星先進制程工藝“名不副實”的傳言由來已久,原本隨著先進工藝難度越來越大,相關話題的熱度也開始逐漸下降,然而今年8月,TechInsights在Blog上發表的文章卻再掀昔日浪潮。

TechInsights在對臺積電和三星的4nm工藝進行剖析和拆解后,認為兩家晶圓代工廠為了贏得彼此間的較量,因而放任客戶聲稱他們采用了4nm工藝,實際上他們所謂的4nm工藝卻仍是5nm技術。用5nm工藝假冒4nm,這件事情居然發生在了2022這個3nm量產年,不禁讓人思考如今的3nm可還好?

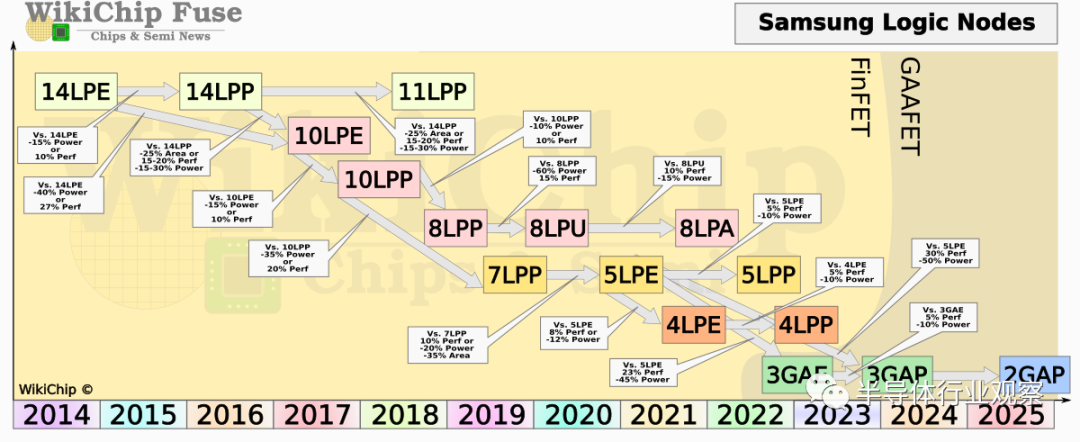

以已經宣布量產的三星3nm為例,三星官方消息顯示,與三星5nm工藝相比,第一代3nm工藝可以使功耗降低45%,性能提升23%,芯片面積減少16%;而未來第二代3nm工藝則使功耗降低50%,性能提升30%,芯片面積減少 35%。Wikichip根據官方數據粗略估計,第一代3nm 3GAE的晶體管密度約為 150 MTr/mm2,而第二代3nm 3GAP的晶體管密度約為 195 MTr/mm2。需要注意的是,英特爾2017年發布的10nm工藝的晶體管密度就已經達到了100.8Mtr/mm2。

圖源:Wikichip

Wikichip強調,由于從 FinFET 到 GAA 的過渡,因而降低高達 50% 的功率,如此大幅度的功率降低,對于三星代工來說,是自平面晶體管時代以來從未有過的。此外,就3nm性能而言,Wikichip也認為這些數字偏高,但僅略高于一些先前的節點。

臺媒《經濟日報》更是報道,分析師指出,三星的3nm制程所能達到的晶體管密度,最終可能與英特爾的制程4或者臺積電的5nm家族當中的4nm相當,但是帶寬與漏電控制表現會更好,帶來更優異的效能。

那么臺積電作為全球代工龍頭,它的3nm就毫無爭議嗎?非也。

今年6月,臺積電在2022 年技術研討會透露了其即將推出的3nm節點的部分細節。但令人感到疑惑的是,技術研討會上的大部分3nm消息都是關于 N3E ,也就是臺積電第二代3nm工藝,而關于第一代3nm的消息卻寥寥無幾。

到了今年8月,業內人士手機晶片達人在微博上爆料稱,臺積電內部決定放棄N3工藝,因為客戶都不用,轉2023下半年量產降本的N3E工藝,N3成本高,design的window又很critical,連蘋果都放棄N3工藝。雖然臺積電在論壇上辟謠了該說法,但最新消息顯示,蘋果A17芯片將有可能直接采用臺積電最先進的N3E工藝打造。

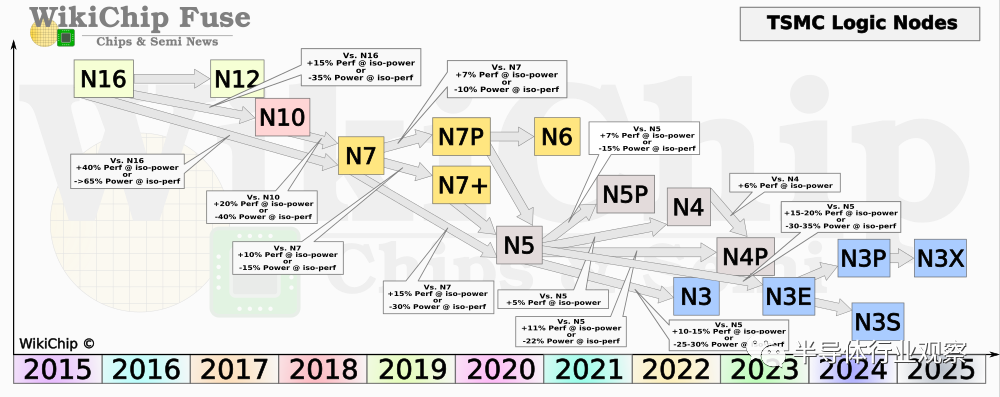

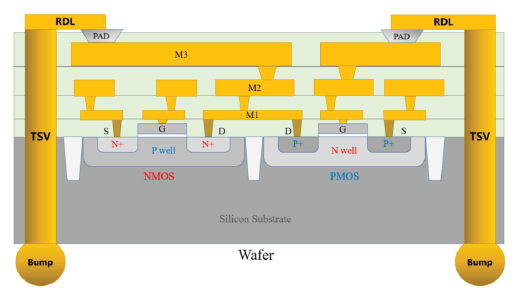

N3節點是臺積電于2018-2019 年宣布,預計在今年下半年量產的第一代3nm節點,與臺積電的 Vanilla N5 節點相比,原始 N3 節點在 ISO 功率下可將速度提高約10-15%,數字邏輯的密度提高了約 1.7 倍,模擬邏輯的密度提高了約 1.1倍。鑒于臺積電尚未公開任何設計規則,Wikichip粗略估計N3的晶體管密度范圍約為 180-220 MTr/mm2。

雖然臺積電方多次強調N3會在今年下半年量產,但是能否成為臺積電3nm的主流工藝仍是一個疑問,關鍵之處就是在于N3E的出現。作為臺積電第二代3nm工藝,N3E與N3有著極大的不同,消息顯示兩者之間的設計規則和IP 實現方式都有著較大的差異,這就意味著,客戶沒有直接的IP路徑可讓在N3上的設計遷移到 N3E。基于N3E,臺積電還衍生出了N3P、N3X、N3S 和 N3RF四個變體,而N3似乎已經成為一個被人遺忘的存在。

圖源:wikichip

倘若N3真的成為“棄子”,那么蘋果等手機廠商則需要等到2023年下半年才能采用3nm處理器,更重要的是,據Wikichip估計,N3E的晶體管密度會略低于 N3 密度。無論是三星還是臺積電,其3nm工藝的晶體管密度,似乎都與想象中有所偏差。

傳統上,晶體管密度可以看作是芯片整體性能的指標,被業內奉為“圭臬”的摩爾定律指的就是芯片上可容納的晶體管數目,約每隔18個月便會增加一倍,性能也將提升一倍。從這個角度來看,當前3nm確實會令人產生一定的疑惑。

02放棄“掙扎”的英特爾

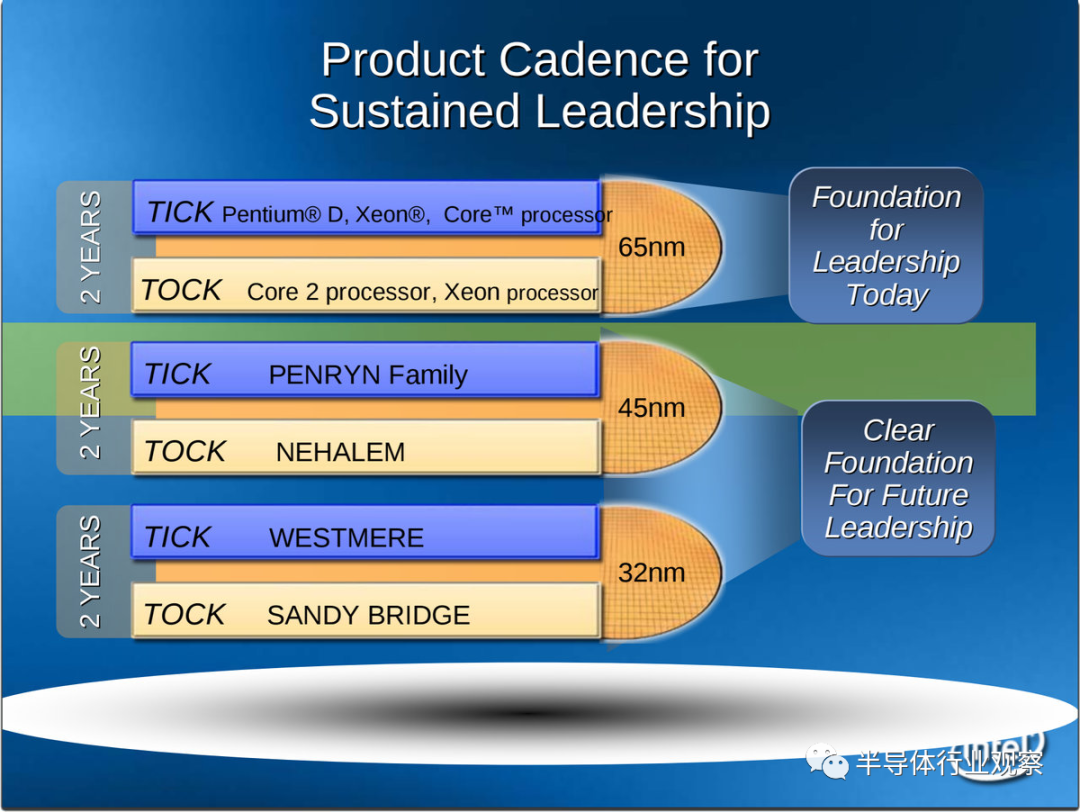

其實,在邁入先進制程之后,晶體管密度問題就一直盤旋在芯片產業的上空。英特爾作為摩爾定律堅定不移的捍衛者,在2007年曾提出著名的“Tick-Tock(制程-新架構)”節點發展周期。按照英特爾的說法,Tick-Tock 的周期兩年一循環,Tick 一年,Tock 一年。在Tick年,英特爾將會引入新的制程工藝;而在Tock年,英特爾將會使用上年更新過后的工藝推出采用全新架構的CPU。

圖源:英特爾

按照Tick-Tock模式,英特爾工藝制程從65nm發展到22nm,但卻在14nm卡了長達7年之久,Tick-Tock模式也在2016年被新戰略PAO(Process-Architecture-Optimization 制程-架構-優化)替代。當英特爾還在困于14nm、10nm節點時,臺積電和三星卻已經從28nm/22nm,發展到16nm/14nm,并走到了7nm節點。

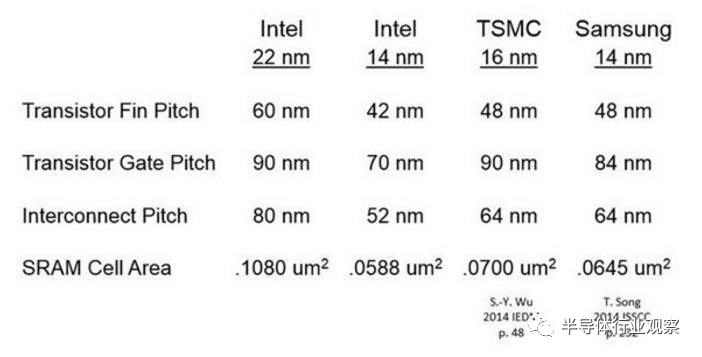

面對競爭對手在先進制程領域的大步邁進,英特爾對此表示不以為意。雖然英特爾14nm和10nm的升級周期都超過了兩年,但是對應的晶體管密度也分別提升了2.5倍和2.7倍,符合摩爾定律的對于晶體管密度的線性增長要求。對比臺積電、三星的16、14nm工藝,可以看出,英特爾的14nm工藝在這些關鍵指標要高于臺積電和三星。

圖源:電腦報

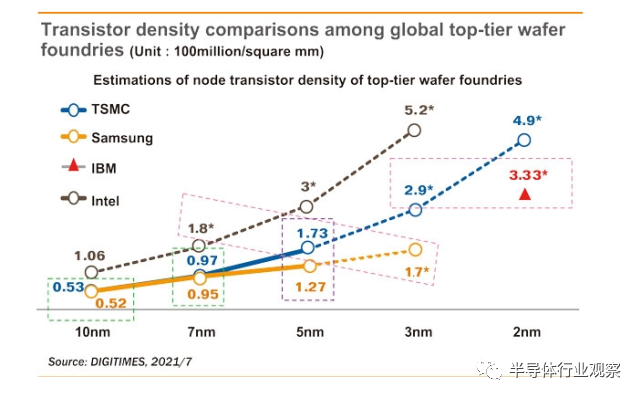

去年,Digitimes也對三家企業的芯片制造工藝做了對比,主要以晶體管密度作為參考指標,對比三家企業的10nm、7nm、5nm、3nm、2nm,其中Intel的5nm和3nm為預估值,臺積電和三星的3nm、2nm工藝為預估值。

圖源:Digitimes

Digitimes指出,在10nm工藝上,英特爾的晶體管密度就已領先于三星和臺積電,此后雙方的差距在的差距逐漸拉大。就晶體管密度而言,臺積電和三星的7nm工藝還稍微落后于英特爾的10nm工藝,到了5nm工藝上三星又與臺積電拉開了差距,并且認為三星的3nm工藝才接近臺積電的5nm工藝和英特爾的7nm工藝。

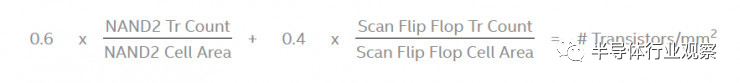

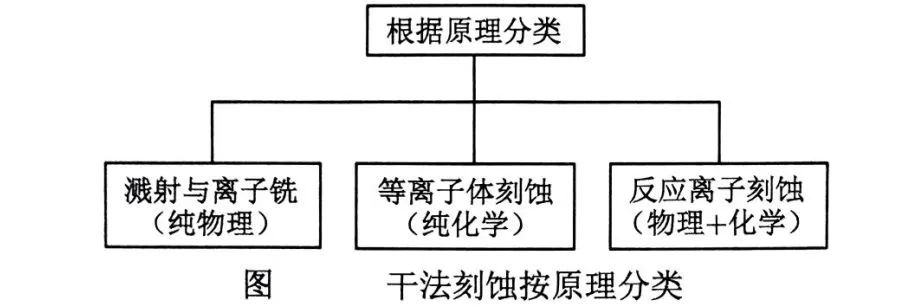

除了數據上的對比,2017年,當時的英特爾高級院士,處理器架構與集成部門主管Mark Bohr直接發布了一篇關于清理Intel工藝混亂命名的相關文章,直指業界在半導體工藝命名上的混亂狀態,并給出了一個衡量半導體工藝水平的公式:

圖源:英特爾

該公式主要分為兩部分,一部分計算2bit NAND(4個晶體管)的密度,另一部分則是用來計算的是SFF(scan flip flop)的晶體管密度,0.6和0.4兩個數字是這兩部分的加權系數。Bohr表示衡量半導體工藝真正需要的是晶體管密度。

種種數據表明,如果從晶體管密度來看,英特爾的10nm/14nm的工藝制程在當時應該都屬于拔頭籌者,但競爭對手憑借命名優勢一路高歌,反觀英特爾卻被冠上“牙膏廠”的稱謂。

到了2021年,英特爾終究放棄掙扎,選擇“同流合污”,更改了制程命名方式。英特爾未來5年技術路線圖,對芯片的制程工藝進行了新的命名,10納米Enhanced SuperFin更名為“Intel 7”、Intel 7納米更名為“Intel 4”、其后是“Intel 3”、“Intel 20A”、“Intel 18A”。

隨著英特爾的加入,如今的工藝制程命名似乎也已成定局。

03命名“游戲”的開始

當前大家所熟知的XX nm工藝,指的其實是線寬,比如3nm意思就是柵極的最小線寬為3nm。而工藝的命名方式則遵循每個世代線寬縮減約 0.7 倍的規律,0.7x0.7約等于 0.5,也就是晶體管整體面積相比上一代縮小一倍,符合摩爾定律。

雖然XX nm工藝的命名方式在半導體業內已約定俗成,但其實早在1997年,也就是350nm之后,業界就已經意識到基于納米的傳統制程節點命名方法,不再與晶體管實際的柵極長度相對應。到了2012年,隨著3D晶體管Finfet的出現,只用gate 的長度來衡量晶體管的特征尺寸已經遠遠不夠了,還需要Fin的高度,Fin 的寬度,Fin Pitch,Gate length,Gate width等各種參數。

當下,0.7 倍的命名原則仍在繼續,然而這些數據的實際意義卻已經不大了,但臺積電、三星等一眾代工廠卻從工藝命名上獲得了巨大的利益和成功。

2014年,臺積電利用其創新的雙重曝刻技術,成為世界上第一家開始批量生產20nm半導體的公司,并在同年創造了臺積電最快的產能提升記錄。憑借著20nm的優勢,臺積電從三星手中奪下了蘋果的部分訂單,臺積電2014年第四季財報顯示,合并營收約新臺幣2225.2億元,與2013年同期相比營收增加52.6%,其中20nm制程出貨占臺積電第四季晶圓銷售的21%。到了2016年,臺積電已經取代三星,成為了蘋果A系列處理器的最大芯片代工廠。2016年臺積電全年營收達到9479.38億新臺幣,同比增長12.4%,造就了當時臺積電歷史上的最高紀錄。

三星方面也是如此,在A8處理器以前,三星是蘋果處理器的獨家代工廠,卻在2014年失去了獨家地位,然而2015年憑借全球首個14nm工藝制程實現反超,重新奪回了蘋果處理器的代工業務。

眾所周知,蘋果A9處理器有兩個版本,分別是三星的14nm和臺積電的16nm,理論上講,三星的14nm性能應該高于16nm,但從當時的消息來看,消費者的口碑就截然相反,三星代工的芯片在功耗和發熱方面都不及臺積電,這其實就已反映出工藝制成的命名原則已經背離了真實工藝性能。

即便如此,臺積電和三星依舊“樂此不疲”,畢竟對于購買手機的消費者來說,絕大多數都是不會過于錙銖必較。以最新的Iphone 14來說,大家關注的大多在于只有Pro版本用上了最新A16仿生芯片,但對于A16與A15之間的性能差可能就一笑置之。

毫無疑問,商業上取得的紅利是驅動命名“游戲”開始的關鍵點,但不可否認,臺積電、三星和英特爾在整體半導體工藝的進展上也確實取得了巨大的進步,是推動整個芯片產業前進的強大引擎。

摩爾定律從提出到現在已經快60年了,隨著時間的推移,我們不得不承認工藝制程的演進正在變得越來越困難,為了延續摩爾定律,臺積電、三星、英特爾研發了各種先進技術,比如三星3nm中采用了GAA晶體管,臺積電在先進封裝領域的發力,英特爾的背面供電技術等…雖然當前芯片工藝進程或許有些受挫,但他們并沒有放棄,相反正在積極研發各式各樣的先進技術,希望有一天,會出現類似于“浸潤式光刻”那樣的顛覆性技術,能讓制程發展實現大跨越。

從某種意義上來說,或許這些巨頭延續原有的命名方式,也是他們表達捍衛摩爾定律的最后“倔強”。

04寫在最后

未來是未知的,但芯片產業向前發展是可以肯定的,我們相信未來先進制程一定會有更好的表現形式,但在下一個顛覆性技術出現之前,我們還需要臺積電、三星、英特爾等巨頭持續不斷地創新,推出新技術…

審核編輯 :李倩

-

芯片

+關注

關注

459文章

52464瀏覽量

440167 -

工藝

+關注

關注

4文章

681瀏覽量

29421 -

晶體管

+關注

關注

77文章

10015瀏覽量

141510

原文標題:芯片工藝的命名“游戲”仍將繼續…

文章出處:【微信號:算力基建,微信公眾號:算力基建】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

概倫電子先進PDK驗證平臺PQLab介紹

先進封裝工藝面臨的挑戰

IEDM 2024先進工藝探討(三):2D材料技術的進展及所遇挑戰

其利天下技術開發|目前先進的芯片封裝工藝有哪些

先進封裝中RDL工藝介紹

CoWoS先進封裝技術介紹

芯和半導體將參加2024集成電路特色工藝與先進封裝測試產業技術論壇

高速點焊工藝中先進控制電源的關鍵技術探究與應用

先進封裝中互連工藝凸塊、RDL、TSV、混合鍵合的新進展

光刻工藝的基本知識

陷入風波的先進工藝

陷入風波的先進工藝

評論