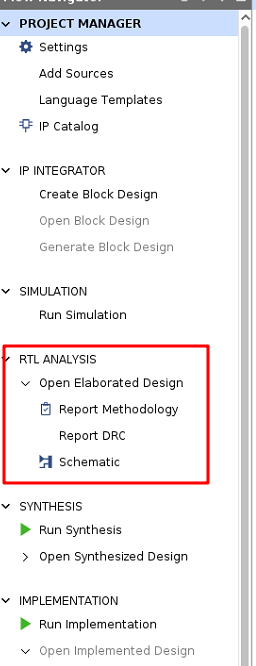

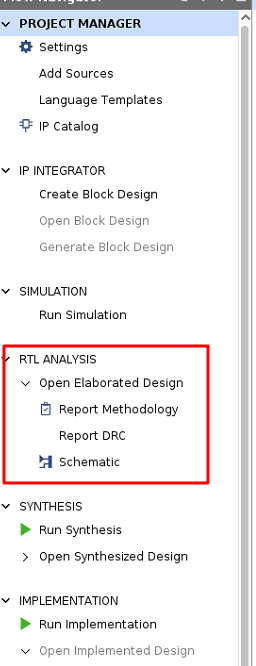

在Vivado的界面中,有個RTL ANALYSIS->Open Elaborated Design的選項,可能很多工程師都沒有使用過。因為大家基本都是從Run Synthesis開始的。

elaborate可以翻譯為“詳盡解析”,就是將RTL源代碼翻譯轉換成對應的電路。

有同學會問,這不是Synthesis做的工作嗎?

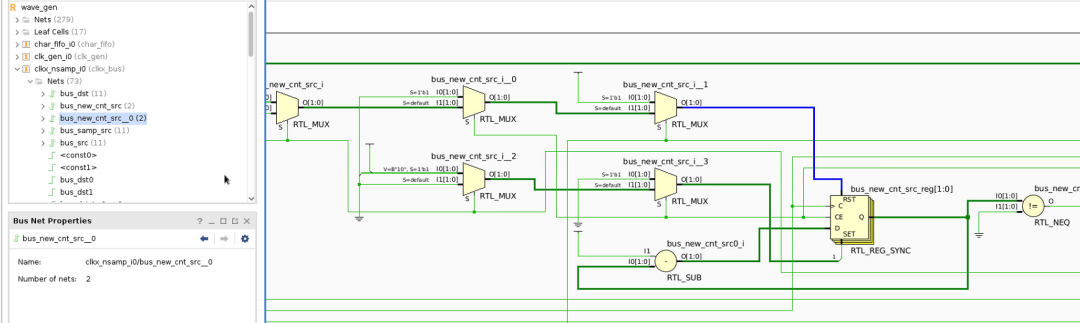

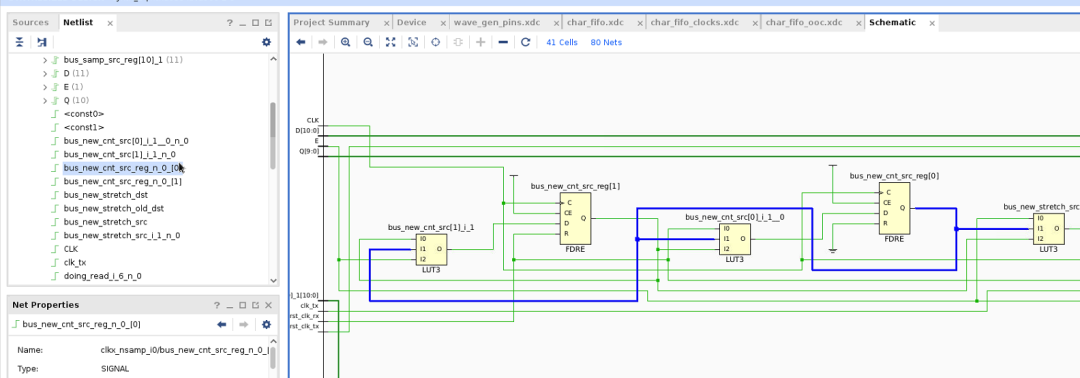

我們可以來比較一下Elaborate和Synthesis后的Schematic就很直觀了:

Elaborated Design:

image-20221023165430449

Synthesisd Design:

image-20221023165346017

可以看出,Elaborated Design里面的電路是單純的對RTL源代碼的解析,到了Synthesisd Design,則可以看到Xilinx的具體的庫單元,比如LUT3、FDRE等,都是在Xilinx FPGA中真實存在的。

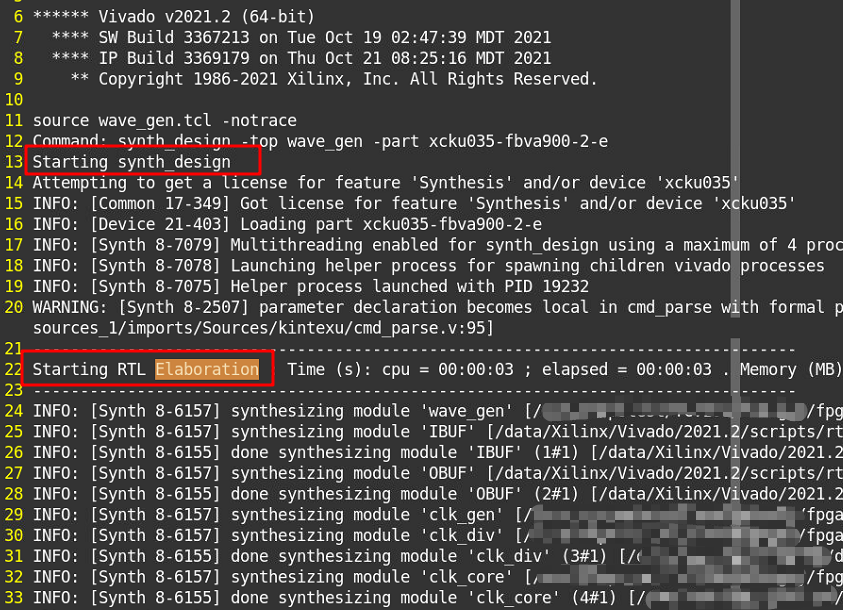

其實在綜合的log文件,看到Elaborate的存在,綜合的第一步就是先進行Elaborate:

審核編輯:湯梓紅

-

design

+關注

關注

0文章

161瀏覽量

46411 -

Synthesis

+關注

關注

0文章

8瀏覽量

8391 -

Vivado

+關注

關注

19文章

831瀏覽量

68303

原文標題:Vivado中的Elaborate是做什么的?

文章出處:【微信號:傅里葉的貓,微信公眾號:傅里葉的貓】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

請問IIO軟件是做什么的?

bootloader程序是用來做什么的?與startup程序有區別么?

stm32的這些時鐘都是做什么的

SOHO一族,SOHO一族是做什么的?

半導體公司是做什么的

什么是汽車芯片 汽車芯片是做什么的

ip地址是做什么的

簡述Vivado中的Elaborate的作用

Vivado中的Elaborate是做什么的?

Vivado中的Elaborate是做什么的?

評論