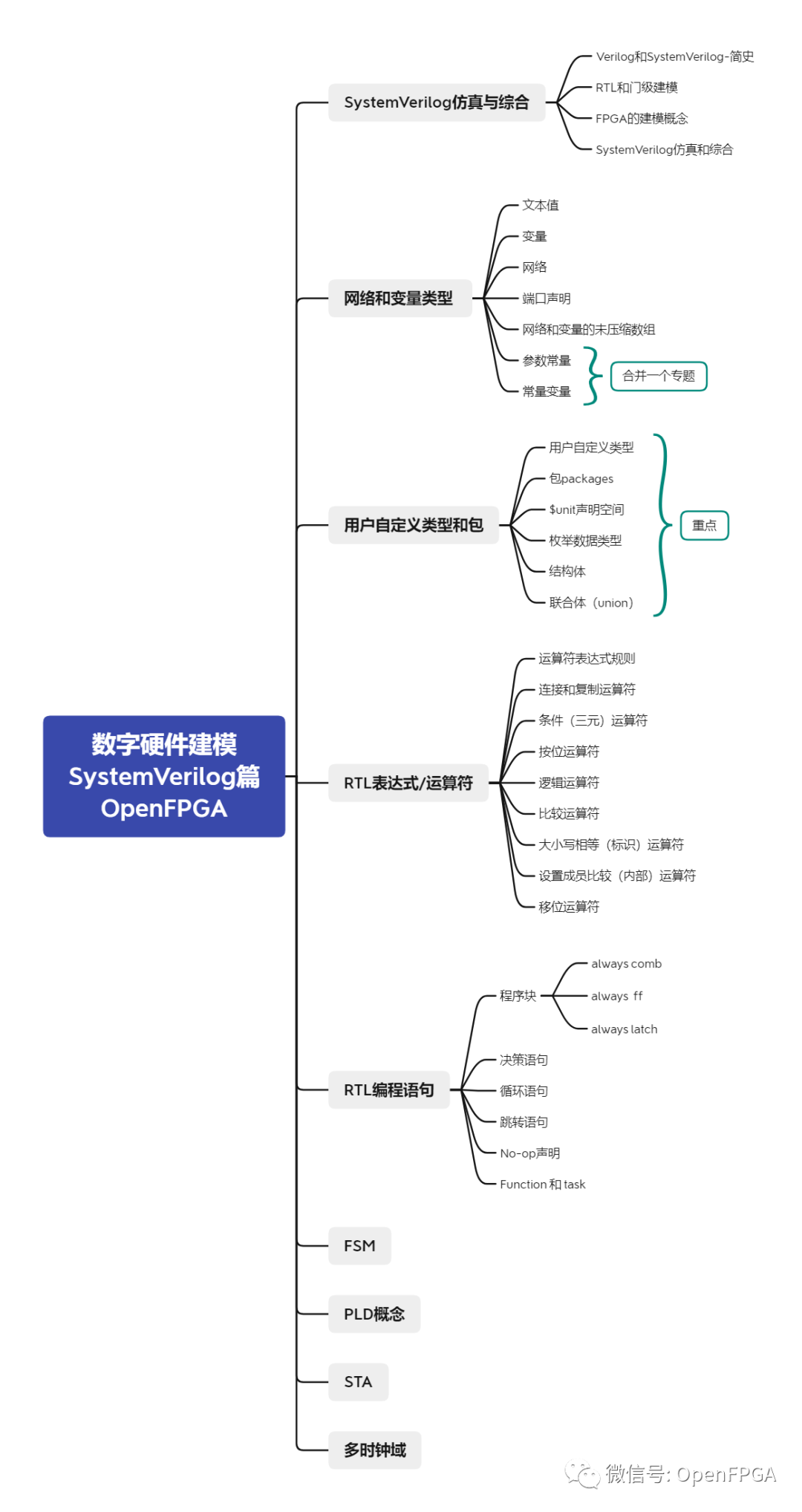

數(shù)字硬件建模SystemVerilog-決策語(yǔ)句-case語(yǔ)句

經(jīng)過(guò)幾周的更新,SV核心部分用戶(hù)自定義類(lèi)型和包內(nèi)容已更新完畢,接下來(lái)就是RTL表達(dá)式和運(yùn)算符。

馬上HDLBits-SystemVerilog版本也開(kāi)始準(zhǔn)備了,基本這一部分完成后就開(kāi)始更新~

決策語(yǔ)句(Decision statements)允許程序塊的執(zhí)行流程根據(jù)設(shè)計(jì)中信號(hào)的當(dāng)前值分支到特定語(yǔ)句。SystemVerilog有兩個(gè)主要的決策語(yǔ)句:if…else語(yǔ)句和case語(yǔ)句,使用關(guān)鍵字case、case…inside,casex和casez。

介紹

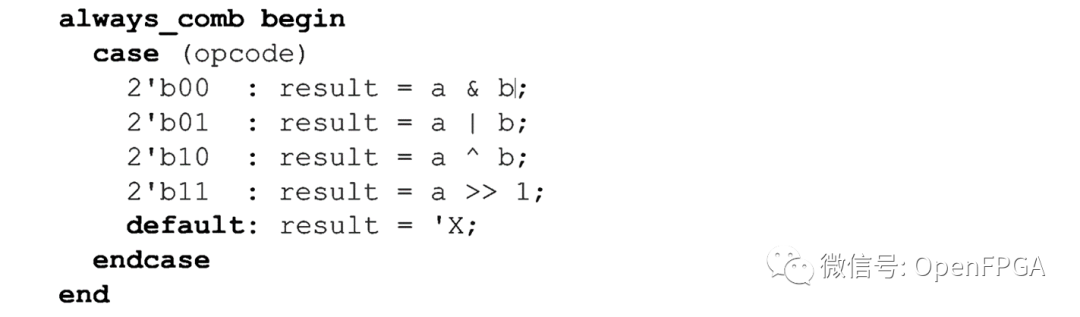

case語(yǔ)句提供了一種簡(jiǎn)潔的方式來(lái)表示一系列決策選擇。例如:

SystemVerilog case語(yǔ)句與C switch語(yǔ)句類(lèi)似,但有重要區(qū)別。SystemVerilog不能使用break語(yǔ)句(C使用break從switch語(yǔ)句的分支退出)。case語(yǔ)句在執(zhí)行分支后自動(dòng)退出(使用break退出case語(yǔ)句是非法的。),不能執(zhí)行break語(yǔ)句。

SystemVerilog有4種不同的case語(yǔ)句,關(guān)鍵字為case、case…inside casex和casez。這些不同case語(yǔ)句的一般語(yǔ)法和用法是相同的。這些區(qū)別將在本文后面介紹。

case、casex或casez關(guān)鍵字后面跟一個(gè)用括號(hào)括起來(lái)的case表達(dá)式。case表達(dá)式可以是網(wǎng)絡(luò)、變量、用戶(hù)定義類(lèi)型、參數(shù)常量、文字值或運(yùn)算結(jié)果。case表達(dá)式后面跟一個(gè)冒號(hào),如果case表達(dá)式與case項(xiàng)匹配,后續(xù)執(zhí)行是可以是一條語(yǔ)句或者begin-end包含的系列語(yǔ)句。

默認(rèn)case項(xiàng)。可以使用default關(guān)鍵字指定可選的默認(rèn)case項(xiàng)。如果case表達(dá)式與任何case項(xiàng)不匹配,將執(zhí)行默認(rèn)case項(xiàng)。在上面的例子中,case項(xiàng)覆蓋了2位操作碼的所有可能的2-state值。但是,如果操作碼是4-state類(lèi)型,則會(huì)有額外的X和Z值未被case項(xiàng)覆蓋。如果操作碼的任何位都是X或Z,則將執(zhí)行默認(rèn)case項(xiàng),在前面的示例中,該分支將把X值傳播到結(jié)果變量上。默認(rèn)情況下的case項(xiàng)不需要是最后一個(gè)case項(xiàng)。語(yǔ)法上,默認(rèn)case項(xiàng)可以是第一個(gè)case項(xiàng),或者在case項(xiàng)中的任何地方,代碼可讀性的最佳實(shí)踐編碼風(fēng)格是默認(rèn)case項(xiàng)為最后一個(gè)case項(xiàng)。

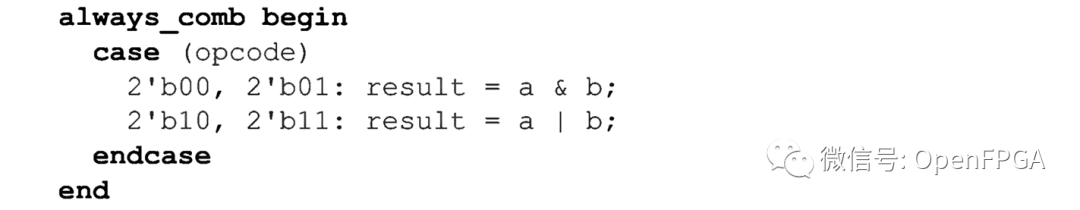

以逗號(hào)分隔的case項(xiàng)列表。case項(xiàng)可以是逗號(hào)分隔的列表,如以下代碼段所示:

如果操作碼的值為2’b00或2’b01,則執(zhí)行case語(yǔ)句的第一個(gè)分支,如果值為2’b10或2’b11,則執(zhí)行第二個(gè)分支。

case與case…inside

當(dāng)只使用case關(guān)鍵字時(shí), case表達(dá)式將與case項(xiàng)進(jìn)行比較,比較的運(yùn)算符為(===)。(===)運(yùn)算符將比較表達(dá)式的每一位,這將獲得4-state值的精確匹配。在下面的代碼段中,如果select的值為1’bz,則執(zhí)行第三個(gè)分支,如果select的值為1’bx,則執(zhí)行第四個(gè)分支(此示例不可綜合;綜合不允許比較X和Z值)

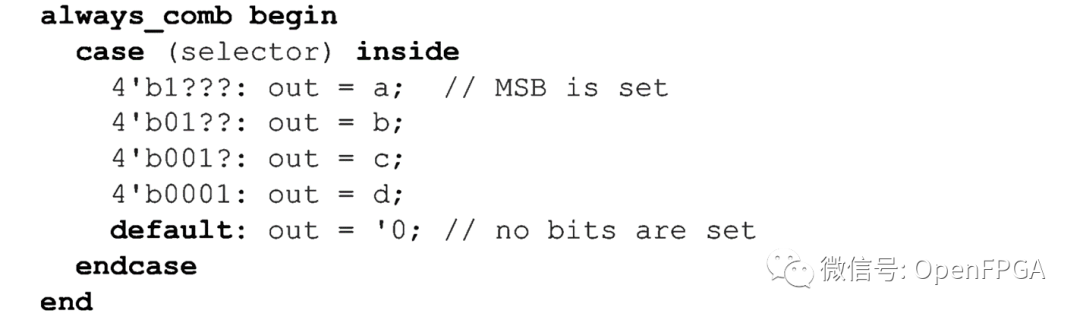

在case…inside語(yǔ)句中,使用(==?)通配符case相等運(yùn)算符的行為將case表達(dá)式與case項(xiàng)進(jìn)行比較(case使用===運(yùn)算符)。(==?)運(yùn)算符允許從比較中屏蔽某一位(即不進(jìn)行某一位的比較)。case項(xiàng)中的任何位被設(shè)置為x或z或?當(dāng)case表達(dá)式與case項(xiàng)進(jìn)行比較時(shí),該位位置將被忽略。

在以下示例中,如果selector的最高有效位置1,將執(zhí)行第一個(gè)分支,忽略case項(xiàng)的所有剩余位,如果selector的上兩位的值為01,將執(zhí)行第二個(gè)分支,并忽略剩余位,依此類(lèi)推:

過(guò)時(shí)的casex和casez語(yǔ)句

在SystemVerilog于2005年擴(kuò)展Verilog語(yǔ)言之前,最初的Verilog語(yǔ)言使用casex和casez關(guān)鍵字來(lái)屏蔽比較中的位。SystemVerilog將casex和casez替換為case…inside關(guān)鍵字。casex和casez語(yǔ)句屏蔽了設(shè)置為x、z或?的任何位。Casez語(yǔ)句僅屏蔽設(shè)置為z或?的位

| 最佳實(shí)踐指南6-2 |

|---|

| 用case…inside在決策語(yǔ)句中忽略case項(xiàng)中的特定位。不要使用過(guò)時(shí)的casex和casez語(yǔ)句。 |

SystemVerilog取代casex和casez的原因是,它們?cè)?a target="_blank">仿真時(shí)存在嚴(yán)重缺陷,在綜合邏輯門(mén)后,其行為與RTL仿真非常不同。簡(jiǎn)而言之,casex和casez不僅允許在case項(xiàng)中屏蔽位,還允許在case表達(dá)式中屏蔽位,這種雙重掩蔽可能會(huì)導(dǎo)致執(zhí)行一個(gè)非預(yù)期的分支,而這可能不是由綜合創(chuàng)建的門(mén)級(jí)電路實(shí)現(xiàn)時(shí)采用的同一個(gè)分支。casex和casez的缺點(diǎn)在本系列文章中沒(méi)有詳細(xì)討論,因?yàn)闆](méi)有必要使用這些過(guò)時(shí)的語(yǔ)句。

case項(xiàng)優(yōu)先級(jí)和綜合優(yōu)化

case項(xiàng)按其列出的順序進(jìn)行評(píng)估。因此,第一個(gè)case項(xiàng)的優(yōu)先級(jí)高于所有后續(xù)case項(xiàng)。在評(píng)估case語(yǔ)句時(shí),仿真將始終遵循此優(yōu)先級(jí)。

這種推斷出的優(yōu)先級(jí)編碼在ASIC或FPGA實(shí)現(xiàn)中通常是不可取的。與并行計(jì)算相比,優(yōu)先級(jí)編碼邏輯需要更多的邏輯門(mén)和更長(zhǎng)的傳播路徑。在將case語(yǔ)句轉(zhuǎn)換為邏輯門(mén)之前,綜合編譯器將分析case項(xiàng)的值。如果兩個(gè)case項(xiàng)不可能同時(shí)為真,則綜合編譯器將自動(dòng)優(yōu)化門(mén)級(jí)實(shí)現(xiàn),以并行評(píng)估case項(xiàng),而不是作為優(yōu)先級(jí)編碼功能。

然而,如果兩個(gè)或多個(gè)case項(xiàng)可能同時(shí)為真,那么綜合將實(shí)現(xiàn)case語(yǔ)句仿真中固有的優(yōu)先級(jí)編碼邏輯。通過(guò)實(shí)施優(yōu)先級(jí)編碼,綜合時(shí)將確保ASIC或FPGA的門(mén)級(jí)行為與RTL仿真行為匹配。

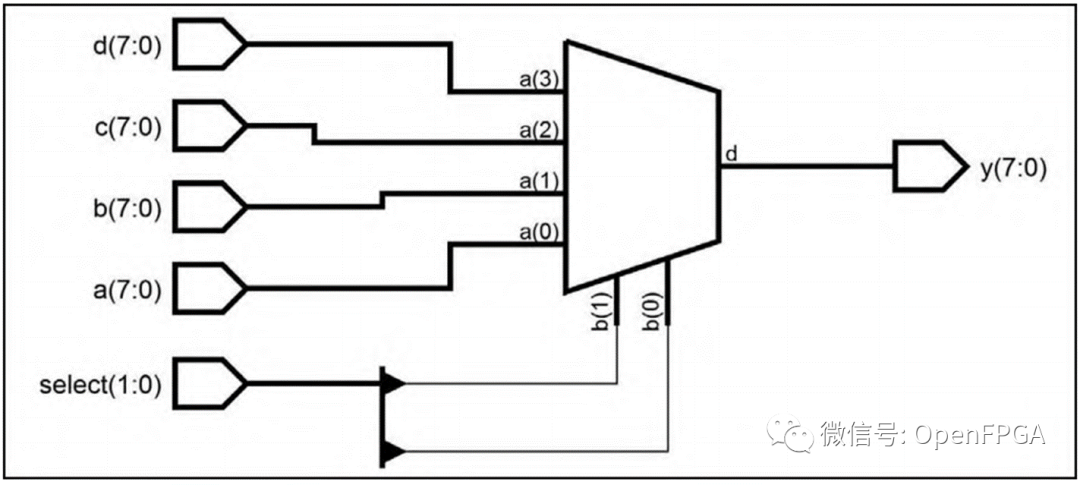

例6-5顯示了一個(gè)4選1的多路復(fù)用器。在本例中,四個(gè)case表達(dá)式具有唯一的、不重疊的值。綜合器將識(shí)別到兩個(gè)case表達(dá)式不可能同時(shí)為真,并自動(dòng)刪除case項(xiàng)的優(yōu)先級(jí)編碼。圖6-5顯示了綜合器如何實(shí)現(xiàn)case語(yǔ)句。

示例6-5:使用case語(yǔ)句對(duì)4選1多路復(fù)用器建模

//`begin_keywords"1800-2012"http://useSystemVerilog-2012keywords modulemux4to1 #(parameterN=8) ( inputlogic[N-1:0]a,b,c,d, inputlogic[1:0]select, outputlogic[N-1:0]y ); always_combbegin case(select) 2'b00:y=a; 2'b01:y=b; 2'b10:y=c; 2'b11:y=d; endcase end endmodule:mux4to1 //`end_keywords

圖6-5:示例6-5的綜合結(jié)果:綜合4選1多路復(fù)用器的case語(yǔ)句

圖6-5:示例6-5的綜合結(jié)果:綜合4選1多路復(fù)用器的case語(yǔ)句

例6-5中的case項(xiàng)是互斥的,這意味著其中兩個(gè)case項(xiàng)不可能同時(shí)成立。因此,綜合編譯器刪除了case語(yǔ)句的優(yōu)先級(jí)編碼行為,并以多路復(fù)用器的形式對(duì)case項(xiàng)實(shí)現(xiàn)了更高效的并行計(jì)算,

綜合編譯器自動(dòng)刪除優(yōu)先級(jí)邏輯,只要綜合可以確定所有case項(xiàng)都是互斥的(不會(huì)有兩個(gè)或多個(gè)case項(xiàng)同時(shí)計(jì)算結(jié)果為true)。如果綜合編譯器不能確定case項(xiàng)是互斥的,那么它將保留case項(xiàng)的優(yōu)先級(jí)方式。

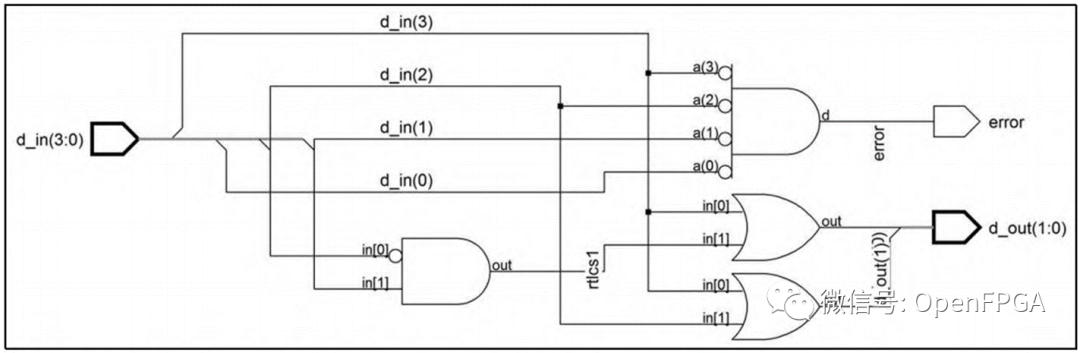

示例6-6類(lèi)似于示例6-3中所示的4選2優(yōu)先級(jí)編碼器,但這次使用case…inside,只允許檢查4位d_in值中的特定位。由于忽略了其他位,因此可能存在不止一個(gè)位case項(xiàng)同時(shí)為true,仿真將執(zhí)行第一個(gè)匹配分支,綜合編譯器將通過(guò)“保留case語(yǔ)句固有的優(yōu)先級(jí)編碼”來(lái)匹配該行為。

示例6-6:使用內(nèi)部的case項(xiàng)來(lái)仿真優(yōu)先級(jí)編碼器

//`begin_keywords"1800-2012"http://useSystemVerilog-2012keywords modulepriority_4to2_encoder( inputlogic[3:0]d_in, outputlogic[1:0]d_out, outputlogicerror ); timeunit1ns;timeprecision1ns; always_combbegin error='0; case(d_in)inside 4'b1???:d_out=2'h3;//bit3isset 4'b01??:d_out=2'h2;//bit2isset 4'b001?:d_out=2'h1;//bit1isset 4'b0001:d_out=2'h0;//bit0isset 4'b0000:begin//nobitsset d_out=2'b0; error='1; end endcase end endmodule:priority_4to2_encoder //`end_keywords

圖6-6:示例6-6的綜合結(jié)果:case…inside作為優(yōu)先編碼器

圖6-6:示例6-6的綜合結(jié)果:case…inside作為優(yōu)先編碼器

優(yōu)先級(jí)邏輯的效果可以在一系列門(mén)電路中看到,d_in的不同位通過(guò)這些門(mén)傳播。當(dāng)使用一系列if-else-if語(yǔ)句時(shí),綜合編譯器綜合出來(lái)的電路非常相似,如上一章節(jié)的例程。

唯一和優(yōu)先決策修飾符

SystemVerilog為case和if-else決策語(yǔ)句提供三個(gè)修飾符:unique、unique0和priority。后面章節(jié)將詳細(xì)討論RTL模型中使用的修飾符。

簡(jiǎn)而言之,unique、unigue0和priority修飾符有兩個(gè)功能:

它們影響綜合編譯器在門(mén)級(jí)電路實(shí)現(xiàn)case語(yǔ)句的方式。

他們?cè)诜抡嬷袑?huì)報(bào)告警告消息,幫助驗(yàn)證綜合效果是否會(huì)按預(yù)期工作。

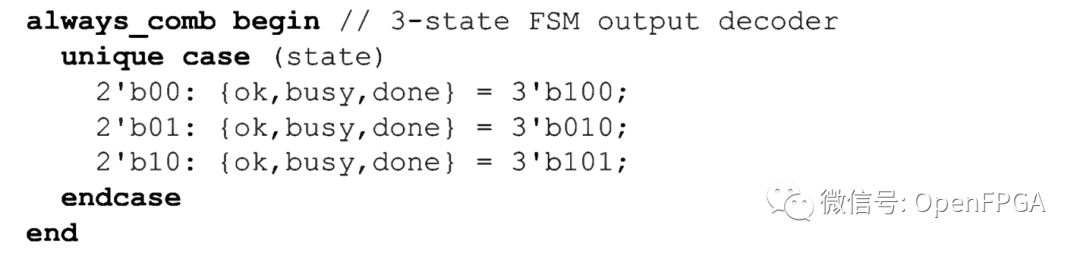

這些決策修飾符的一個(gè)示例用法是:

對(duì)于綜合,本例中的unique修飾符通知綜合編譯器case語(yǔ)句可以被認(rèn)為是完整的,即使2位狀態(tài)變量的四個(gè)可能值中只有三個(gè)被解碼。同時(shí)還通知綜合編譯器,對(duì)case項(xiàng)并行評(píng)估是可以的。

對(duì)于仿真,unique關(guān)鍵字在仿真中啟用兩個(gè)檢查例程,如果對(duì)case語(yǔ)句進(jìn)行了評(píng)估,并且state的值與任何case項(xiàng)都不匹配,則將生成違規(guī)報(bào)告。此檢查有助于驗(yàn)證將case語(yǔ)句視為完整的綜合是否安全。如果state的值同時(shí)與多個(gè)案例項(xiàng)匹配,則還會(huì)生成違規(guī)報(bào)告。該檢查有助于驗(yàn)證對(duì)case項(xiàng)并行評(píng)估是安全的,而不是按照case項(xiàng)列出的順序,

-

硬件

+關(guān)注

關(guān)注

11文章

3466瀏覽量

67284 -

HDL

+關(guān)注

關(guān)注

8文章

330瀏覽量

47885 -

編碼

+關(guān)注

關(guān)注

6文章

967瀏覽量

55581 -

RTL

+關(guān)注

關(guān)注

1文章

388瀏覽量

60779

原文標(biāo)題:SystemVerilog-決策語(yǔ)句-case語(yǔ)句

文章出處:【微信號(hào):Open_FPGA,微信公眾號(hào):OpenFPGA】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

Verilog中的always塊內(nèi)的語(yǔ)句執(zhí)行的速度?

mfc程序執(zhí)行流程小結(jié),MFC程序的執(zhí)行順序

select語(yǔ)句和update語(yǔ)句分別是怎么執(zhí)行的

Verilog的兩種塊語(yǔ)句解析

Verilog的塊語(yǔ)句

Verilog的塊語(yǔ)句fork...join 和 begin...end

systemverilog的決策語(yǔ)句if…else語(yǔ)句介紹

SystemVerilog中的always語(yǔ)句塊

SCL用GOTO語(yǔ)句執(zhí)行程序跳轉(zhuǎn)

WHILE語(yǔ)句如何執(zhí)行

決策語(yǔ)句允許程序塊的執(zhí)行流程

決策語(yǔ)句允許程序塊的執(zhí)行流程

評(píng)論