大家都知道理做PCB板就是把設(shè)計(jì)好的原理圖變成一塊實(shí)實(shí)在在的PCB電路板,請(qǐng)別小看這一過(guò)程,有很多原理上行得通的東西在工程中卻難以實(shí)現(xiàn),或是別人能實(shí)現(xiàn)的東西另一些人卻實(shí)現(xiàn)不了,因此說(shuō)做一塊PCB板不難,但要做好一塊PCB板卻不是一件容易的事情。

微電子領(lǐng)域的兩大難點(diǎn)在于高頻信號(hào)和微弱信號(hào)的處理,在這方面PCB制作水平就顯得尤其重要,同樣的原理設(shè)計(jì),同樣的元器件,不同的人制作出來(lái)的PCB就具有不同的結(jié)果,那么如何才能做出一塊好的PCB板呢?

根據(jù)我們以往的經(jīng)驗(yàn),想就以下幾方面談?wù)勛约旱目捶ǎ?/p>

一要明確設(shè)計(jì)目標(biāo)

接受到一個(gè)設(shè)計(jì)任務(wù),首先要明確其設(shè)計(jì)目標(biāo),是普通的PCB板、高頻PCB板、小信號(hào)處理PCB板還是既有高頻率又有小信號(hào)處理的PCB板,如果是普通的PCB板,只要做到布局布線合理整齊,機(jī)械尺寸準(zhǔn)確無(wú)誤即可,如有中負(fù)載線和長(zhǎng)線,就要采用一定的手段進(jìn)行處理,減輕負(fù)載,長(zhǎng)線要加強(qiáng)驅(qū)動(dòng),重點(diǎn)是防止長(zhǎng)線反射。

當(dāng)板上有超過(guò)40MHz的信號(hào)線時(shí),就要對(duì)這些信號(hào)線進(jìn)行特殊的考慮,比如線間串?dāng)_等問(wèn)題。如果頻率更高一些,對(duì)布線的長(zhǎng)度就有更嚴(yán)格的限制,根據(jù)分布參數(shù)的網(wǎng)絡(luò)理論,高速電路與其連線間的相互作用是決定性因素,在系統(tǒng)設(shè)計(jì)時(shí)不能忽略。隨著門(mén)傳輸速度的提高,在信號(hào)線上的反對(duì)將會(huì)相應(yīng)增加,相鄰信號(hào)線間的串?dāng)_將成正比地增加,通常高速電路的功耗和熱耗散也都很大,在做高速PCB時(shí)應(yīng)引起足夠的重視。

當(dāng)板上有毫伏級(jí)甚至微伏級(jí)的微弱信號(hào)時(shí),對(duì)這些信號(hào)線就需要特別的關(guān)照,小信號(hào)由于太微弱,非常容易受到其它強(qiáng)信號(hào)的干擾,屏蔽措施常常是必要的,否則將大大降低信噪比。以致于有用信號(hào)被噪聲淹沒(méi),不能有效地提取出來(lái)。

對(duì)板子的調(diào)測(cè)也要在設(shè)計(jì)階段加以考慮,測(cè)試點(diǎn)的物理位置,測(cè)試點(diǎn)的隔離等因素不可忽略,因?yàn)橛行┬⌒盘?hào)和高頻信號(hào)是不能直接把探頭加上去進(jìn)行測(cè)量的。

此外還要考慮其他一些相關(guān)因素,如板子層數(shù),采用元器件的封裝外形,板子的機(jī)械強(qiáng)度等。在做PCB板子前,要做出對(duì)該設(shè)計(jì)的設(shè)計(jì)目標(biāo)心中有數(shù)。

二了解元器件的功能對(duì)布局布線的要求

我們知道,有些特殊元器件在布局布線時(shí)有特殊的要求,比如LOTI和APH所用的模擬信號(hào)放大器,模擬信號(hào)放大器對(duì)電源要求要平穩(wěn)、紋波小。模擬小信號(hào)部分要盡量遠(yuǎn)離功率器件。在OTI板上,小信號(hào)放大部分還專門(mén)加有屏蔽罩,把雜散的電磁干擾給屏蔽掉。

NTOI板上用的GLINK芯片采用的是ECL工藝,功耗大發(fā)熱厲害,對(duì)散熱問(wèn)題必須在布局時(shí)就必須進(jìn)行特殊考慮,若采用自然散熱,就要把GLINK芯片放在空氣流通比較順暢的地方,而且散出來(lái)的熱量還不能對(duì)其它芯片構(gòu)成大的影響。如果板子上裝有喇叭或其他大功率的器件,有可能對(duì)電源造成嚴(yán)重的污染這一點(diǎn)也應(yīng)引起足夠的重視。

三元器件布局的考慮

元器件的布局首先要考慮的一個(gè)因素就是電性能,把連線關(guān)系密切的元器件盡量放在一起,尤其對(duì)一些高速線,布局時(shí)就要使它盡可能地短,功率信號(hào)和小信號(hào)器件要分開(kāi)。在滿足電路性能的前提下,還要考慮元器件擺放整齊、美觀,便于測(cè)試,板子的機(jī)械尺寸,插座的位置等也需認(rèn)真考慮。

高速系統(tǒng)中的接地和互連線上的傳輸延遲時(shí)間也是在系統(tǒng)設(shè)計(jì)時(shí)首先要考慮的因素。信號(hào)線上的傳輸時(shí)間對(duì)總的系統(tǒng)速度影響很大,特別是對(duì)高速的ECL電路,雖然集成電路塊本身速度很高,但由于在底板上用普通的互連線(每30cm線長(zhǎng)約有2ns的延遲量)帶來(lái)延遲時(shí)間的增加,可使系統(tǒng)速度大為降低。

象移位寄存器,同步計(jì)數(shù)器這種同步工作部件最好放在同一塊插件板上,因?yàn)榈讲煌寮迳系?a href="http://m.xsypw.cn/tags/時(shí)鐘/" target="_blank">時(shí)鐘信號(hào)的傳輸延遲時(shí)間不相等,可能使移位寄存器產(chǎn)主錯(cuò)誤,若不能放在一塊板上,則在同步是關(guān)鍵的地方,從公共時(shí)鐘源連到各插件板的時(shí)鐘線的長(zhǎng)度必須相等。

四對(duì)布線的考慮

隨著OTNI和星形光纖網(wǎng)的設(shè)計(jì)完成,以后會(huì)有更多的100MHz以上的具有高速信號(hào)線的板子需要設(shè)計(jì),這里將介紹高速線的一些基本概念。

傳輸線

印制電路板上的任何一條“長(zhǎng)”的信號(hào)通路都可以視為一種傳輸線。如果該線的傳輸延遲時(shí)間比信號(hào)上升時(shí)間短得多,那么信號(hào)上升期間所產(chǎn)主的反射都將被淹沒(méi)。不再呈現(xiàn)過(guò)沖、反沖和振鈴,對(duì)現(xiàn)時(shí)大多數(shù)的MOS電路來(lái)說(shuō),由于上升時(shí)間對(duì)線傳輸延遲時(shí)間之比大得多,所以走線可長(zhǎng)以米計(jì)而無(wú)信號(hào)失真。而對(duì)于速度較快的邏輯電路,特別是超高速ECL。

集成電路來(lái)說(shuō),由于邊沿速度的增快,若無(wú)其它措施,走線的長(zhǎng)度必須大大縮短,以保持信號(hào)的完整性。

有兩種方法能使高速電路在相對(duì)長(zhǎng)的線上工作而無(wú)嚴(yán)重的波形失真,TTL對(duì)快速下降邊沿采用肖特基二極管箝位方法,使過(guò)沖量被箝制在比地電位低一個(gè)二極管壓降的電平上,這就減少了后面的反沖幅度,較慢的上升邊緣允許有過(guò)沖,但它被在電平“H”狀態(tài)下電路的相對(duì)高的輸出阻抗(50~80Ω)所衰減。此外,由于電平“H”狀態(tài)的抗擾度較大,使反沖問(wèn)題并不十分突出,對(duì)HCT系列的器件,若采用肖特基二極管箝位和串聯(lián)電阻端接方法相結(jié)合,其改善的效果將會(huì)更加明顯。

當(dāng)沿信號(hào)線有扇出時(shí),在較高的位速率和較快的邊沿速率下,上述介紹的TTL整形方法顯得有些不足。因?yàn)榫€中存在著反射波,它們?cè)诟呶凰俾氏聦②呌诤铣桑瑥亩鹦盘?hào)嚴(yán)重失真和抗干擾能力降低。因此,為了解決反射問(wèn)題,在ECL系統(tǒng)中通常使用另外一種方法:線阻抗匹配法。用這種方法能使反射受到控制,信號(hào)的完整性得到保證。

嚴(yán)格他說(shuō),對(duì)于有較慢邊沿速度的常規(guī)TTL和CMOS器件來(lái)說(shuō),傳輸線并不是十分需要的。對(duì)有較快邊沿速度的高速ECL器件,傳輸線也不總是需要的。但是當(dāng)使用傳輸線時(shí),它們具有能預(yù)測(cè)連線時(shí)延和通過(guò)阻抗匹配來(lái)控制反射和振蕩的優(yōu)點(diǎn)。

1. 決定是否采用傳輸線的基本因素有以下五個(gè)。它們是:

(1)系統(tǒng)信號(hào)的沿速率;

(2)連線距離 ;

(3)容性負(fù)載(扇出的多少);

(4)電阻性負(fù)載(線的端接方式);

(5)允許的反沖和過(guò)沖百分比(交流抗擾度的降低程度)。

2.傳輸線的幾種類型

(1) 同軸電纜和雙絞線:它們經(jīng)常用在系統(tǒng)與系統(tǒng)之間的連接。同軸電纜的特性阻抗通常有50Ω和75Ω,雙絞線通常為110Ω。

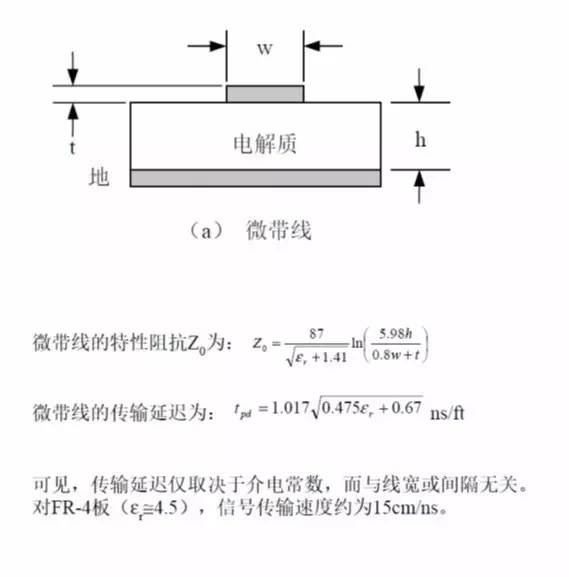

(2)印制板上的微帶線

微帶線是一根帶狀導(dǎo)(信號(hào)線),與地平面之間用一種電介質(zhì)隔離開(kāi)。如果線的厚度、寬度以及與地平面之間的距離是可控制的,則它的特性阻抗也是可以控制的。微帶線的特性阻抗Z0為:

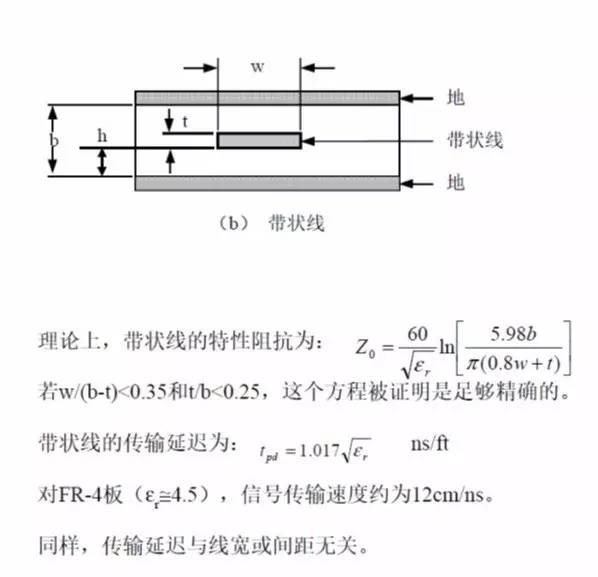

(3)印制板中的帶狀線

帶狀線是一條置于兩層導(dǎo)電平面之間的電介質(zhì)中間的銅帶線。如果線的厚度和寬度、介質(zhì)的介電常數(shù)以及兩層導(dǎo)電平面間的距離是可控的,那么線的特性阻抗也是可控的,帶狀線的特性阻抗為:

3.端接傳輸線

在一條線的接收端用一個(gè)與線特性阻抗相等的電阻端接,則稱該傳輸線為并聯(lián)端接線。它主要是為了獲得最好的電性能,包括驅(qū)動(dòng)分布負(fù)載而采用的。

有時(shí)為了節(jié)省電源消耗,對(duì)端接的電阻上再串接一個(gè)104電容形成交流端接電路,它能有效地降低直流損耗。

在驅(qū)動(dòng)器和傳輸線之間串接一個(gè)電阻,而線的終端不再接端接電阻,這種端接方法稱之為串聯(lián)端接。較長(zhǎng)線上的過(guò)沖和振鈴可用串聯(lián)阻尼或串聯(lián)端接技術(shù)來(lái)控制.串聯(lián)阻尼是利用一個(gè)與驅(qū)動(dòng)門(mén)輸出端串聯(lián)的小電阻(一般為10~75Ω)來(lái)實(shí)現(xiàn)的.這種阻尼方法適合與特性阻抗來(lái)受控制的線相聯(lián)用(如底板布線,無(wú)地平面的電路板和大多數(shù)繞接線等。

串聯(lián)端接時(shí)串聯(lián)電阻的值與電路(驅(qū)動(dòng)門(mén))輸出阻抗之和等于傳輸線的特性阻抗.串聯(lián)聯(lián)端接線存在著只能在終端使用集總負(fù)載和傳輸延遲時(shí)間較長(zhǎng)的缺點(diǎn).但是,這可以通過(guò)使用多余串聯(lián)端接傳輸線的方法加以克服。

4.非端接傳輸線

如果線延遲時(shí)間比信號(hào)上升時(shí)間短得多,可以在不用串聯(lián)端接或并聯(lián)端接的情況下使用傳輸線,如果一根非端接線的雙程延遲(信號(hào)在傳輸線上往返一次的時(shí)間)比脈沖信號(hào)的上升時(shí)間短,那么由于非端接所引起的反沖大約是邏輯擺幅的15%。最大開(kāi)路線長(zhǎng)度近似為:

Lmax<tr/2tpd

式中:tr為上升時(shí)間

tpd為單位線長(zhǎng)的傳輸延遲時(shí)間

5.幾種端接方式的比較

并聯(lián)端接線和串聯(lián)端接線都各有優(yōu)點(diǎn),究竟用哪一種,還是兩種都用,這要看設(shè)計(jì)者的愛(ài)好和系統(tǒng)的要求而定。并聯(lián)端接線的主要優(yōu)點(diǎn)是系統(tǒng)速度快和信號(hào)在線上傳輸完整無(wú)失真。長(zhǎng)線上的負(fù)載既不會(huì)影響驅(qū)動(dòng)長(zhǎng)線的驅(qū)動(dòng)門(mén)的傳輸延遲時(shí)間,又不會(huì)影響它的信號(hào)邊沿速度,但將使信號(hào)沿該長(zhǎng)線的傳輸延遲時(shí)間增大。在驅(qū)動(dòng)大扇出時(shí),負(fù)載可經(jīng)分支短線沿線分布,而不象串聯(lián)端接中那樣必須把負(fù)載集總在線的終端。

串聯(lián)端接方法使電路有驅(qū)動(dòng)幾條平行負(fù)載線的能力,串聯(lián)端接線由于容性負(fù)載所引起的延遲時(shí)間增量約比相應(yīng)并聯(lián)端接線的大一倍,而短線則因容性負(fù)載使邊沿速度放慢和驅(qū)動(dòng)門(mén)延遲時(shí)間增大,但是,串聯(lián)端接線的串?dāng)_比并聯(lián)端接線的要小,其主要原因是沿串聯(lián)端接線傳送的信號(hào)幅度僅僅是二分之一的邏輯擺幅,因而開(kāi)關(guān)電流也只有并聯(lián)端接的開(kāi)關(guān)電流的一半,信號(hào)能量小串?dāng)_也就小。

做PCB時(shí)是選用雙面板還是多層板,要看最高工作頻率和電路系統(tǒng)的復(fù)雜程度以及對(duì)組裝密度的要求來(lái)決定。在時(shí)鐘頻率超過(guò)200MHZ時(shí)最好選用多層板。如果工作頻率超過(guò)350MHz,最好選用以聚四氟乙烯作為介質(zhì)層的印制電路板,因?yàn)樗母哳l衰耗要小些,寄生電容要小些,傳輸速度要快些,還由于Z0較大而省功耗,對(duì)印制電路板的走線有如下原則要求:

(1)所有平行信號(hào)線之間要盡量留有較大的間隔,以減少串?dāng)_。如果有兩條相距較近的信號(hào)線,最好在兩線之間走一條接地線,這樣可以起到屏蔽作用。

(2) 設(shè)計(jì)信號(hào)傳輸線時(shí)要避免急拐彎,以防傳輸線特性阻抗的突變而產(chǎn)生反射,要盡量設(shè)計(jì)成具有一定尺寸的均勻的圓弧線。

(3)印制線的寬度可根據(jù)上述微帶線和帶狀線的特性阻抗計(jì)算公式計(jì)算,印制電路板上的微帶線的特性阻抗一般在50~120Ω之間。要想得到大的特性阻抗,線寬必須做得很窄,但很細(xì)的線條又不容易制作。

綜合各種因素考慮,一般選擇68Ω左右的阻抗值比較合適,因?yàn)檫x擇68Ω的特性阻抗,可以在延遲時(shí)間和功耗之間達(dá)到最佳平衡。一條50Ω的傳輸線將消耗更多的功率;較大的阻抗固然可以使消耗功率減少,但會(huì)使傳輸延遲時(shí)間憎大。

由于負(fù)線電容會(huì)造成傳輸延遲時(shí)間的增大和特性阻抗的降低。但特性阻抗很低的線段單位長(zhǎng)度的本征電容比較大,所以傳輸延遲時(shí)間及特性阻抗受負(fù)載電容的影響較小。具有適當(dāng)端接的傳輸線的一個(gè)重要特征是,分枝短線對(duì)線延遲時(shí)間應(yīng)沒(méi)有什么影響。當(dāng)Z0為50Ω時(shí)。分枝短線的長(zhǎng)度必須限制在2.5cm以內(nèi).以免出現(xiàn)很大的振鈴。

(4)對(duì)于雙面板(或六層板中走四層線)。電路板兩面的線要互相垂直,以防止互相感應(yīng)產(chǎn)主串?dāng)_。

(5)印制板上若裝有大電流器件,如繼電器、指示燈、喇叭等,它們的地線最好要分開(kāi)單獨(dú)走,以減少地線上的噪聲,這些大電流器件的地線應(yīng)連到插件板和背板上的一個(gè)獨(dú)立的地總線上去,而且這些獨(dú)立的地線還應(yīng)該與整個(gè)系統(tǒng)的接地點(diǎn)相連接。

(6)如果板上有小信號(hào)放大器,則放大前的弱信號(hào)線要遠(yuǎn)離強(qiáng)信號(hào)線,而且走線要盡可能地短,如有可能還要用地線對(duì)其進(jìn)行屏蔽。

審核編輯 :李倩

-

pcb

+關(guān)注

關(guān)注

4365文章

23477瀏覽量

409112 -

寄存器

+關(guān)注

關(guān)注

31文章

5433瀏覽量

124240 -

信號(hào)處理

+關(guān)注

關(guān)注

48文章

1055瀏覽量

104054

原文標(biāo)題:從原理圖到實(shí)實(shí)在在PCB電路板,這一過(guò)程其實(shí)也不容易!

文章出處:【微信號(hào):電子設(shè)計(jì)聯(lián)盟,微信公眾號(hào):電子設(shè)計(jì)聯(lián)盟】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

阿里稱要把AI融入每一塊業(yè)務(wù) 蔡崇信稱電商和云+AI是方向

兩塊SRAM分別位于不同的基地址,有什么方法可以使這兩塊區(qū)域SRAM當(dāng)成一塊使用?

實(shí)驗(yàn)過(guò)程中DLP Discovery 4100開(kāi)發(fā)板的電源撥碼開(kāi)關(guān)sw4連帶焊盤(pán)一塊脫落,怎么解決?

使用兩塊TSW3003EVM電路板連接到同一臺(tái)PC時(shí),無(wú)法對(duì)另一塊進(jìn)行編程如何解決?

怎么設(shè)計(jì)ADS828E的高速PCB板,要注意哪些問(wèn)題?

揭秘PCB電路板抄板全過(guò)程:從元件記錄到完美復(fù)制

陶瓷PCB的表面處理

如何才能做出一塊好的PCB板呢?

如何才能做出一塊好的PCB板呢?

評(píng)論