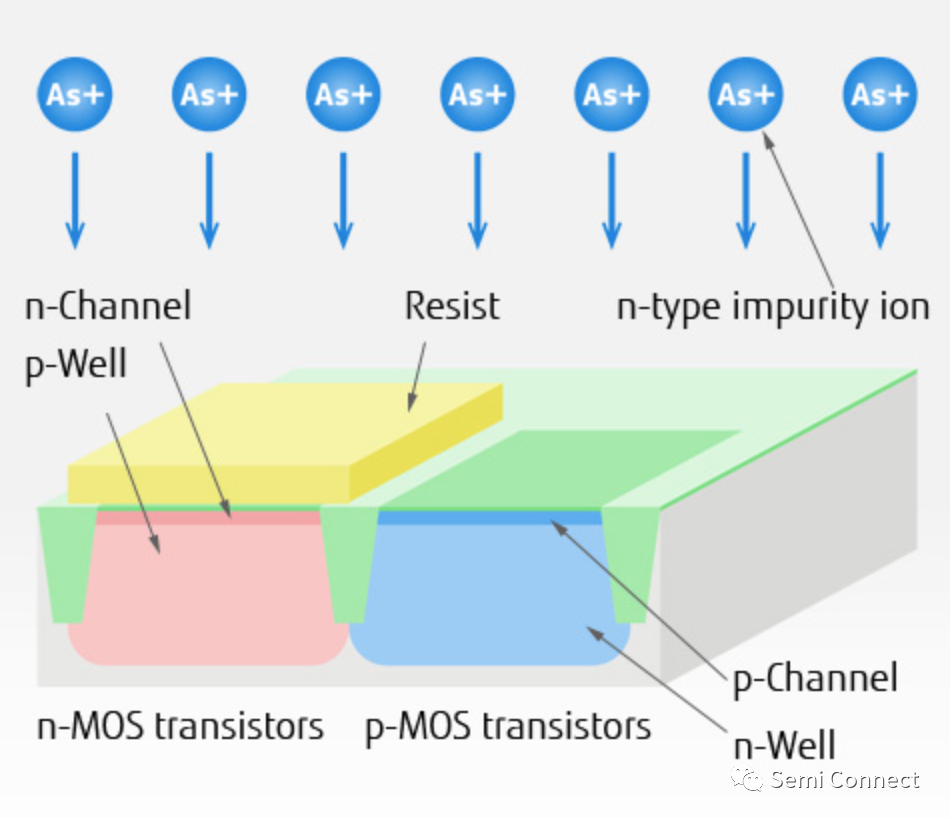

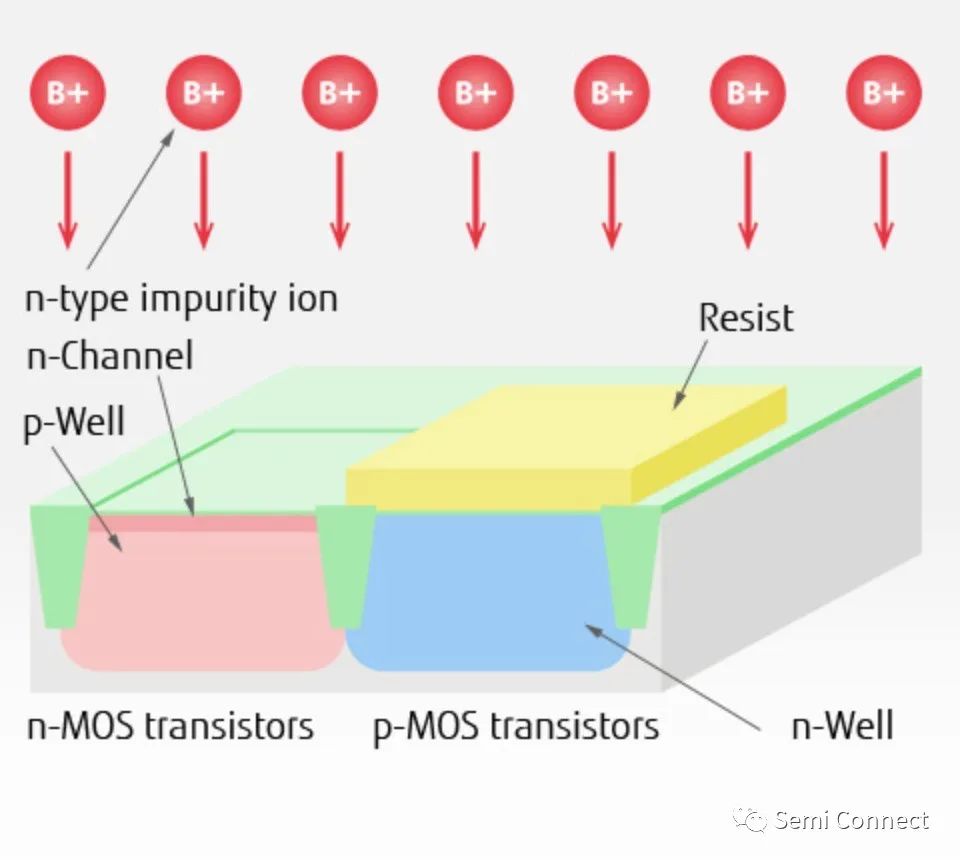

調節 MOSFET 閾值電壓的最直接的工藝方法就是對 n-MOSFET 和 p-MOSFET的溝道區分別進行離子注入,從而使其閾值電壓達到預期值。另外,在溝道區為防止源漏穿通而引入的高能量離子注入,以及在柵電極形成后為減少短溝道效應而從源漏端大角度地側面離子注入,也會對 MOSFET 的閾值電壓有直接影響。溝道工藝在一定程度上還與雙阱工藝相關。

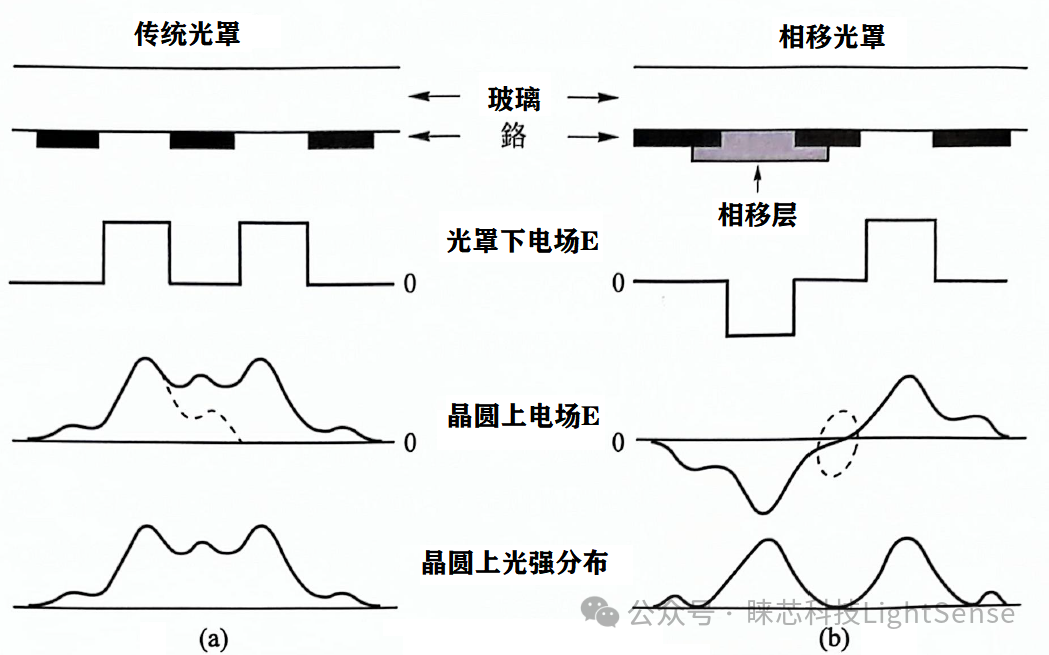

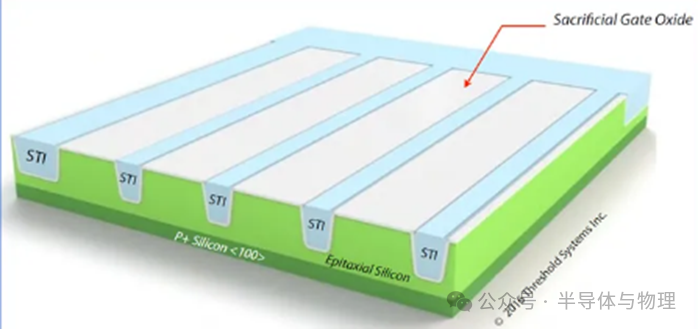

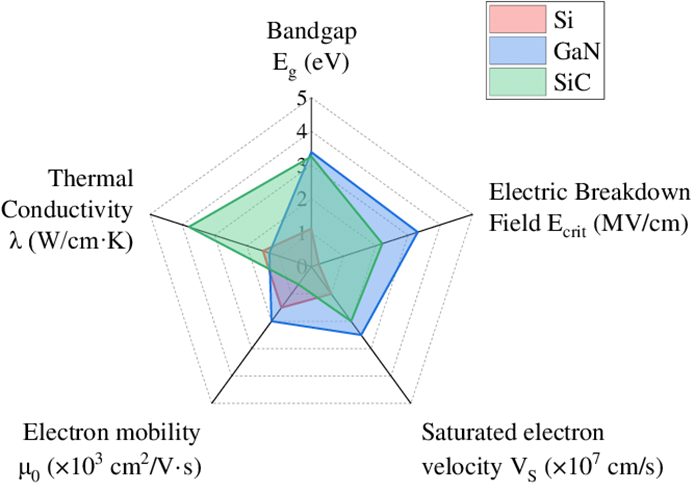

溝道工藝是集成電路的核心工藝之一,它確定了場效應晶體管的基本特性,如閾值電壓、短溝道特性、噪聲特性、穿通(Punch-througb)特性等,其目的是使場效應晶體管具有穩定的符合要求的電學參數,如閾值電壓等。隨著器件尺寸的不斷縮小,出現了很多會影響閾值電壓的因素,如柵氧厚度的波動,多晶硅柵長和寬度的變化,多晶硅柵的耗盡效應和摻雜的波動,側墻的寬度,以及源漏注入LDD 等。例如,為了改善短溝道效應,側墻和輕摻雜漏工藝在20 世紀80 年代被引入。為了控制器件的穿通,在溝道區之間注入的基礎上,也使用了大角度回轉的從柵的側面注入。接下來先后引入了氮氧化硅柵介質和高K柵介質層,以解決柵氧化層變薄引起的器件特性惡化問題。所以在一定程度上說,溝道工藝己經不再局限于溝道區的離子注入。例如,對于 40nm 以下的工藝,通過源漏鍺硅(SiGe)外延對溝道區施加應力,可以提高 MOSFET 的開關速度。

由于 SoC 的應用越來越廣泛,在一個集成電路中會有多種特性的場效應晶體管存在,它們工作在不同的電源電壓和閾值電壓條件下,同時器件尺寸(長寬)持續縮小,電源電壓持續下降也導致閾值電壓隨之下降,這就使得器件的漏電和噪聲問題變得越來越難以解決,隨機因素顯著增加,因此給溝道工藝帶來了嚴峻的挑戰。

審核編輯 :李倩

-

集成電路

+關注

關注

5425文章

12076瀏覽量

368593 -

MOSFET

+關注

關注

150文章

8625瀏覽量

220611 -

電源電壓

+關注

關注

3文章

1151瀏覽量

24768

原文標題:溝道工藝(Channel Process)

文章出處:【微信號:Semi Connect,微信公眾號:Semi Connect】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

Stellar P6 SARADC模塊,Internal channel/Test channel/External channel的都有那些區別呢?

FinFet Process Flow-源漏極是怎樣形成的

光刻工藝中分辨率增強技術詳解

溝道工藝(Channel Process)

溝道工藝(Channel Process)

評論