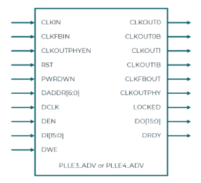

ASIC設(shè)計(jì)服務(wù)暨IP研發(fā)銷售廠商智原科技(Faraday Technology Corporation,TWSE:3035)今日宣布其FPGA-Go-ASIC服務(wù)已成功交付多項(xiàng)設(shè)計(jì)案,工藝從5納米至22納米,涵蓋工業(yè)、醫(yī)療、智能電網(wǎng)、樂(lè)器、與5G無(wú)線等應(yīng)用領(lǐng)域,芯片成品顯著降低原有FPGA設(shè)計(jì)的BOM成本與功耗,提升市場(chǎng)競(jìng)爭(zhēng)力;其中部分設(shè)計(jì)案依客戶需求,與原來(lái)的FPGA芯片針腳完全兼容 (pin-to-pin compatible),用以直接取代芯片運(yùn)行。

智原累積數(shù)十年SoC與IP經(jīng)驗(yàn),熟悉上億門級(jí)(gate-count)的高復(fù)雜度SoC設(shè)計(jì)與制程特性,搭配自有IP及Arm或RISC-V處理器,可快速整合并降低成本,有效率地將FPGA設(shè)計(jì)轉(zhuǎn)換為ASIC芯片。由于ASIC的電路設(shè)計(jì)效率較高,采用較成熟制程即可逹到系統(tǒng)所需的效能,例如將FinFET制程的FPGA轉(zhuǎn)換至40納米或28納米;同時(shí),智原IP客制化的能力可滿足不同IP配置(configuration)的需求,將多個(gè)FPGA設(shè)計(jì)整合為單芯片ASIC,大幅降低系統(tǒng)BOM成本、芯片封裝及PCB尺寸與功耗。

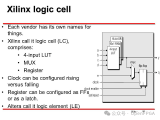

智原科技營(yíng)運(yùn)長(zhǎng)林世欽表示:“相較于以LUT單元來(lái)實(shí)現(xiàn)邏輯設(shè)計(jì)電路的FPGA,采用標(biāo)準(zhǔn)組件的ASIC少了相對(duì)多余的電路,提供較高的效能且減少不必要的功耗。智原為客戶降低整合風(fēng)險(xiǎn)以加速上市時(shí)程,加上我們的長(zhǎng)期供貨承諾,相信這個(gè)FPGA-Go-ASIC解決方案將協(xié)助客戶無(wú)后顧之憂地?fù)屨际袌?chǎng)商機(jī)。”

關(guān)于智原科技

智原科技(Faraday Technology Corporation, TWSE: 3035)為專用集成電路(ASIC)設(shè)計(jì)服務(wù)暨知識(shí)產(chǎn)權(quán)(IP)研發(fā)銷售領(lǐng)導(dǎo)廠商,通過(guò)ISO 9001與ISO 26262認(rèn)證,總公司位于臺(tái)灣新竹科學(xué)園區(qū),并于中國(guó)大陸、美國(guó)與日本設(shè)有研發(fā)、營(yíng)銷據(jù)點(diǎn)。重要的IP產(chǎn)品包括:I/O、標(biāo)準(zhǔn)單元庫(kù)、Memory Compiler、兼容ARM指令集CPU、LPDDR4/4X、DDR4/3、MIPI D-PHY、V-by-One、USB 3.1/2.0、10/100 Ethernet、Giga Ethernet、SATA3/2、PCIe Gen4/3、28G可編程高速SerDes,以及數(shù)百個(gè)外設(shè)數(shù)字及混合訊號(hào)IP。

-

FPGA

+關(guān)注

關(guān)注

1643文章

21977瀏覽量

614468 -

ARM

+關(guān)注

關(guān)注

134文章

9315瀏覽量

375294 -

asic

+關(guān)注

關(guān)注

34文章

1243瀏覽量

122027 -

單芯片

+關(guān)注

關(guān)注

3文章

461瀏覽量

35085 -

智原科技

+關(guān)注

關(guān)注

0文章

22瀏覽量

11266

原文標(biāo)題:智原FPGA-Go-ASIC成功打進(jìn)多元的應(yīng)用市場(chǎng)

文章出處:【微信號(hào):faradaytech,微信公眾號(hào):智原科技】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

JESD204B有專用于ADC/DAC和FPGA或ASIC的接口嗎?

ASIC和GPU的原理和優(yōu)勢(shì)

大多數(shù)FPGA的程序存儲(chǔ)器(FLASH)為什么都放在外面呢?FPGA的主要應(yīng)用

SAE 2024汽車動(dòng)力總成多元化技術(shù)論壇成功舉行

FPGA與ASIC的區(qū)別 FPGA性能優(yōu)化技巧

ASIC集成電路與FPGA的區(qū)別

FPGA和ASIC在大模型推理加速中的應(yīng)用

FPGA與ASIC的優(yōu)缺點(diǎn)比較

go語(yǔ)言如何解決并發(fā)問(wèn)題

FPGA做深度學(xué)習(xí)能走多遠(yuǎn)?

為低功耗FPGA、處理器和ASIC實(shí)施啟用LVDS鏈路

三十分鐘入門基礎(chǔ)Go Java小子版

將ASIC IP核移植到FPGA上——更新概念并推動(dòng)改變以完成充滿挑戰(zhàn)的任務(wù)!

智原FPGA-Go-ASIC成功打進(jìn)多元的應(yīng)用市場(chǎng)

智原FPGA-Go-ASIC成功打進(jìn)多元的應(yīng)用市場(chǎng)

評(píng)論