AXI總線作為一種線,可以掛若干主設(shè)備與從設(shè)備,如果若干主設(shè)備要同時(shí)訪問(wèn)總線,必然會(huì)導(dǎo)致總線需要仲裁。本文不涉及細(xì)節(jié),只簡(jiǎn)單減少原理,一般來(lái)說(shuō)這個(gè)東西不需要自己寫,ARM會(huì)提供,但是作為設(shè)計(jì)者要大致知道原理。

1. 所謂總線,是個(gè)什么意思。

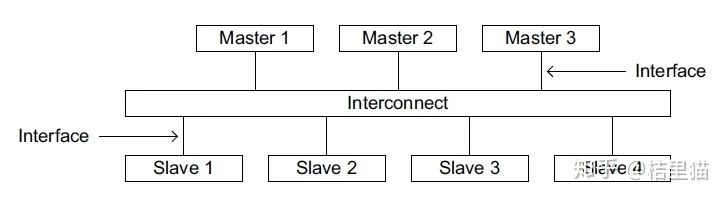

實(shí)際上是有個(gè)interconnect的模塊把所有東西連起來(lái)的。主設(shè)備會(huì)發(fā)起讀寫請(qǐng)求,從設(shè)備只能被動(dòng)接受。SOC中的CPU或者其他加速核心比如AI加速器是主設(shè)備。從設(shè)備一般是存儲(chǔ)啊外設(shè)啊之類的東西。基本的連接關(guān)系是這樣的。

2. 這個(gè)Interconnect里有什么東西

這個(gè)Interconnect連接了整個(gè)系統(tǒng),起到了仲裁的信號(hào)的作用,所以還是比較關(guān)鍵的。一般來(lái)講,瘋狂往interconnect上掛各種主從設(shè)備是會(huì)影響最后的時(shí)序的。由于AXI官方文檔IHI0022E里面貌似是沒(méi)有太多這方面介紹,換句話說(shuō),AXI協(xié)議并沒(méi)有規(guī)定主從設(shè)備連一起應(yīng)該如何工作,于是這里以賽靈思ug1037為基礎(chǔ)介紹一下。

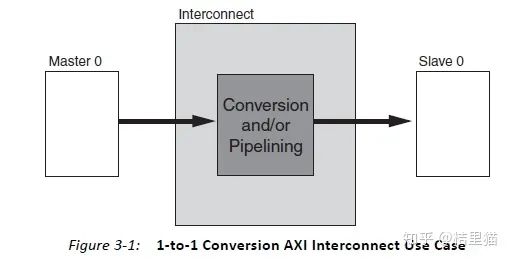

2.1 1to1 interconnect

這個(gè)賊簡(jiǎn)單,不用過(guò)多減少。。。一對(duì)一的連上去就好了。模范夫妻。

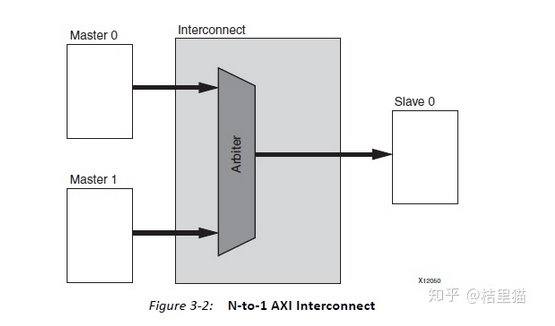

2.2 N-to-1 Interconnect

這個(gè)是稍微復(fù)雜的版本,類似于一妻多夫。。。如果有多個(gè)主設(shè)備,一個(gè)從設(shè)備。那中間需要一個(gè)仲裁器。某個(gè)主設(shè)備傳輸前請(qǐng)求總線,如果總線忙就等著。一般來(lái)講,最簡(jiǎn)單的仲裁原理是輪換優(yōu)先級(jí)。例如有三個(gè)主設(shè)備ABC。上次總線權(quán)限給了A。則下次的優(yōu)先級(jí)變?yōu)锽CA。

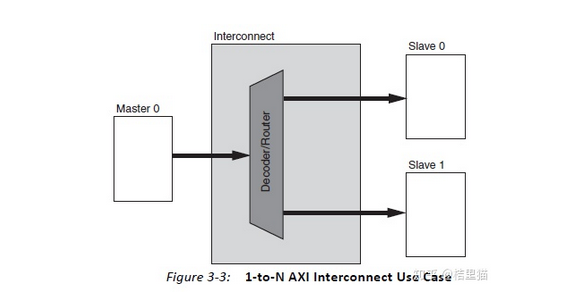

2.3 1-to-N Interconnect

1-to-N原理上比N-to-1簡(jiǎn)單。一夫多妻的版本。。。只需要簡(jiǎn)單判斷一下地址確認(rèn)要往哪個(gè)從設(shè)備里寫,基本上就是多路選擇器。不需要仲裁。總線也不會(huì)阻塞。

2.4 N-to-M Interconnect

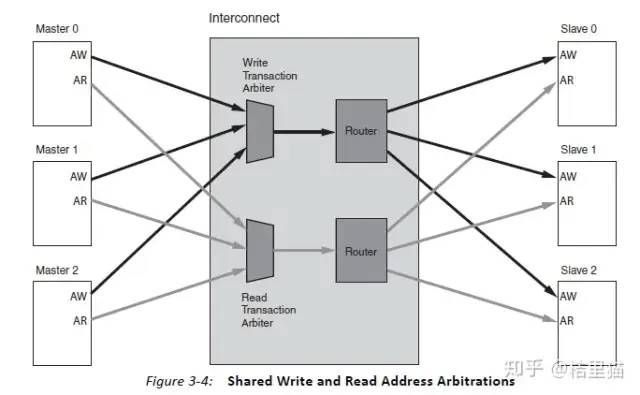

這種情況就比較復(fù)雜了。。。涉及到多設(shè)備時(shí)間管理。但實(shí)際上稍微復(fù)雜一點(diǎn)的SOC這類情況才是常態(tài)。

如上圖所示,讀寫通道是分開的。各自有一個(gè)仲裁器(Arbiter),仲裁原理和N-to-1是一致的。仲裁器會(huì)從所有寫請(qǐng)求和所有讀請(qǐng)求中各選出來(lái)一個(gè)來(lái)執(zhí)行。

3. 實(shí)際上用的時(shí)候怎么用

自己造AXI的各種輪子其實(shí)是比較繁瑣的,不僅僅是interconnect問(wèn)題,舉個(gè)簡(jiǎn)單的例子,AXI的DMA什么的自己造輪子DEBUG非常耗時(shí)。如果是FPGA,可以直接用XILINX的各路IP。如果是ASIC, 一般會(huì)有對(duì)應(yīng)的IP賣。比如ARM提供的最小系統(tǒng)一般會(huì)自帶這個(gè)interconnect。

如果SOC比較復(fù)雜,那還是有可能需要自己造這個(gè)輪子。比如為了壓榨總線的性能,如果兩個(gè)主設(shè)備訪問(wèn)的是兩個(gè)不同的從設(shè)備,如果想實(shí)現(xiàn)同時(shí)執(zhí)行,那對(duì)這個(gè)interconnect就有其他的要求。

4. 總結(jié)

一般情況下,總線可以理解為一種資源。由一對(duì)主從設(shè)備獨(dú)占使用。對(duì)于AXI來(lái)講,一般是兩種資源,讀總線和寫總線,通過(guò)某種仲裁方式分配給不同的主從設(shè)備。

-

soc

+關(guān)注

關(guān)注

38文章

4356瀏覽量

221895 -

總線

+關(guān)注

關(guān)注

10文章

2953瀏覽量

89428 -

AXI總線

+關(guān)注

關(guān)注

0文章

66瀏覽量

14511

原文標(biāo)題:SOC中AXI總線是如何連接的

文章出處:【微信號(hào):IC學(xué)習(xí),微信公眾號(hào):IC學(xué)習(xí)】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

NVMe IP之AXI4總線分析

AMD Versal Adaptive SoC Clock Wizard AXI DRP示例

NVMe簡(jiǎn)介之AXI總線

NVMe協(xié)議簡(jiǎn)介之AXI總線

一文詳解AXI DMA技術(shù)

ZYNQ基礎(chǔ)---AXI DMA使用

RISC-V芯片中使用的各種常用總線釋義

RS485總線的連接方式和注意事項(xiàng)

CAN總線在工業(yè)自動(dòng)化中的應(yīng)用

soc設(shè)計(jì)中的熱管理技巧

SOC芯片在汽車電子中的應(yīng)用

AMBA AXI4接口協(xié)議概述

前端總線是屬于什么總線

Xilinx NVMe AXI4主機(jī)控制器,AXI4接口高性能版本介紹

SOC中AXI總線怎么連接

SOC中AXI總線怎么連接

評(píng)論