什么是時鐘門控?

有幾個因素會影響電路的功耗。邏輯門具有靜態或泄漏功率,只要對其施加電壓,該功率大致恒定,并且它們具有由切換電線產生的動態或開關功率。Flip-flop觸發器非常耗電,大約占總功率的 20%。時鐘消耗的可能更多,可能約為 40%!全局時鐘無處不在,而且每個周期都會切換兩次。正如我們將看到的,時鐘門控避免了在不需要時鐘脈沖時切換時鐘。這減少了時鐘分配和觸發器的功耗,甚至可以減少邏輯門的動態功耗。

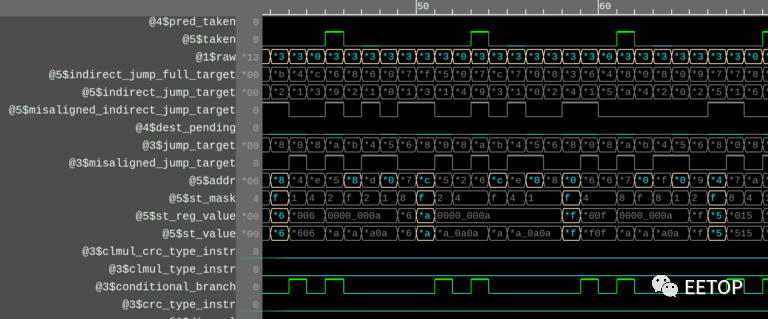

即使在繁忙的電路中,當你仔細觀察時,大多數邏輯電路大部分時間都沒有做有意義的工作。例如,在這個WARP-V CPU核心的跟蹤中,CPU幾乎每個周期都在執行指令。但計算分支目標的邏輯并不繁忙。它只需要用于分支指令。而浮點邏輯只需要用于浮點指令,等等。在下面的跟蹤波形中,大多數信號值是灰色的,表明它們沒有被使用。

顯示時鐘門控的 CPU 波形

如前所述,將時鐘信號驅動到觸發器會消耗總功率的很大一部分,因此觸發器可以將其輸入值傳播到其輸出以用于下一個執行周期。如果這些觸發器的大部分輸入信號都是無意義的,那么就沒有必要傳播它們浪費大量的功耗。

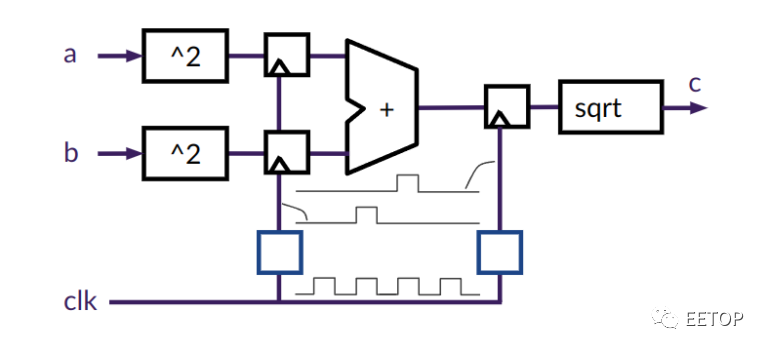

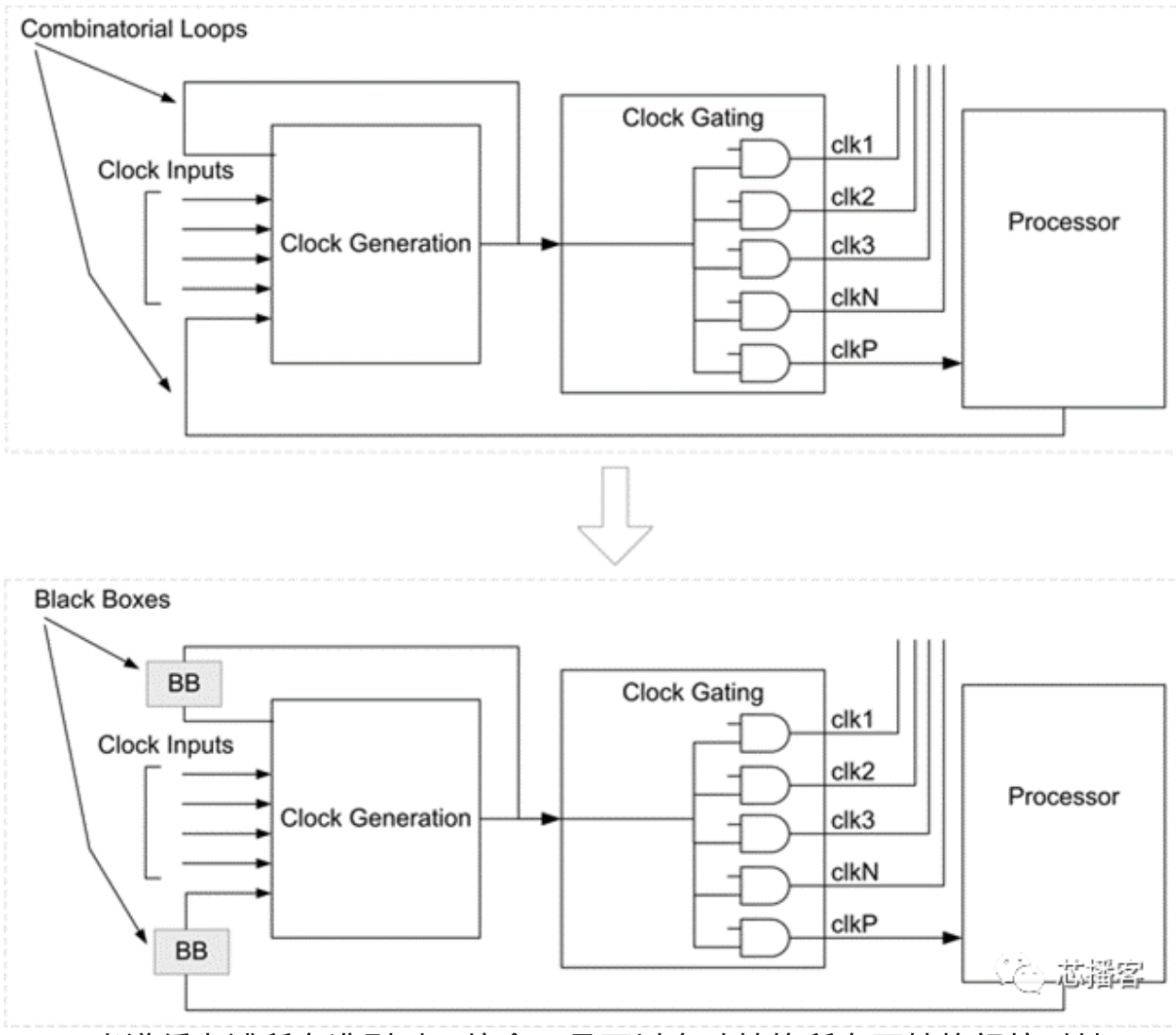

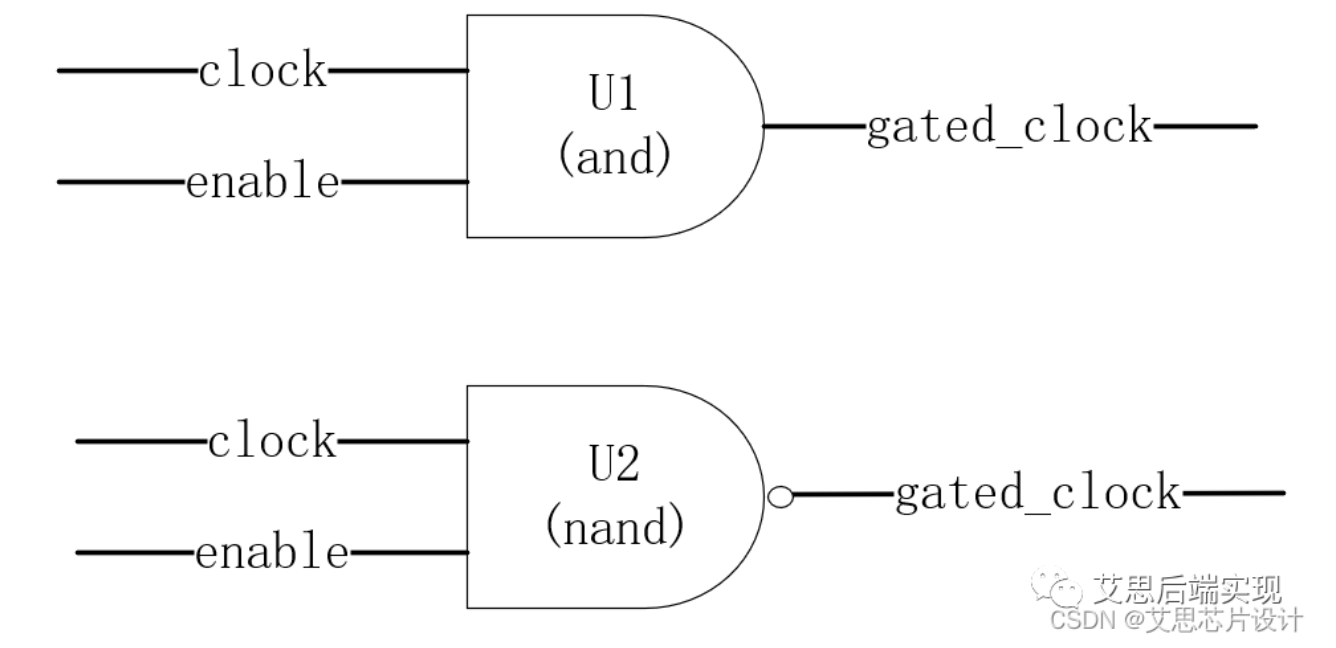

時鐘門控切斷了不需要的時鐘脈沖。(電路也可能被設計成依賴于沒有時鐘,但我們不要把事情和這種情況混淆)。下面的電路顯示了兩個時鐘門控塊(藍色),它們切斷了不需要的時鐘脈沖,只在進行有意義的計算時才剛打開時鐘脈沖。

時鐘門控圖示

除了減少時鐘分配和觸發器功耗外,時鐘門控還可以保證觸發器輸出在沒有時鐘脈沖時不會擺動。這降低了下游動態功耗。總之,與非門控電路相比,時鐘門控可以節省相當多的功率。

實施時鐘門控

時鐘門控的一個先決條件是知道什么時候信號有意義,什么時候沒有意義。這是事務級Verilog模型中固有的高級感知的一些方面。一個 "事務 "的邏輯是在表明其有效性的條件下表達的。因為一個單一的條件可以應用到事務所遵循的路徑上的所有邏輯,所以應用有效性的開銷是最小的。

有效性不僅僅是關于時鐘門控。可以說,它有助于是否有意義。例如,前面的CPU波形是來自TL-Verilog模型。調試變得更容易了,因為我們已經自動過濾掉了大部分的信號值,將它們識別為無意義的。我們知道它們是無意義的,因為自動檢查確保這些值不會被有意義的計算所消耗。

從一開始就有時鐘門控的全部意義可能并不明顯。我從來沒有參與過一個達到時鐘門控目標的項目。我們總是帶著大量的機會去做芯片。這是因為省電總是最后要實現的事情。功能必須是第一位的。沒有它,驗證就不能取得進展。邏輯設計人員在完成他們積壓的功能錯誤之前,不能給予時鐘門控任何真正的關注,而這要到結束時才會考慮。在這一點上,許多單元已經成功實現了沒有完全的時鐘門控。該項目無疑已經落后于計劃,而增加時鐘門控將需要重新實施,包括需要解決新的時序和芯片面積壓力。更糟糕的是,它將帶來全新的功能錯誤。因此,我們只能說,如果從一開始就將時鐘門控納入模型,則不需要任何附加成本。

結論

功耗現在是第一階設計約束,而時鐘門控是整個功率策略的重要組成部分。寄存器傳輸級的建模并不適合成功使用時鐘門控。事務級設計可以從一開始就設置時鐘門控,對項目進度產生積極的影響,如果您計劃生產具有競爭力的芯片,那么從一開始就采用穩健的時鐘門控方法非常重要。

審核編輯:湯梓紅

-

cpu

+關注

關注

68文章

11049瀏覽量

216159 -

觸發器

+關注

關注

14文章

2033瀏覽量

61930 -

時鐘門控

+關注

關注

0文章

7瀏覽量

6921

原文標題:時鐘門控的作用

文章出處:【微信號:bdtdsj,微信公眾號:中科院半導體所】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

fpga門控時鐘問題

什么是時鐘門控?如何去實線時鐘門控的設計呢

基于門控時鐘的低功耗電路設計方案

門控時鐘與時鐘偏移研究

時鐘門控的作用

時鐘門控的作用

評論