門控時鐘的分類

通過門控方式不同,一個門控時鐘通常可以分為下面基類,

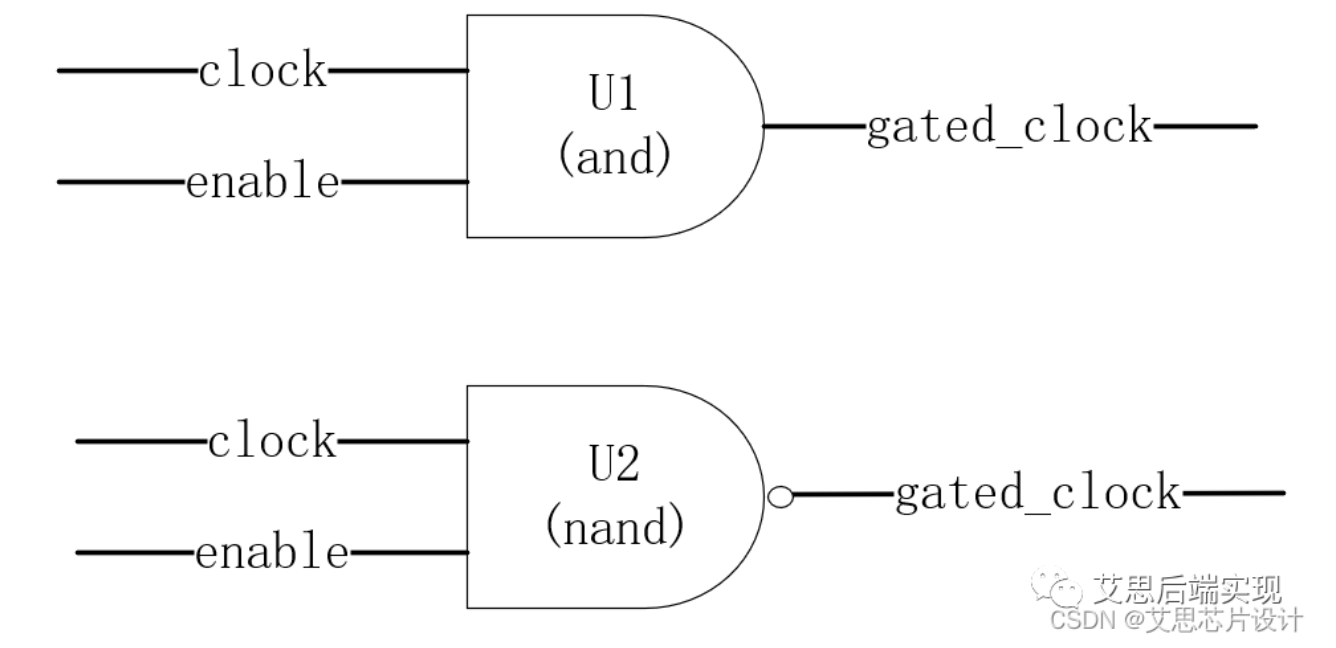

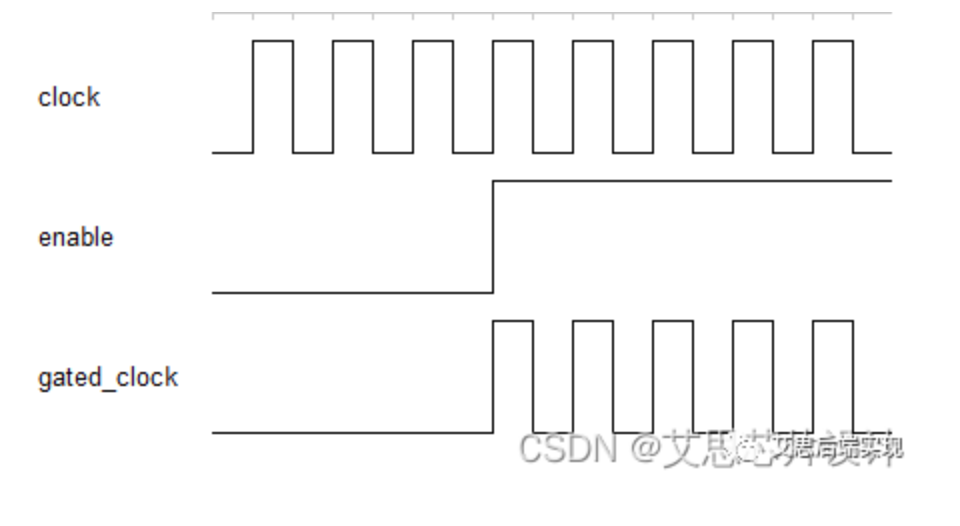

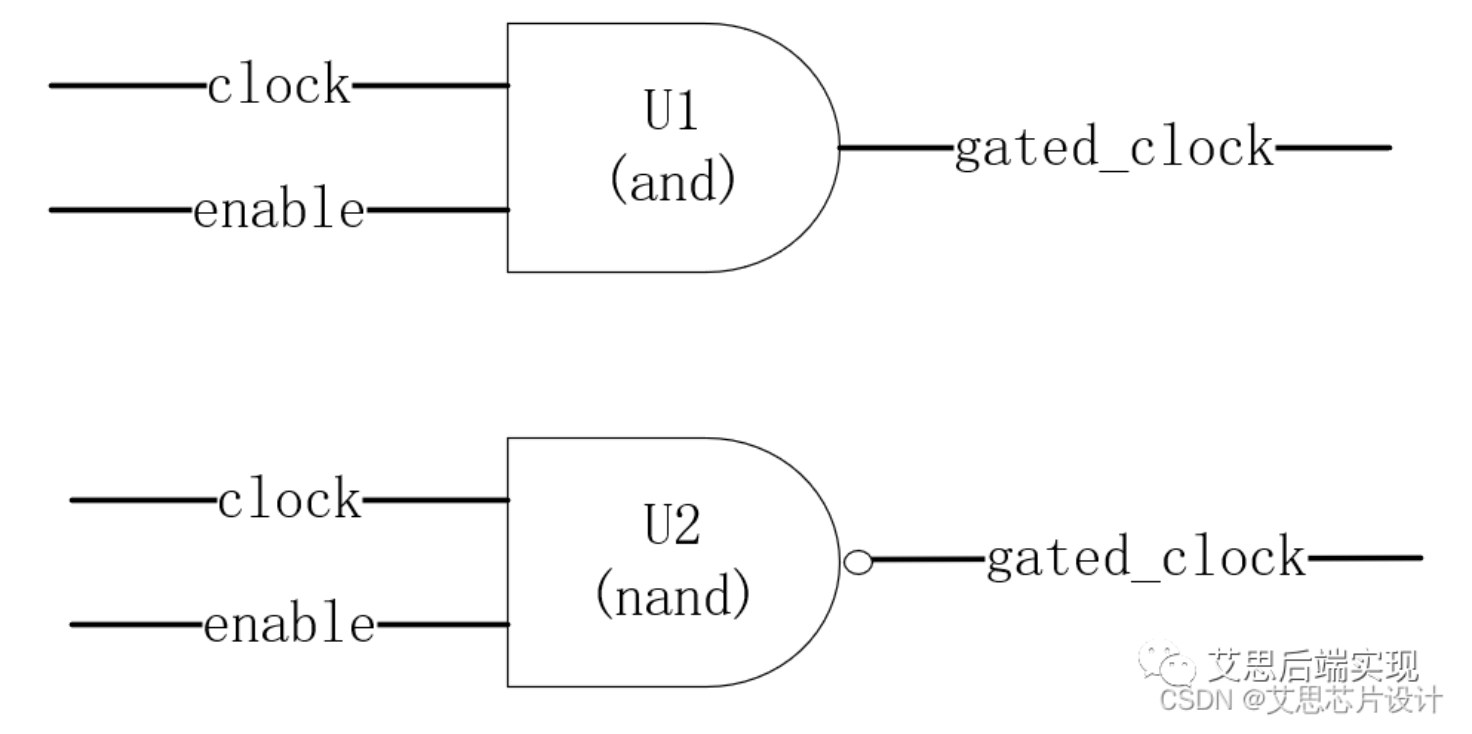

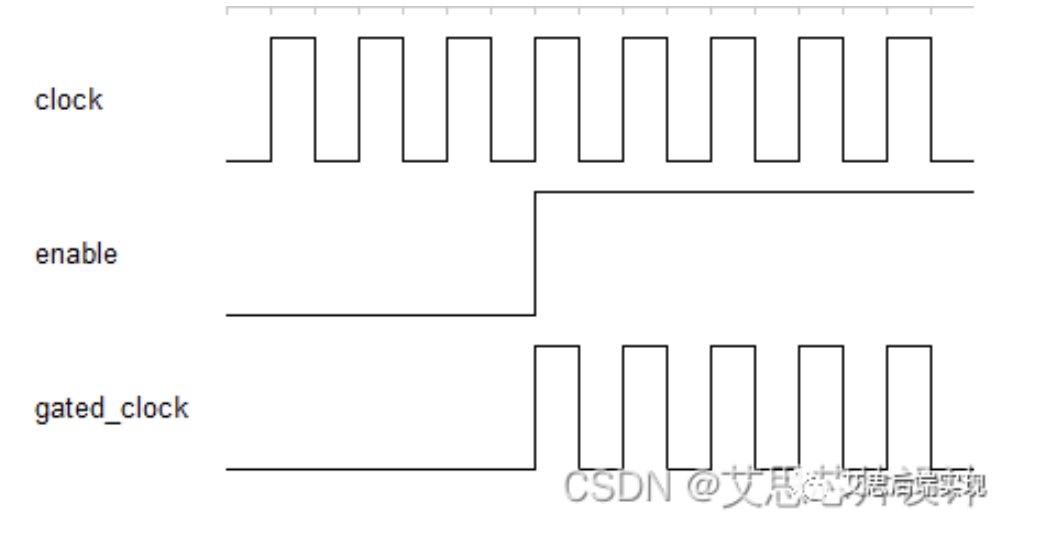

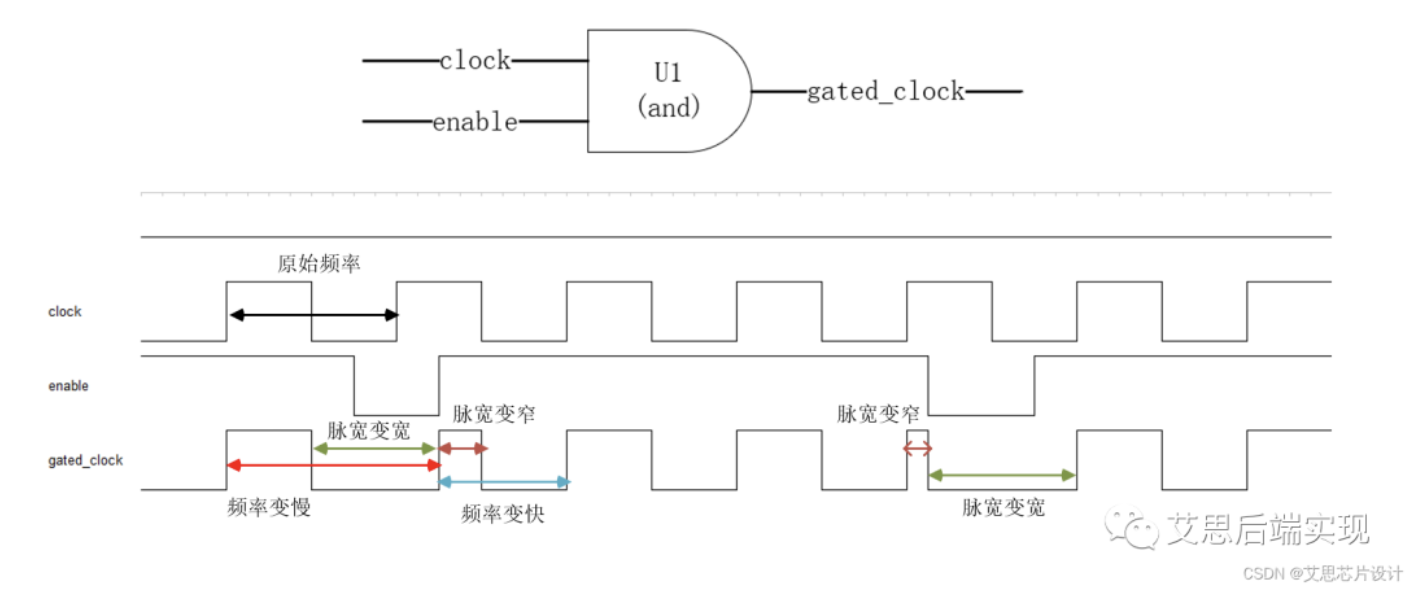

高有效(Active High)門控時鐘

通常使用與門(and)或者與非門(nand)實現(xiàn),

當使能信號為高的時候,時鐘才可以被釋放出去. 如果是nand,則輸出的時鐘是一個反向時鐘的波形

低有效(Active High)門控時鐘

通常使用與門(and)或者與非門(nand)實現(xiàn),

當使能信號為低的時候,時鐘才可以被釋放出去. 如果是nor,則輸出的時鐘是一個反向時鐘的波形

除過上述的情況,有時候也會使用復(fù)雜一些的clock gating結(jié)構(gòu),這里的波形就會復(fù)雜一些

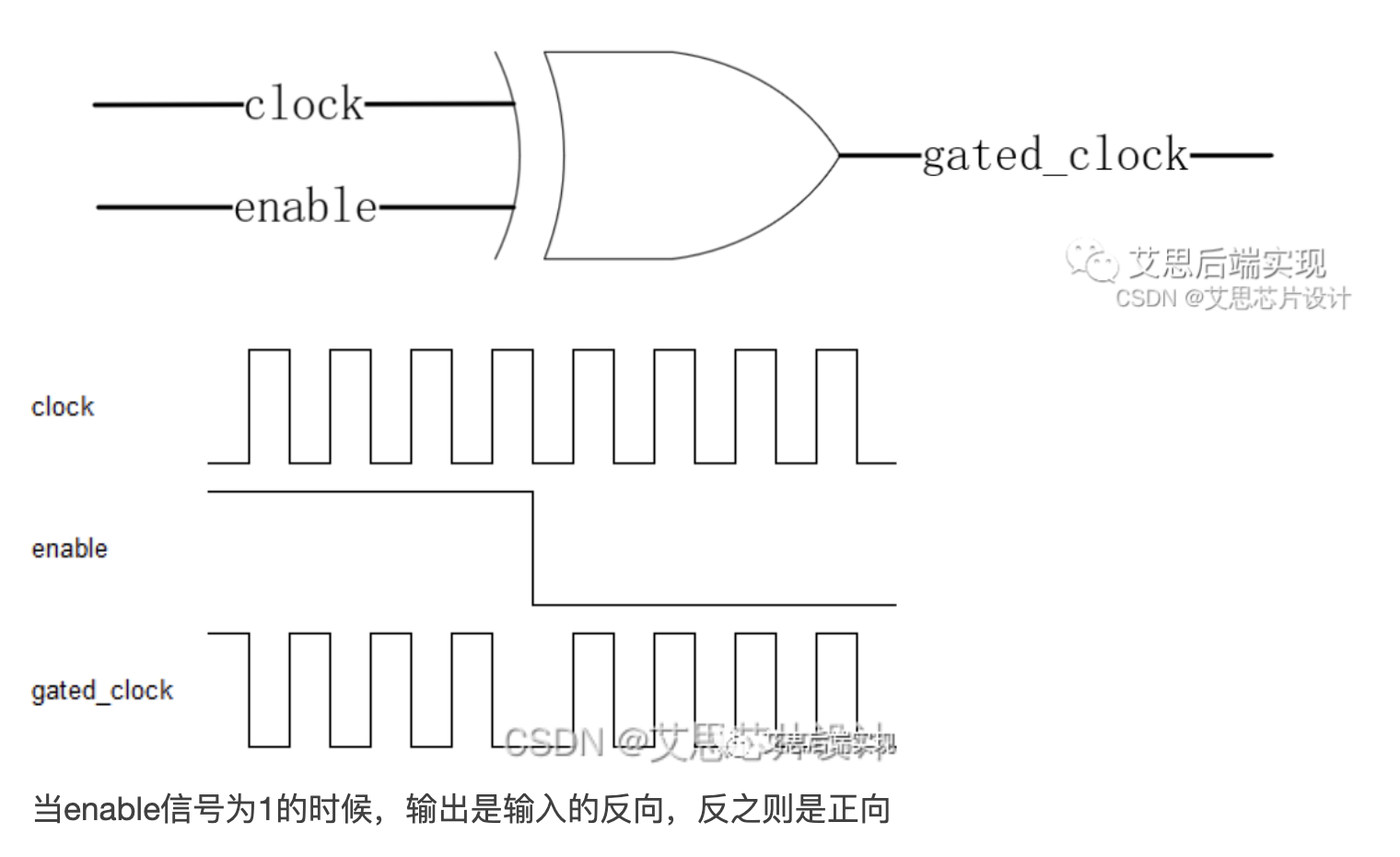

XOR結(jié)構(gòu)的門控時鐘

當enable信號為1的時候,輸出是輸入的反向,反之則是正向

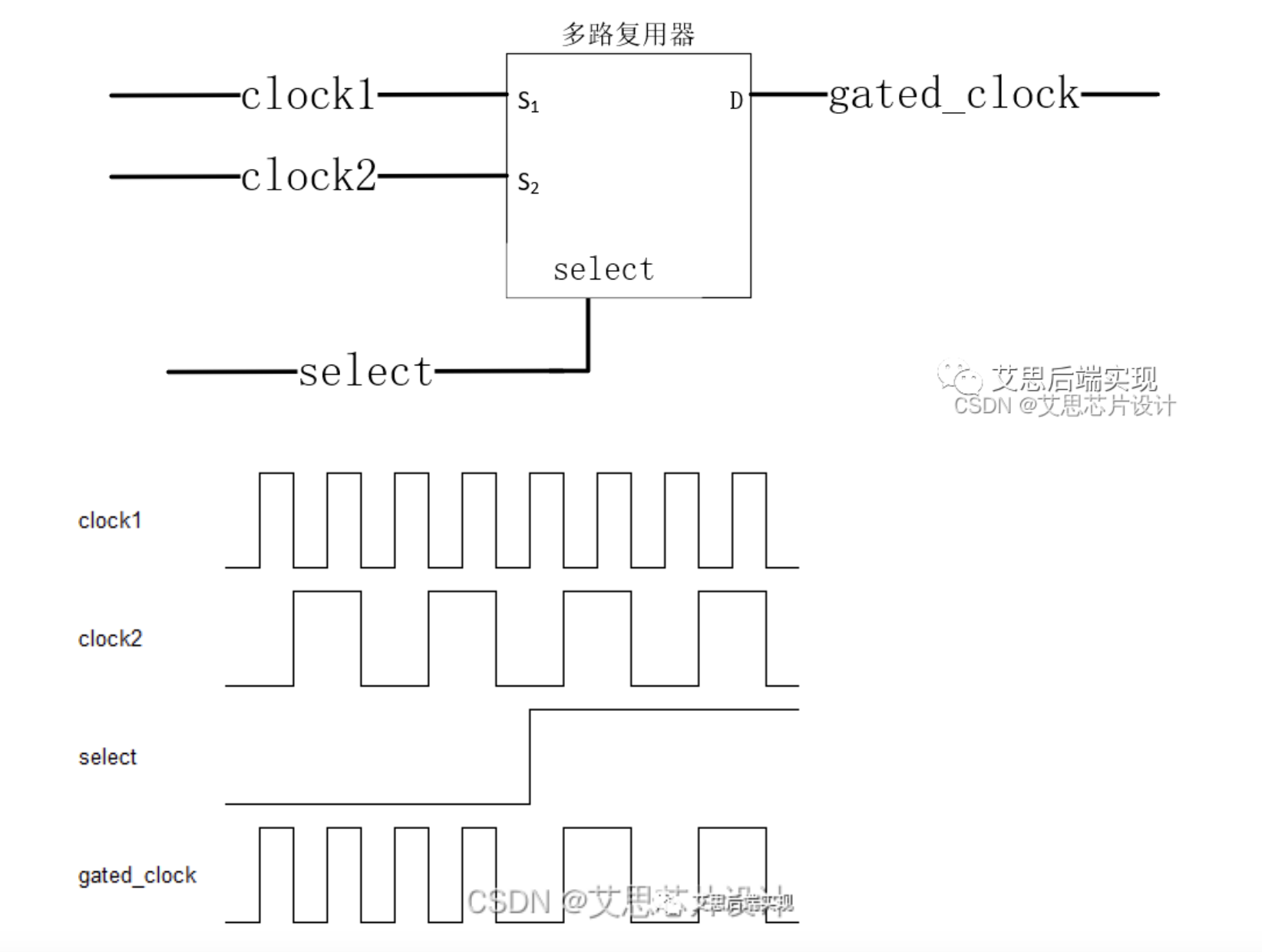

MUX結(jié)構(gòu)的門控時鐘

時鐘傳播單調(diào)性(unate)

靜態(tài)時序分析的基本原理是信號傳播,對于擁有明確單調(diào)性的傳播是構(gòu)建正確STA環(huán)境的基礎(chǔ),數(shù)據(jù)通路對單調(diào)性(unate)通常不敏感,但是時鐘通常是邊沿敏感信號,所以時鐘網(wǎng)絡(luò)的單調(diào)性在STA時序分析的形態(tài)中尤為重要。STA工具也只有在單調(diào)性明確的時鐘網(wǎng)絡(luò)上做正確的時序分析,否則大概率會在實際芯片里邊出現(xiàn)和STA不一致的情況。這點對于時鐘網(wǎng)絡(luò)的設(shè)計非常重要。

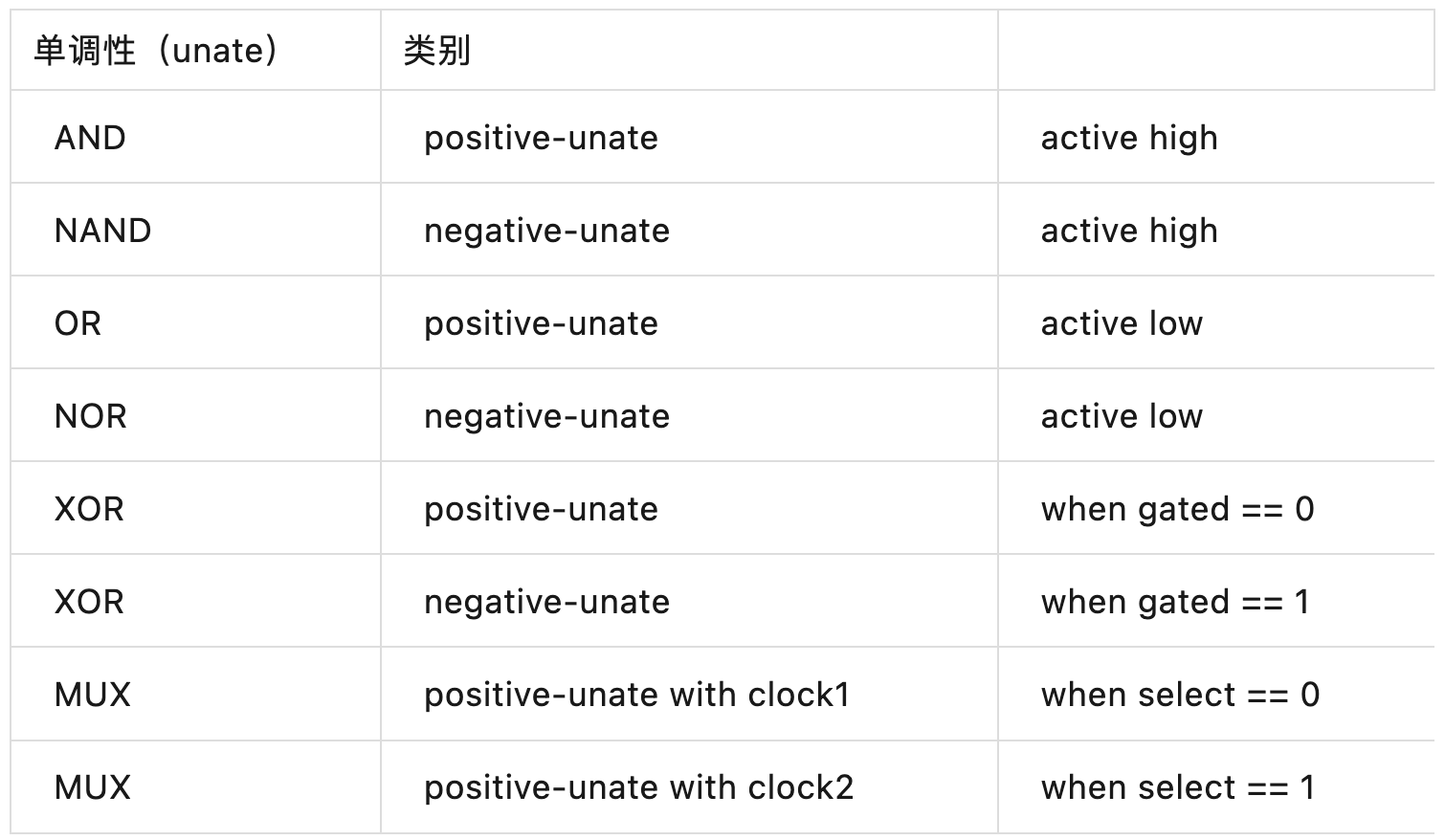

通過上述幾種門控始終結(jié)構(gòu),從單調(diào)時鐘的(unate)的角度來看,可以總結(jié)為下表

gating結(jié)構(gòu)

所以,對于所有在時鐘網(wǎng)絡(luò)上的門控時鐘,用戶都需要明確其單調(diào)性,以便STA進行正確的分析。

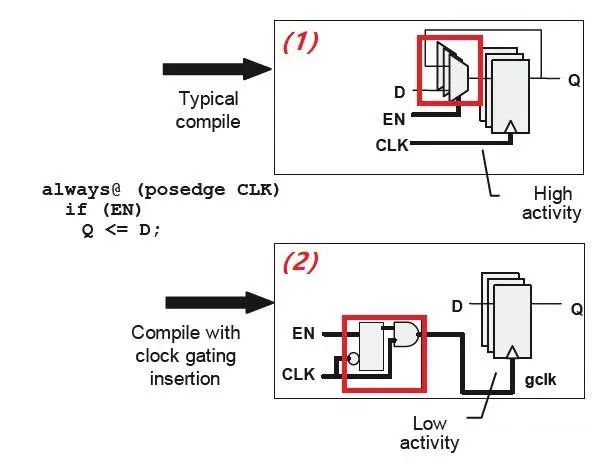

門控時鐘的的檢查(clock gating check)

通過上述描述,可以看到始終網(wǎng)絡(luò)對于靜態(tài)時序分析的重要性,所以在門控時鐘在時鐘網(wǎng)絡(luò)的傳播路徑上的檢查尤為重要。同樣,基于clock gating的結(jié)構(gòu),對于active high,active low的門控時鐘,通過STA工具。可以自動推斷(infer)出相應(yīng)的門控時鐘檢查(clock gating check),用戶可以理解,這里的clock gating結(jié)構(gòu)被STA所覆蓋。所以用戶在需要理解STA自動推斷的原理,從而確保自己的時鐘路徑被STA覆蓋

定義

工具判斷門控時鐘的基本標準如下

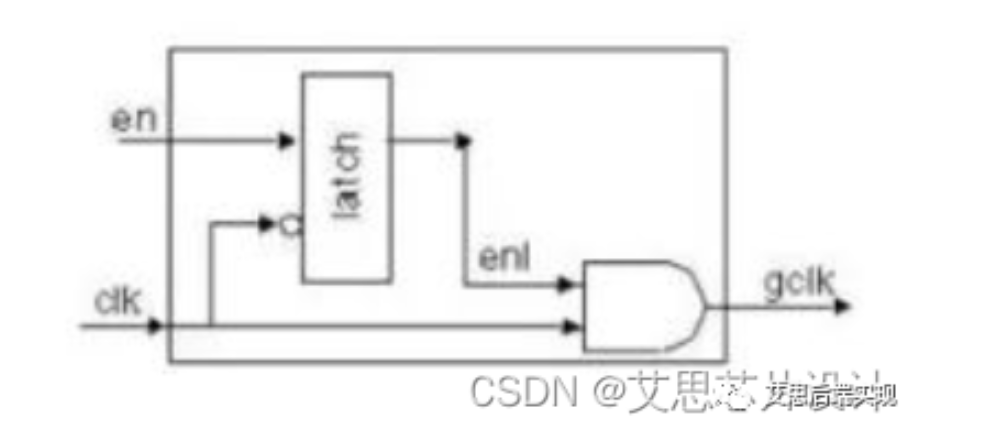

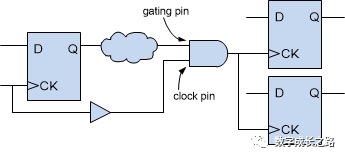

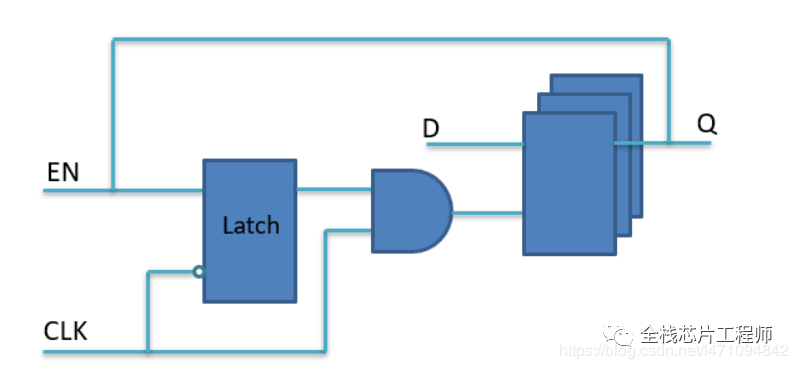

- 輸入的時鐘到輸出必須存在一個組合邏輯的傳播路徑。常規(guī)的與或非,或者常規(guī)的latch based 的clock gating結(jié)構(gòu)(見下圖),但是register的分頻結(jié)構(gòu),就不是一個clock gating。

-

輸入的端口必須包含clock,但是輸入到輸出的傳播必須包含數(shù)據(jù)路徑(gated 信號)。

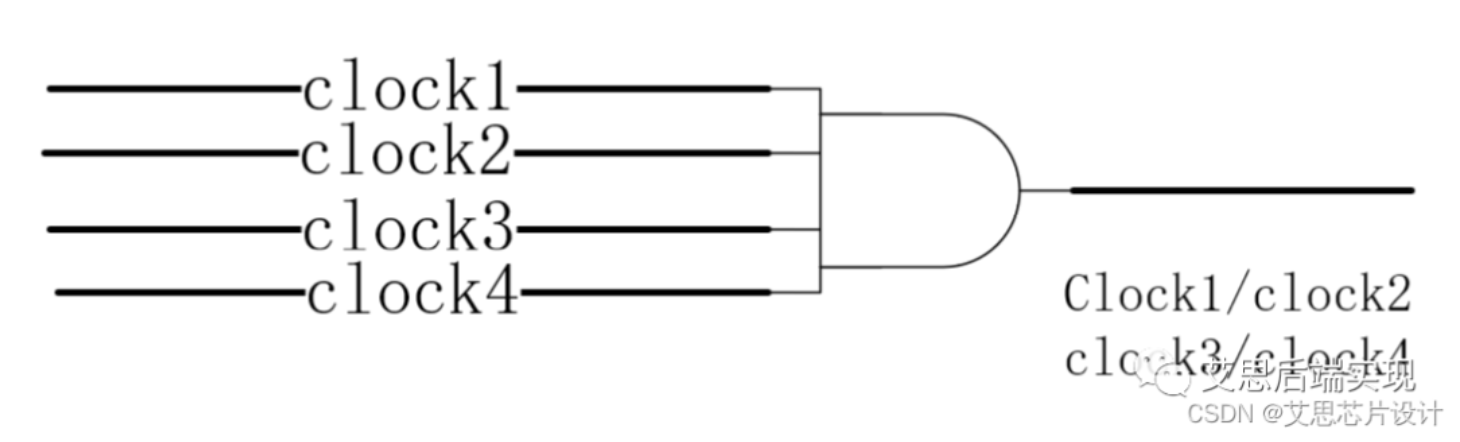

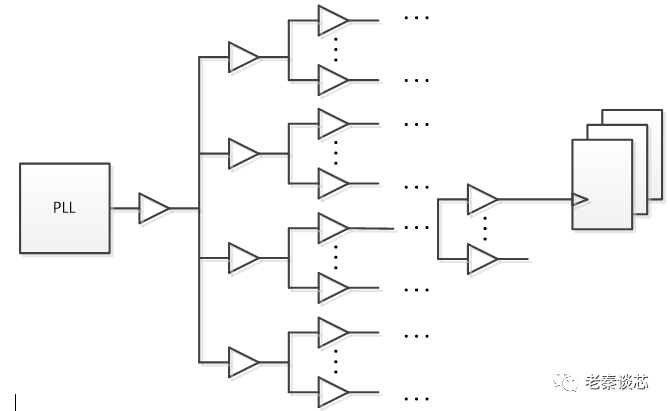

示例1: 組合邏輯的輸入都是clock,STA會自動將時鐘傳播到輸出,這樣輸出的會看到四個clock,這樣的結(jié)構(gòu)是無法判定為clock gating結(jié)構(gòu)的,需要用戶在使用的時候,當clock1有效的時候,clock2/3/4需要維持一個常1,否則輸出的clock會出現(xiàn)混亂

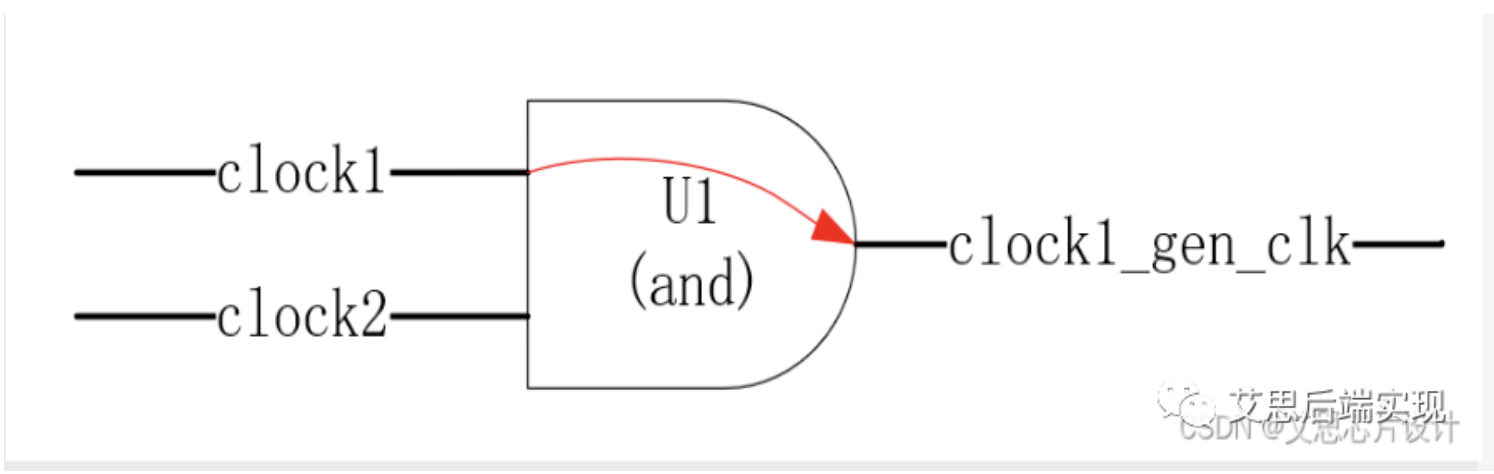

示例2: 輸入都是clock,但是用戶使用下列命令在輸出創(chuàng)建了一個gen-clockcreate_generated_clock -name clock1_gen_clk -divide_by 1 \\ -source clock1 [get_pins U1/Z]

由于這個AND只有clock1傳播過去,STA會自動推斷出這是一個clock gating結(jié)構(gòu),clock1到clock2的gating 檢查,clock2信號就是一個門控信號(enable)

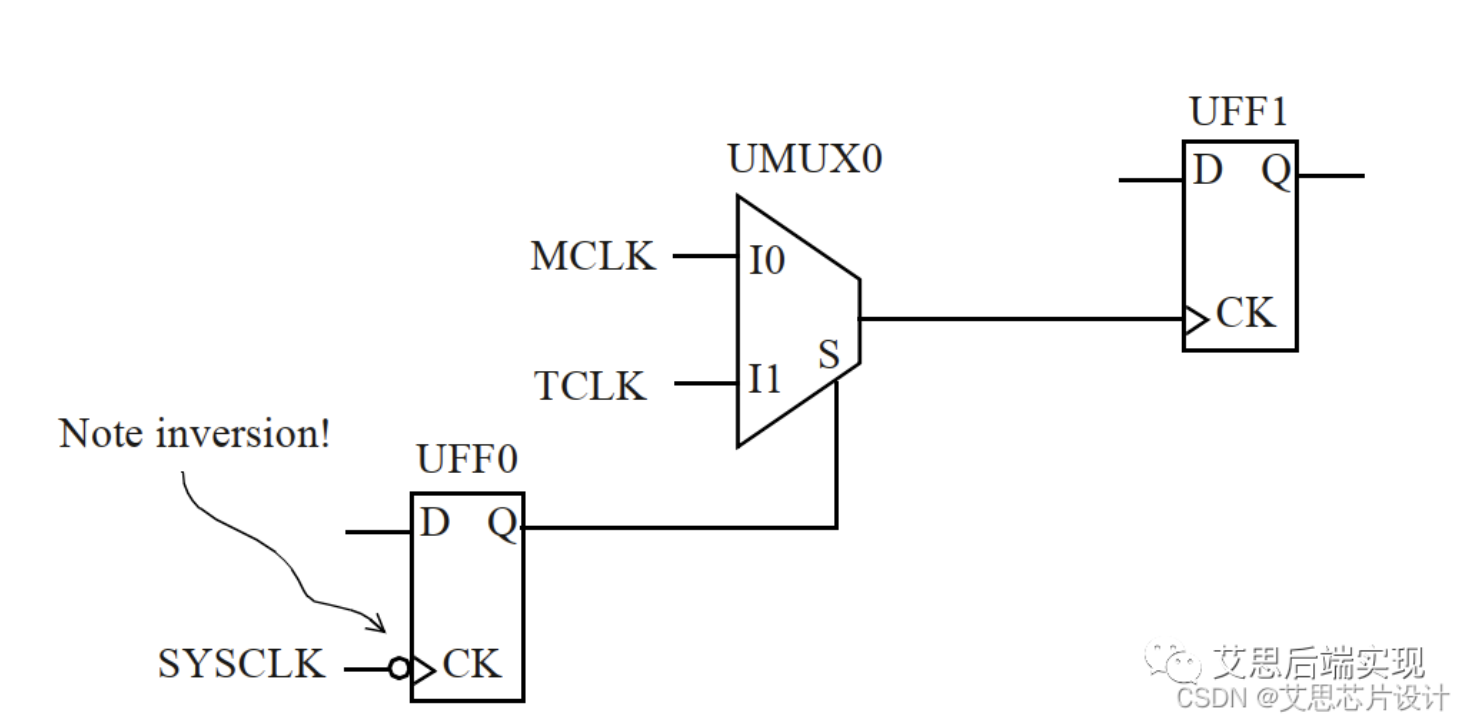

示例3 :對于一個復(fù)雜的門控時鐘無法自動推斷

這里的UMUX0滿足clock gating的結(jié)構(gòu)

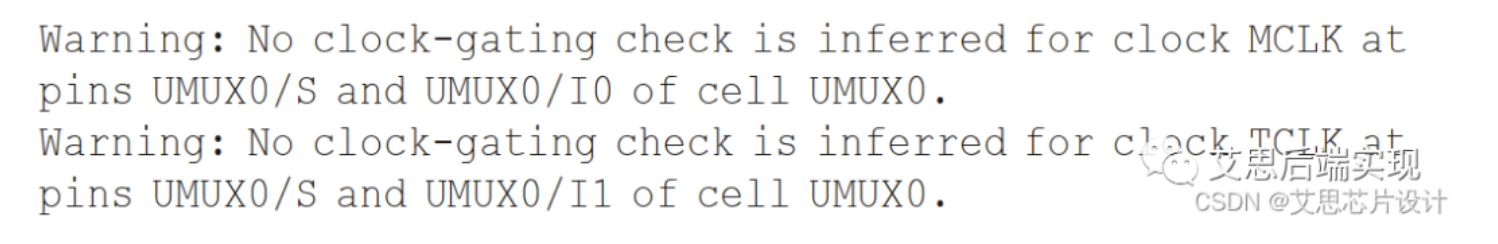

但是由于MUX結(jié)構(gòu)是一個非單調(diào)性傳播(none-unate),這樣一個clock gating結(jié)構(gòu)是無法自動推斷(auto-infer)出來的,所以在clock 傳播路徑上存在風險,這樣工具會給出如下的提示。需要用戶進一步處理

挑戰(zhàn)

門控時鐘是在clock的傳播路徑插入了與或非邏輯,設(shè)計人員通過一定的邏輯控制達到對時鐘的操作:

-

時鐘分頻:使用低頻門控信號與高頻時鐘和做AND操作:

clock_slow = clock_fast * slow_enable -

時鐘開合:使用半靜態(tài)信號(近乎于始終關(guān)斷控制):

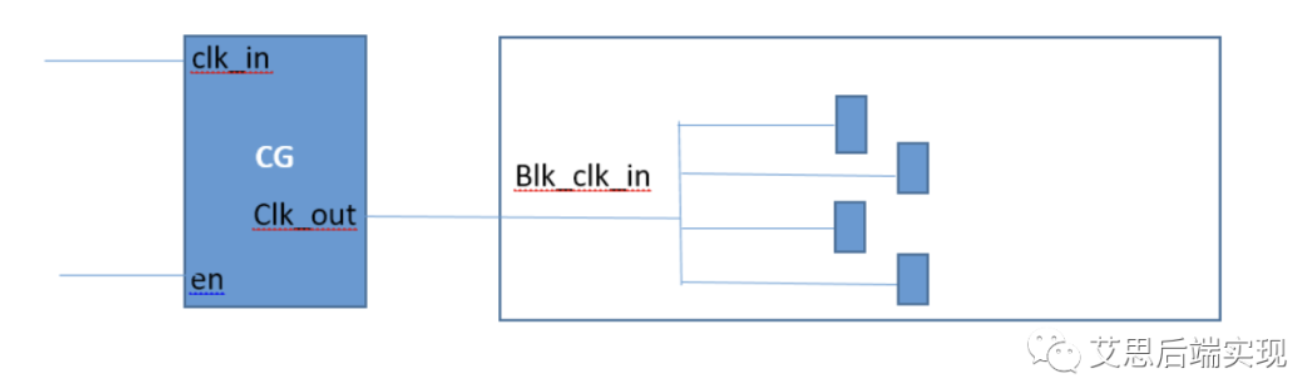

block_clock = sys_clock * block_enable -

時鐘選擇:使用半靜態(tài)信號(近乎于模式控制):

clock_out =(sel==1'b0)?func_clock : scan_clock或者使用latch/reg結(jié)構(gòu),設(shè)計一個防抖的時鐘切換,但是無論門控信號的產(chǎn)生有多么復(fù)雜,只要符合門控適中的結(jié)構(gòu),最后的clock gating check的點位是不會發(fā)生變化的,只是一個好的時鐘生成(clock-gen)的設(shè)計,可以對STA更友好的,推進項目質(zhì)量和加速項目收斂,這也是一個有經(jīng)驗的設(shè)計工程師的基本修為。

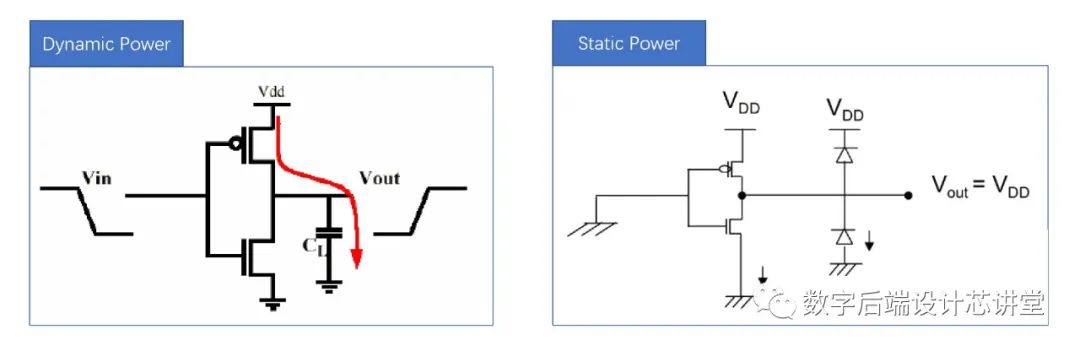

時鐘是周期的變化,如果和一個門控邏輯進行組合邏輯運算,通常會出現(xiàn)時鐘波形傳播的問題(clock crop 或者clock swallow):

在不同階段出現(xiàn)的enable信號,會導致clock的波形發(fā)生畸變

注意:在STA的timing report中,用戶是不會看到上述問題的影響的的,但是在實際芯片中,這種影響是真實發(fā)生的。 所以,clock-gating的邏輯,必須被clock-gating-check所覆蓋,并且需要謹慎地進行徹底修復(fù),對于工具不能自動推斷出來的clock-gating點,需要用戶重點關(guān)注和給出解決方案,否則在最后的芯片中會出現(xiàn)和STA完全不一致(無法通過STA定位)的時序問題。

未完待續(xù)… (To Be continued …)

這樣處理以后,LVS的std-cell的port mismatch也就完美解決了,

學好v2lvs,再也不用perl去patch source netlist了~~~~

【敲黑板劃重點】

理解門控時鐘檢查(clock-gating-check)和理解門控時鐘(clock-gating)同等重要,任何在clock tree上做的動作都需要額外的小心。

-

分頻器

+關(guān)注

關(guān)注

43文章

492瀏覽量

51181 -

STA

+關(guān)注

關(guān)注

0文章

52瀏覽量

19311 -

門控時鐘

+關(guān)注

關(guān)注

0文章

27瀏覽量

9121 -

XOR

+關(guān)注

關(guān)注

0文章

12瀏覽量

162373

發(fā)布評論請先 登錄

FPGA的時鐘門控是好還是壞?

通常有兩種不同的時鐘門控實現(xiàn)技術(shù)

什么是門控時鐘?如何生成門控時鐘?

為什么需要時鐘門控?時鐘門控終極指南

ASIC的clock gating在FPGA里面實現(xiàn)是什么結(jié)果呢?

門控時鐘檢查(clock gating check)的理解和設(shè)計應(yīng)用

門控時鐘檢查(clock gating check)的理解和設(shè)計應(yīng)用

評論