應(yīng)對(duì)系統(tǒng)級(jí)封裝SiP高速發(fā)展期,環(huán)旭電子先進(jìn)制程研發(fā)中心暨微小化模塊事業(yè)處副總經(jīng)理趙健先生在系統(tǒng)級(jí)封裝大會(huì)SiP Conference 2021上海站上,分享系統(tǒng)級(jí)封裝SiP技術(shù)優(yōu)勢(shì)、核心競(jìng)爭(zhēng)力及整合設(shè)計(jì)與制程上的挑戰(zhàn),獲得熱列回響。

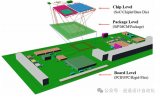

系統(tǒng)級(jí)封裝SiP的微小化優(yōu)勢(shì)顯而易見,通過(guò)改變模組及XYZ尺寸縮小提供終端產(chǎn)品更大的電池空間,集成更多的功能;通過(guò)異質(zhì)整合減少組裝廠的工序,加上更高度自動(dòng)化的工藝在前端集成,降低產(chǎn)業(yè)鏈復(fù)雜度;此外,系統(tǒng)級(jí)封裝SiP實(shí)現(xiàn)更好的電磁屏蔽功能,運(yùn)用模塑(Molding Compound)加上濺鍍(Sputter)或噴涂(Spray Coating)技術(shù),實(shí)現(xiàn)對(duì)外界電磁輻射的屏蔽與模塊內(nèi)部不同功能之間的屏蔽,特別適用于頻段越來(lái)越多的5G mmWave模塊與TWS真無(wú)線藍(lán)牙耳機(jī)等。另一方面,借由日月光和客戶共同設(shè)計(jì)的優(yōu)勢(shì)與扎實(shí)的封測(cè)技術(shù)到系統(tǒng)組裝的綜合能力,因應(yīng)產(chǎn)品上電源管理模塊、光學(xué)、傳感器模塊、射頻、可編程序存儲(chǔ)器(AP Memory)等等功能多樣化需求,模組化設(shè)計(jì)的便利性,更創(chuàng)新設(shè)計(jì)應(yīng)用,利用核心競(jìng)爭(zhēng)力的主板級(jí)組裝(Board Level)能力,為終端產(chǎn)品設(shè)計(jì)提供更大的靈活性。

先進(jìn)的工藝、測(cè)試及EE/RF硬件設(shè)計(jì)能力等將推動(dòng)系統(tǒng)級(jí)封裝SiP技術(shù)不斷創(chuàng)新,整體工藝成本將會(huì)越來(lái)越有優(yōu)勢(shì),其優(yōu)越的性能將越來(lái)越多地應(yīng)用在更多穿戴產(chǎn)品,如智能眼鏡、支持5G和AI的物聯(lián)網(wǎng)、智能汽車及生物醫(yī)學(xué)等對(duì)尺寸有特別要求的應(yīng)用領(lǐng)域,提供客制化設(shè)計(jì)與解決方案。

單面塑封 Single Side Molding, SSM

環(huán)旭電子系統(tǒng)級(jí)封裝SiP模塊微小化制程技術(shù)能力主要有單面塑封(Single Side Molding, SSM)和雙面塑封(Double Side Molding, DSM)。其中單面塑封主要核心技術(shù)是高密度SiP,以智能手表為例,可運(yùn)用008004被動(dòng)元件,間距達(dá)50μm,在20毫米左右的主板面積上可置入1000多顆元件;采用Molding形式,不需要Underfill點(diǎn)膠,加上Laser Marking 的能力,更可最大化節(jié)省空間與成本。

雙面塑封 Double Side Molding, DSM

雙面塑封(Double Side Molding, DSM)先進(jìn)制程技術(shù),為了有效地利用空間集成更多的元器件必須克服制程上的多種困難,尤其在雙面模具與屏蔽的制程、Cavity SMT性能的改善,加上鐵框與Flex 制程能力的開發(fā),目前已經(jīng)順利在2021年導(dǎo)入量產(chǎn)。環(huán)旭電子持續(xù)在先進(jìn)制程技術(shù)上研究發(fā)展,建置SMT并結(jié)合打線(Wire Bond)和粘晶(Die Bond) 整合產(chǎn)線,終端產(chǎn)品客戶可以直接投入晶圓,直接制造產(chǎn)出模塊的整合服務(wù),加快產(chǎn)品的上市時(shí)程,也利用扇出型封裝連結(jié)(Fan Out Interposer)等技術(shù)保持電路聯(lián)通性,確保電路不受高度集成的模塊影響,同時(shí)增加主板的空間利用率。

日月光與環(huán)旭電子深耕合作多年,積累在系統(tǒng)級(jí)封裝SiP從封測(cè)到系統(tǒng)端的組裝整體解決方案,未來(lái)將提供終端產(chǎn)品客戶更優(yōu)化的設(shè)計(jì)、制造上的整合與彈性化的營(yíng)運(yùn),發(fā)展高性能、微小化模塊,加速迎來(lái)系統(tǒng)級(jí)封裝SiP新應(yīng)用機(jī)會(huì)。

審核編輯 :李倩

-

SiP

+關(guān)注

關(guān)注

5文章

523瀏覽量

106171 -

物聯(lián)網(wǎng)

+關(guān)注

關(guān)注

2927文章

45959瀏覽量

388662 -

RF

+關(guān)注

關(guān)注

65文章

3174瀏覽量

168554

發(fā)布評(píng)論請(qǐng)先 登錄

系統(tǒng)級(jí)封裝電磁屏蔽技術(shù)介紹

AM625SIP 通用系統(tǒng)級(jí)封裝,采用 Arm? Cortex-A53? 和集成 LPDDR4數(shù)據(jù)手冊(cè)

3D封裝與系統(tǒng)級(jí)封裝的背景體系解析介紹

了解面向蜂窩物聯(lián)網(wǎng)的NRF9151 SiP

SiP藍(lán)牙芯片在項(xiàng)目開發(fā)及應(yīng)用中具有什么優(yōu)勢(shì)?

深入解析:SiP與SoC的技術(shù)特點(diǎn)與應(yīng)用前景

一種新型RDL PoP扇出晶圓級(jí)封裝工藝芯片到晶圓鍵合技術(shù)

SIP封裝技術(shù):引領(lǐng)電子封裝新革命!

嵌入式板級(jí)封裝在高壓應(yīng)用中的新挑戰(zhàn)—微區(qū)缺陷造成的局部放電

一文讀懂系統(tǒng)級(jí)封裝(SiP)技術(shù):定義、應(yīng)用與前景

為什么MiniLED、系統(tǒng)級(jí)SIP封裝要用水洗型焊錫膏?

SiP技術(shù)的結(jié)構(gòu)、應(yīng)用及發(fā)展方向

系統(tǒng)級(jí)封裝(SiP)技術(shù)介紹

系統(tǒng)級(jí)封裝工藝流程說(shuō)明

AM625SIP處理器如何透過(guò)整合LPDDR4,加快開發(fā)速度

系統(tǒng)級(jí)封裝SiP整合設(shè)計(jì)的優(yōu)勢(shì)與挑戰(zhàn)

系統(tǒng)級(jí)封裝SiP整合設(shè)計(jì)的優(yōu)勢(shì)與挑戰(zhàn)

評(píng)論