有一個(gè)很無語的問題,什么是register?天天在配寄存器,但是不知道寄存器是什么。寄存器的地址偏移有的是1,有的是4。這個(gè)偏移量為什么偏移不是3?偏移量和register的data位數(shù)有沒有關(guān)系

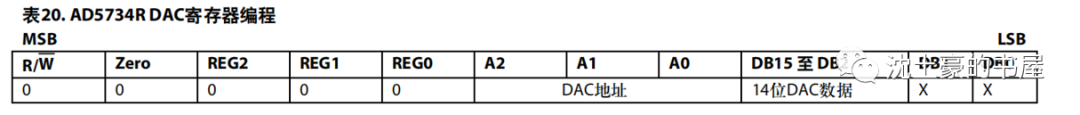

基本隨便打開一份數(shù)字IC的數(shù)據(jù)手冊我們就會(huì)得到designer提供的register table。

24bit的register,A2:A0 選擇DAC地址,DB15:DB2設(shè)置DAC輸出電壓。

給自己的一點(diǎn)理解:

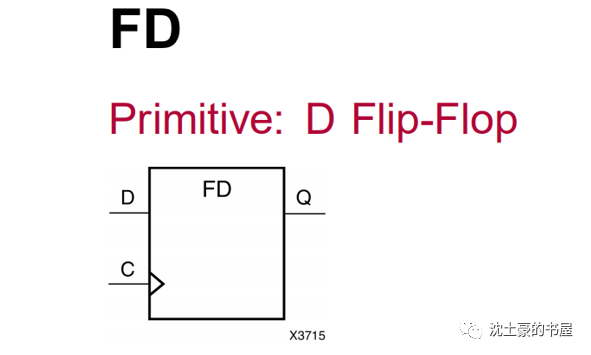

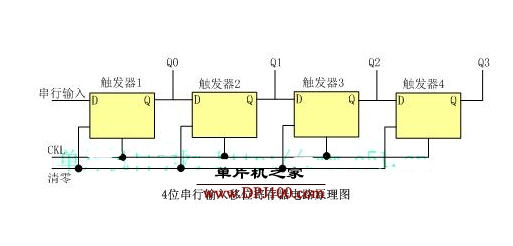

所有register,如果是接入clk的,xilinx稱為原語D flip-flop,就是大學(xué)本科的教材,D觸發(fā)器。

有32 bit的 register,就是32個(gè)DFF。DFF值從哪里來的?就是RTL級code的數(shù)百個(gè)module/IP里面input,output,reg信號。

這些信號拉到哪里去?拉到reg access的module,這個(gè)reg access的module就是通過填表,通過腳本gen出來的電路。

這個(gè)module port數(shù)非常大,大到只要register table里的有的信號,就會(huì)從其他各個(gè)模塊電路拉進(jìn)來,input output信號極其多。

這份文檔有描述FPGA/ASIC狀態(tài)寄存器和控制寄存器的做法:

csrGen: Automated CSRs for ASIC/FPGA Processor Interfaces .pdf

control/status registers (CSRs),的意思IC內(nèi)部的控制寄存器和狀態(tài)寄存器。

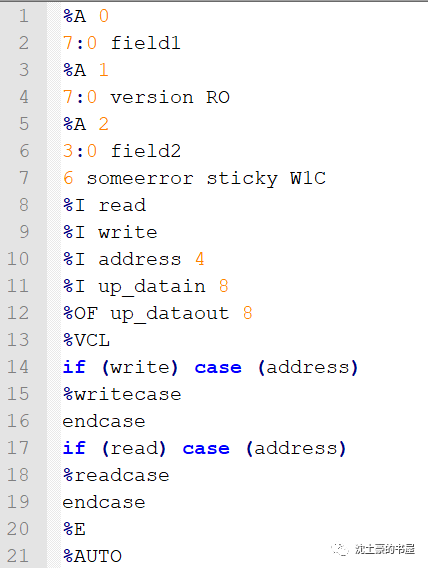

文檔大概的意思是說是用csrGen寫的一個(gè)腳本一樣的code,用戶可以通過填寫register table,最后可以綜合生成verilog register RTL code。

填表

用戶填表:

大概的意思是:

第一行就是定義:A就是register的地址address縮寫, 為0x0,共8bit,名字field1

第三行就是定義:A就是register的地址address縮寫, 為0x1,共8bit,名字version,類型是RO

后面還有一些W1C,wite 1 clear register value,這種太難了我也看不懂怎么實(shí)現(xiàn)的。我們就看一個(gè)register讀的,和寫的。

后面通過它寫的CSRGen,可以gen出一份RTL code。

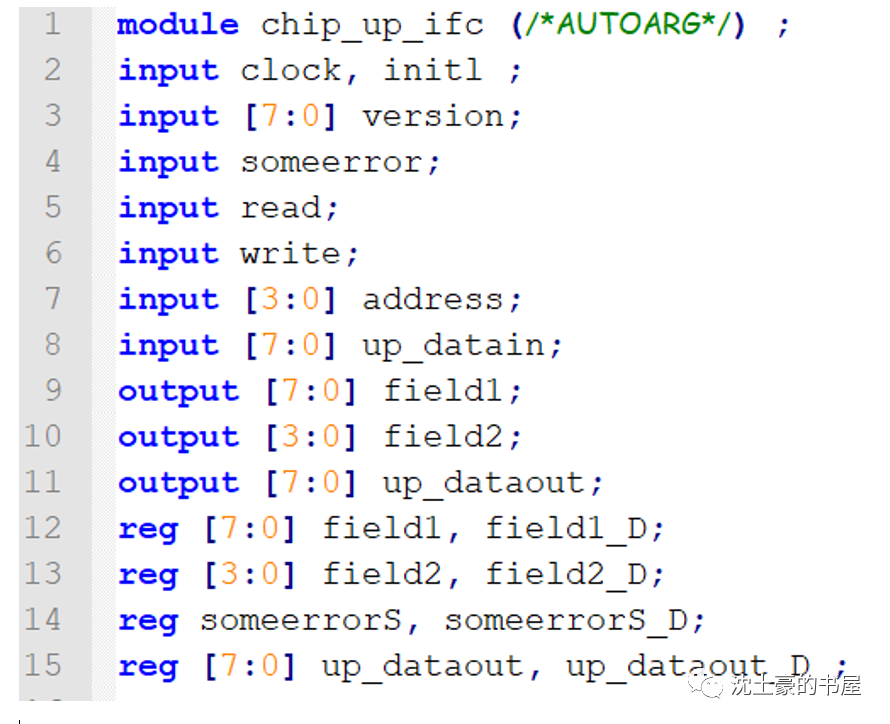

我們來看一下上面csrGen出來的RTL code。

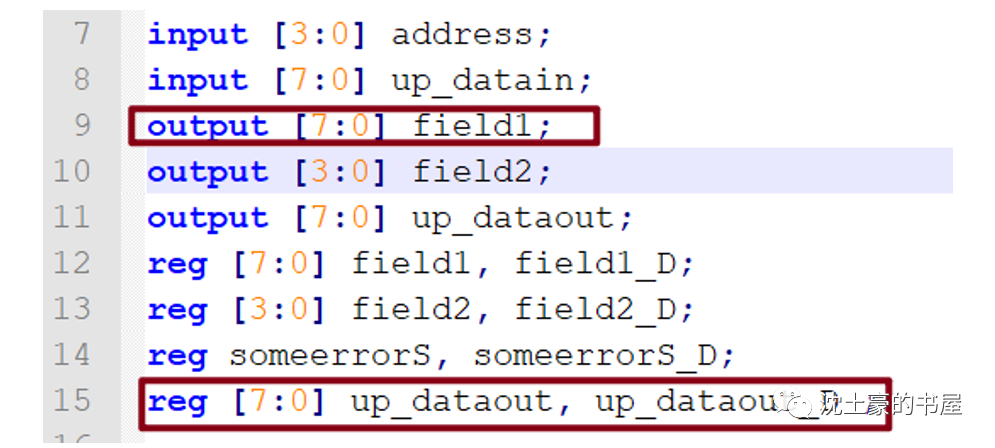

RTL級code定義了一個(gè)module,可以看到實(shí)際上對于讀寫指令,實(shí)際上就是1bit控制信號read/write,傳入的address[3:0],和up_datain[7:0]。

同時(shí)可以看到剛才看到RO類型的寄存器8bit version,實(shí)際上是從其他IP拉過來的,可以認(rèn)為IC內(nèi)部有很多個(gè)module/IP,這個(gè)viersion[7:0]就是從其他IP拉給chip_up_ifc 模塊的。

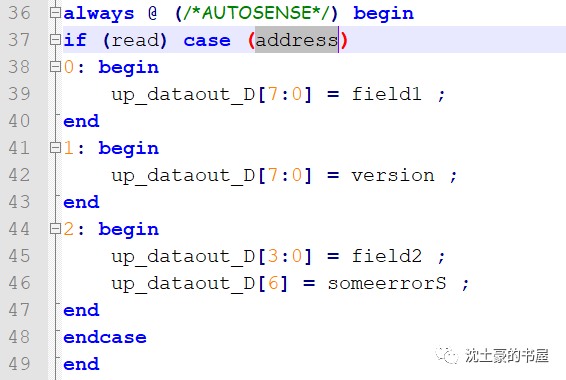

Read

當(dāng)我們?nèi)プx寫reg的時(shí)候,實(shí)際上就傳入read的命令和address。

RTL怎么實(shí)現(xiàn)的呢?就是通過在chip_up_ifc,在敏感列表響應(yīng)到read == 1’b1,采樣address值,通過case匹配,把需要RW的register地址,賦值到用戶的讀寫reg的接口上,即up_dataout_D[7:0] = version ;

version是其他module拉線來的,對于這個(gè)chip_up_ifc來說是input信號,up_dataout_D[7:0]是chip_up_ifc輸出的。

Write

當(dāng)我們?nèi)憆eg的時(shí)候,實(shí)際上就傳入write的命令和address和data值。

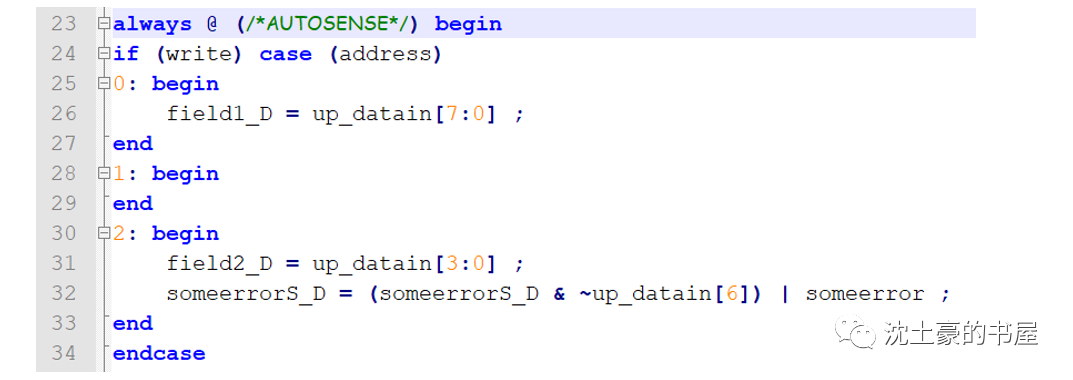

RTL級code如下,當(dāng)always塊敏感列表有write指令的時(shí)候,

看到case敏感列表里面是address,這里IC內(nèi)部排布的reg地址是從0 1 2 3 4….

當(dāng)對address 0,寫的時(shí)候,就把用戶想要寫入的數(shù)據(jù)up_datain[7:0],賦值給address 為0的field1_D。

我們剛才填寫的register profile就是

%A 0

7:0 field1

這里是對field1_D賦值而不是field1的原因是,在內(nèi)部生成了2個(gè)reg。一個(gè)是field1,field1_D。以我?guī)讉€(gè)禮拜的RTL coding基礎(chǔ),猜測是防止直接操作field1影響它原本所在的電路,通過下一個(gè)clk信號,

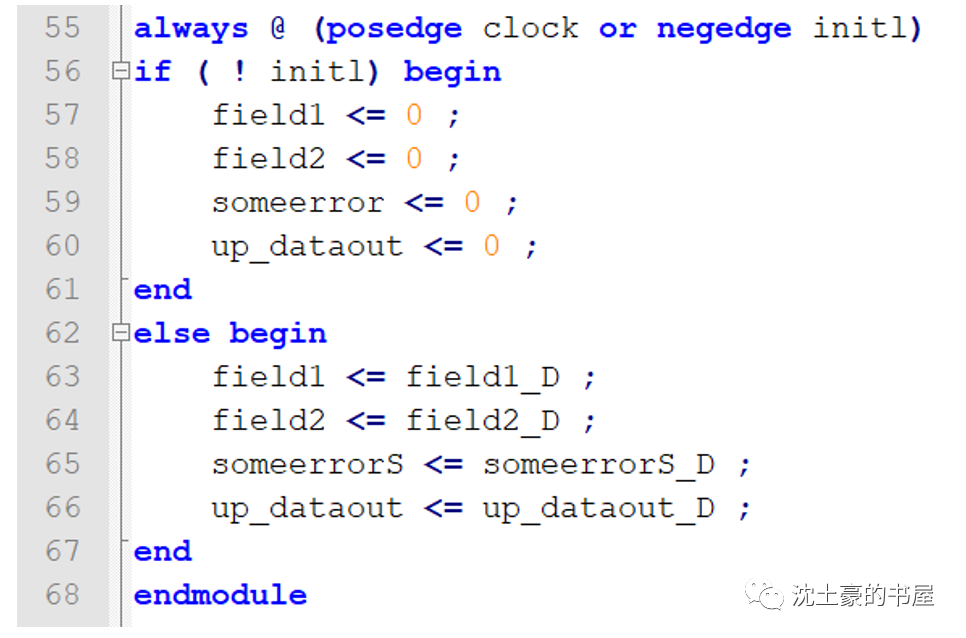

才把field1 <= field1_D,打了一拍。

RTL在下面63行也有體現(xiàn)。register的初值怎么做到的,也在always塊的init1下降沿觸發(fā)賦值有體現(xiàn)。

所以就有了以下結(jié)論,

Q:IC內(nèi)部的寄存器偏移地址一定是1或4,有什么含義嗎?

A:沒有任何意義。這邊address,在always塊每次匹配的是多少就是訪問的哪個(gè)reg,它可以偏移1,偏移100,1000都可以,甚至排布可以是1 3 5 7 9;

A:每個(gè)address獲得的reg數(shù)據(jù)位寬和偏移有關(guān)系嗎?

Q:也沒有,想定義每個(gè)address的reg的位寬是13個(gè)bit都可以,并不是8 /16/32 bit。RTL決定了本質(zhì)是多少個(gè)DFF。在clock節(jié)拍下寄存下別的module拉過來的信號值。但是多少考慮到數(shù)據(jù)位寬,也要定義成8/16/32吧。

A:上面結(jié)論是不是都對的?

Q:不一定,都是我猜的,其實(shí)我是做硬件的不太懂FPGA,有幸在南郵讀書期間和FPGA coder聯(lián)調(diào)過小半年。這邊我猜測:軟件跑在SOC,SOC有些reg地址,好像就是access sram,sram有大小的,8k的sram就被分成了那么多地址。軟件那邊定義的應(yīng)該有關(guān)聯(lián)的吧?RTL實(shí)現(xiàn)的reg是無關(guān)聯(lián)的。

-

寄存器

+關(guān)注

關(guān)注

31文章

5425瀏覽量

123627 -

Register

+關(guān)注

關(guān)注

0文章

36瀏覽量

14139 -

地址

+關(guān)注

關(guān)注

1文章

32瀏覽量

10981

發(fā)布評論請先 登錄

寄存器是什么?怎么操作寄存器點(diǎn)亮LED燈?

寄存器與移位寄存器

數(shù)據(jù)寄存器,數(shù)據(jù)寄存器是什么意思

寄存器培訓(xùn)教程

移位寄存器怎么用_如何使用移位寄存器_移位寄存器的用途

寄存器變量

移位寄存器的原理

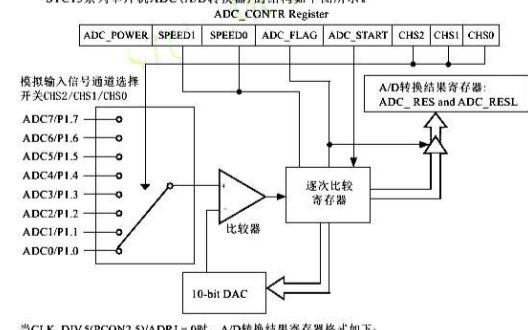

AD轉(zhuǎn)換寄存器設(shè)置

單片機(jī)工作寄存器作用 單片機(jī)常用專用寄存器

CPSR寄存器和APSR寄存器的組成

什么是寄存器

什么是寄存器

評論