之前在Trion上一直強(qiáng)調(diào)驅(qū)動(dòng)PLL要走pllin管腳。但是如果在硬件設(shè)計(jì)之時(shí)沒有注意而把PLL輸入管腳放置在普通GPIO也不是完全沒有辦法。

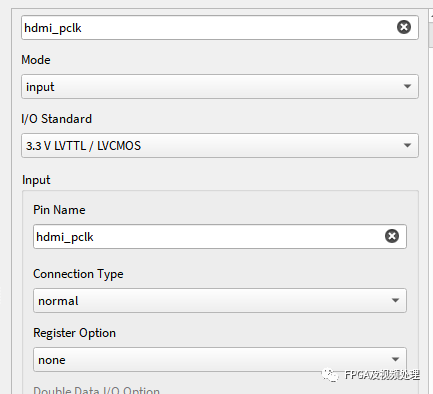

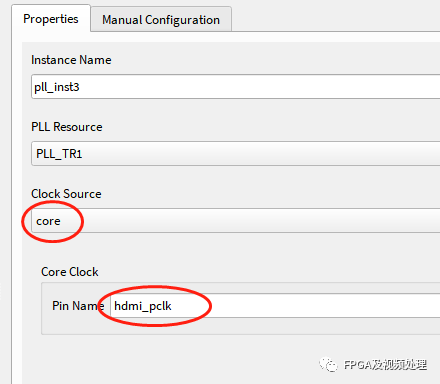

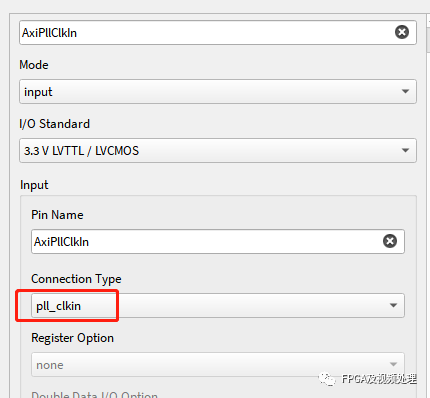

(1)如果放在了GCLK上,Connection Type設(shè)置成GCLK,PLL的時(shí)鐘源設(shè)置成Core;

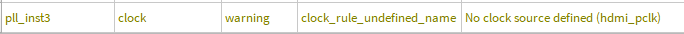

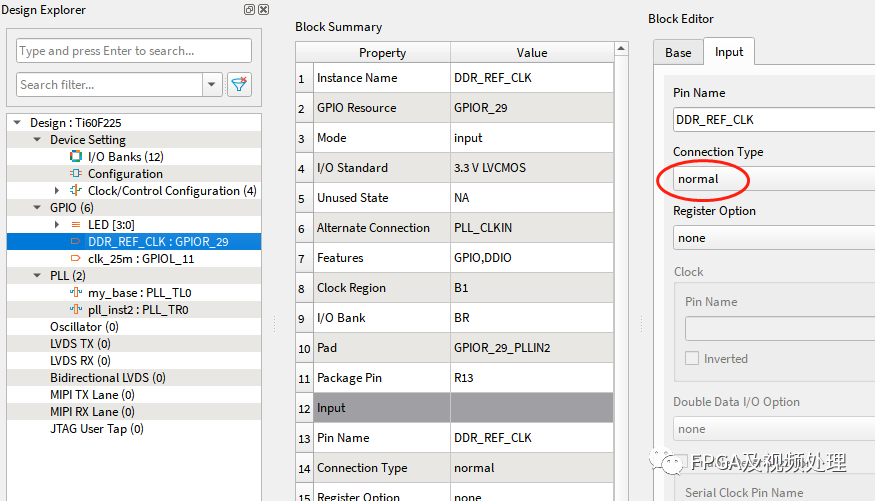

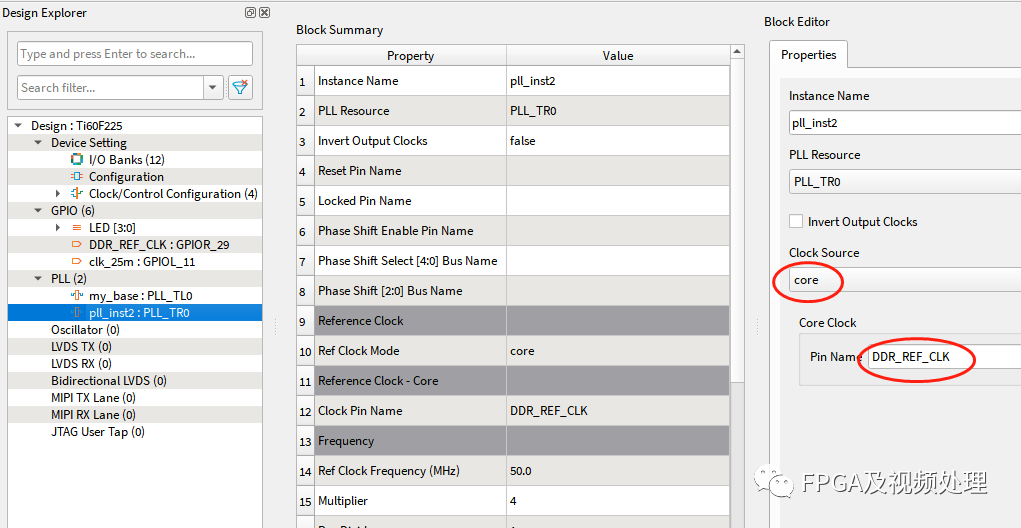

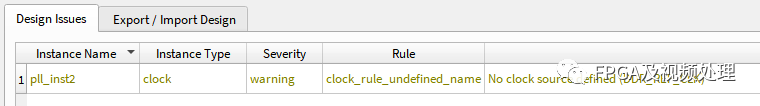

(2)如果放在了普通GPIO上,那Connection Type只能設(shè)置成Normal,同樣PLL的時(shí)鐘源設(shè)置成Core;不過會(huì)有警告信息clock_rule_undefined_name:No clock source defined(xxx)

Trion驗(yàn)證

有警告信息clock_rule_undefined_name:No clock source defined(hdmi_pclk )但是不用管。照用不誤。

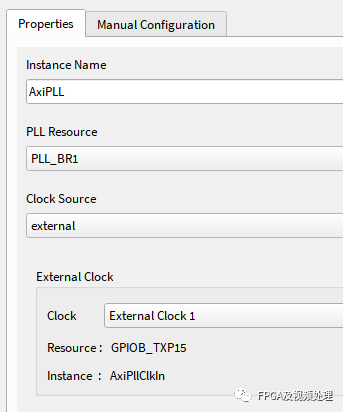

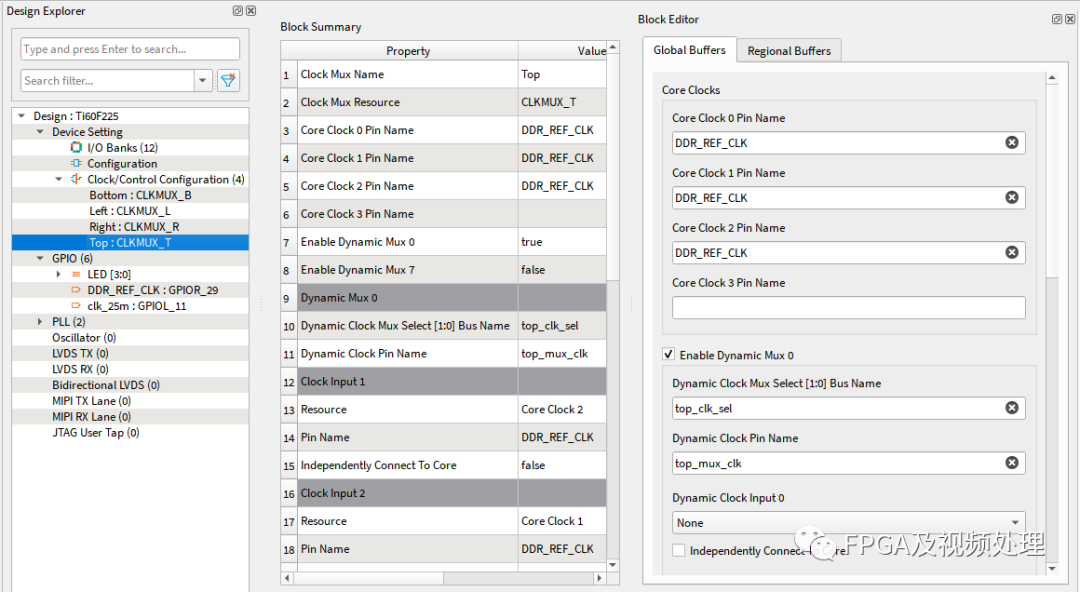

在鈦金上同樣可以這樣設(shè)置。

把DDR_REF_CLK設(shè)置為normal。

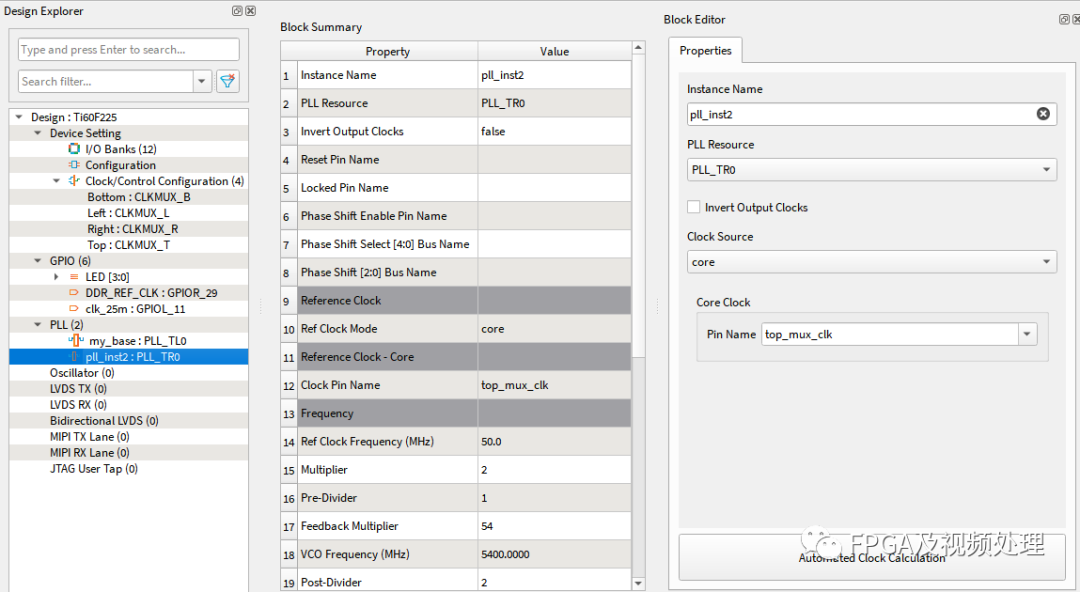

把PLL的參考修改成Core,并輸入時(shí)鐘名DDR_REF_CLK。

有警告信息clock_rule_undefined_name :No clock source defined(DDR_REF_CLK),但是不用管。照用不誤。

方法二:通過clkmux驅(qū)動(dòng)PLL

審核編輯:劉清

-

HDMI

+關(guān)注

關(guān)注

33文章

1818瀏覽量

154589 -

pll

+關(guān)注

關(guān)注

6文章

884瀏覽量

136077 -

GPIO

+關(guān)注

關(guān)注

16文章

1276瀏覽量

53608

原文標(biāo)題:GPIO驅(qū)動(dòng)PLL的

文章出處:【微信號:gh_ea2445df5d2a,微信公眾號:FPGA及視頻處理】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

使用兩塊LTM4613并聯(lián)時(shí),輸出電壓為6V,PLLIN管腳可以懸空嗎?

在quartus上想修改軟核PLL中設(shè)置,為什么打不開啊?

求助, nidec pll 驅(qū)動(dòng)電機(jī)

如何將PLL / BUFPLL保留在我的項(xiàng)目中

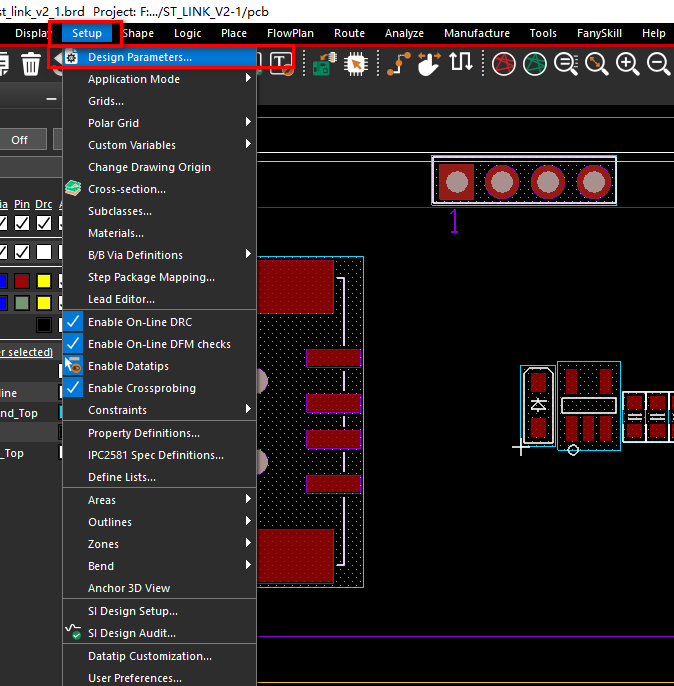

請問PCB板上的走線,器件管腳沒有網(wǎng)絡(luò)該怎么辦?

是否可以通過軟件在驅(qū)動(dòng)程序中交換/更改PLL?

PCB板上多長的走線才是傳輸線?

AN-910: 在ADAV801和ADAV803上恢復(fù)DIR PLL運(yùn)行

在FPGA上編寫的通過SPI總線配置外部PLL芯片AD9518和ADC9268的程序

基于T35F324的FPGA開發(fā)板圖像采集顯示系統(tǒng)方案

Cadence Allegro 22.1-1-3-將網(wǎng)絡(luò)顯示在焊盤、走線、銅皮上

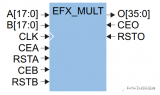

Trion DSP 原語使用問題 - 1

PLL用法

在Trion上驅(qū)動(dòng)PLL走pllin管腳

在Trion上驅(qū)動(dòng)PLL走pllin管腳

評論