大家在電子行業工作的工程師們,所做的產品多種多樣,所設計的電路模塊也多種多樣,那么有某些產品他的電路組成模塊就會設計到我們的高速電路,大家可能如果之前沒有接觸高速電路的話,可能對“高速”沒有概念,那么究竟速率多高才能稱為高速電路呢,平時我們應該如何區分高速和低速呢?

大家可能會認為信號周期頻率 FCLOCK 高的才屬于高速設計

其實我們在設計時考慮的最高頻率往往取決于信號的有效頻率(亦稱轉折頻率) Fknee

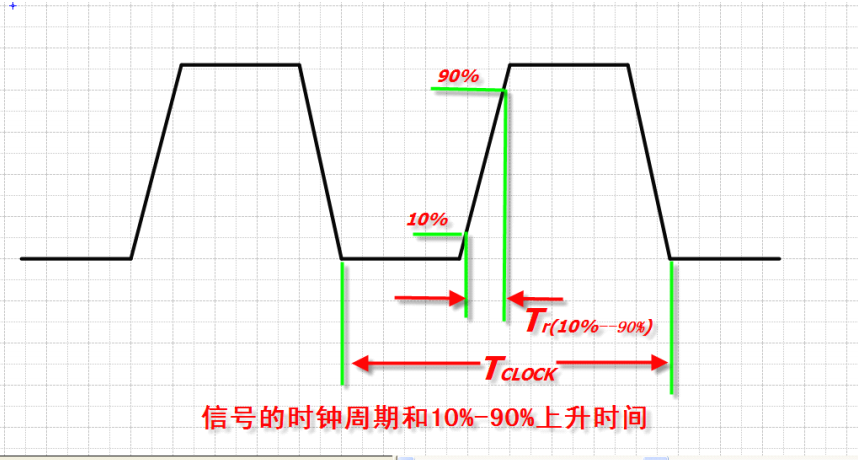

如上圖信號周期頻率與有效(轉折)頻率定義為:

FCLOCK = 1/Tclock

Fknee = 0.5/Tr(10%?90%) (實際中多數信號而言)

一般而言,在信號傳輸路徑的長度(即信號線的長度)小于信號的有效波長的 1/6 時, 可以認為在該傳輸路徑上,各點的電平狀態近似相同。由信號波長與頻率的關系 λ = c / F , 我們可以按下面的步驟進行高速低速的區分;1 獲得信號的有效頻率 Fknee 和走線長度 L; 2 利用 Fknee 計算出信號的有效波長 λknee;3 判斷 L 與 1/6λknee的關系,若 L>1/6λknee,則信號為高速信號;反之,則為低速信號。

總之,我們通常認為數字邏輯電路的頻率達到或者超過50MHz,而且工作在這個頻率之上的電路已經占到了整個電子系統相當的分量,例如三分之一,就稱為高速電路。而實際上,信號邊沿的諧波頻率比信號本身的頻率高,是信號快速變化的上升沿與下降沿引發了信號傳輸的各種問題。所以,當信號所在的傳輸路徑長度大于1/6倍傳輸信號的波長時,信號被認為是高速信號;當信號沿著傳輸線傳播時,發生了嚴重的趨膚效應和電離損耗時,認為是高速信號。因此,通常約定如果電路板上信號的傳播延遲大于一半數字信號驅動端的上升時間,則認為此類信號是高速信號并產生傳輸線效應,這樣的電路就是高速電路。

聲明:-

pcb

+關注

關注

4365文章

23480瀏覽量

409179

原文標題:平時我們所說的高速電路該怎么區分呢?

文章出處:【微信號:FANYPCB,微信公眾號:凡億PCB】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

從DLPA2000的規格書來看,可以設置UVLO閾值(2.3-4.5),請問這個閾值我們開發者該怎么設置呢?

如何用單片ADC和DAC去匹配改善電路呢?

電路中的主動元件,被動元件,有源器件,無源器件,分立元件,集成電路怎么區分?

在ads1261的通用c語言例程中的390行的if是用來區分什么的呢?

ADS8558無法實現高速采集,可能是哪些因素導致的,我們應該從哪些方面檢查呢?

lmv1012引腳怎么區分?DSBGA封裝怎么區分引腳?

如何區分元器件低頻和高頻

如何區分同向電路和反相電路

24V繼電器中常閉點和常開點如何區分

OPA2695具體功能和平時做的功放電路一樣嗎?

高速電路板的電容會并多大,要不要串電阻或者電感呢?

在實際應用中,如何區分電源紋波和噪聲?

平時我們所說的高速電路該怎么區分呢?

平時我們所說的高速電路該怎么區分呢?

評論