隨著微電子技術的迅猛發展,SRAM 逐漸呈現出高集成度、快速及低功耗的發展趨勢。在半導體存儲器的發展中,靜態存儲器(SRAM)由于其廣泛的應用成為其中不可或缺的重要一員。近年來SRAM在改善系統性能、提高芯片可靠性、降低成本等方面都起到了積極的作用。

在了解SRAM之前,有必要先說明一下RAM。RAM主要的作用就是存儲代碼和數據供CPU在需要的時候調用。但是這些數據并不是像用袋子盛米那么簡單,更像是圖書館中用書架擺放書籍一樣,不但要放進去還要能夠在需要的時候準確的調用出來,雖然都是書但是每本書是不同的。對于RAM等存儲器來說也是一樣的,雖然存儲的都是代表0和1的代碼,但是不同的組合就是不同的數據。

讓我們重新回到書和書架上來,如果有一個書架上有10行和10列格子(每行和每列都有0-9的編號),有100本書要存放在里面,那么我們使用一個行的編號+一個列的編號就能確定某一本書的位置。在RAM存儲器中也是利用了相似的原理。

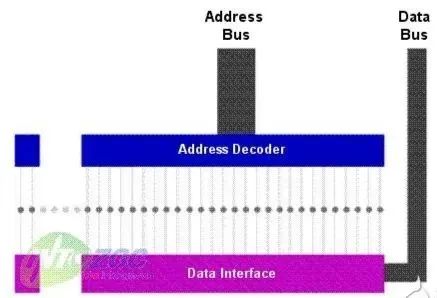

現在讓我們回到RAM存儲器上,對于RAM存儲器而言數據總線是用來傳入數據或者傳出數據的。因為存儲器中的存儲空間是如果前面提到的存放圖書的書架一樣通過一定的規則定義的,所以我們可以通過這個規則來把數據存放到存儲器上相應的位置,而進行這種定位的工作就要依靠地址總線來實現了。

對于CPU來說,RAM就像是一條長長的有很多空格的細線,每個空格都有一個唯一的地址與之相對應。如果CPU想要從RAM中調用數據,它首先需要給地址總線發送“編號”,請求搜索圖書(數據),然后等待若干個時鐘周期之后,數據總線就會把數據傳輸給CPU。

小圓點代表RAM中的存儲空間,每一個都有一個唯一的地址線同它相連。當地址解碼器接收到地址總線的指令:“我要這本書”(地址數據)之后,它會根據這個數據定位CPU想要調用的數據所在位置,然后數據總線就會把其中的數據傳送到CPU。

下面該介紹一下今天的主角SRAM:

SRAM——“Static RAM(靜態隨機存儲器)”的簡稱,所謂“靜態”,是指這種存儲器只要保持通電,里面儲存的數據就可以恒常保持。這里與我們常見的DRAM動態隨機存儲器不同,具體來看看有哪些區別:

SRAM VS DRAM

SRAM不需要刷新電路即能保存它內部存儲的數據。而DRAM(Dynamic Random Access Memory)每隔一段時間,要刷新充電一次,否則內部的數據即會消失。因此SRAM具有較高的性能,功耗較小。

此外,SRAM主要用于二級高速緩存(Level2 Cache)。它利用晶體管來存儲數據。與DRAM相比,SRAM的速度快,但在相同面積中SRAM的容量要比其他類型的內存小。

但是SRAM也有它的缺點,集成度較低,相同容量的DRAM內存可以設計為較小的體積,但是SRAM卻需要很大的體積。同樣面積的硅片可以做出更大容量的DRAM,因此SRAM顯得更貴。

還有,SRAM的速度快但昂貴,一般用小容量SRAM作為更高速CPU和較低速DRAM 之間的緩存。

總結一下:

SRAM成本比較高

DRAM成本較低(1個場效應管加一個電容)

SRAM存取速度比較快

DRAM存取速度較慢(電容充放電時間)

SRAM一般用在高速緩存中

DRAM一般用在內存條里

SRAM如何運作

剛才總結到了SRAM有著很特別的優點,你該好奇這家伙是怎樣的運作過程?

一個SRAM單元通常由4-6只晶體管組成,當這個SRAM單元被賦予0或者1的狀態之后,它會保持這個狀態直到下次被賦予新的狀態或者斷電之后才會更改或者消失。SRAM的速度相對比較快,且比較省電,但是存儲1bit的信息需要4-6只晶體管制造成本可想而知,但DRAM只要1只晶體管就可以實現。

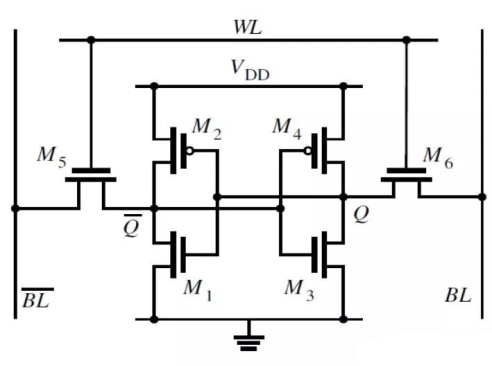

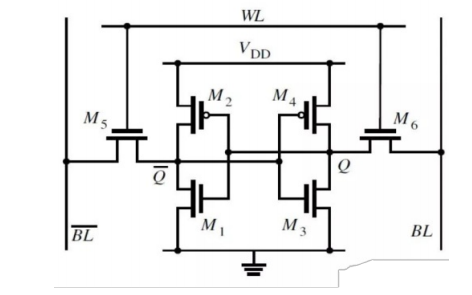

連接一下SRAM的結構,比較出名的是6場效應管組成一個存儲bit單元的結構:

M1-6表示6個晶體管,SRAM中的每一個bit存儲由4個場效應管M1234構成兩個交叉耦合的反相器中。一個SRAM基本單元有0、1 兩個狀態。

SRAM基本單元由兩個CMOS反相器組成,兩個反相器的輸入輸出交叉連接,即第一個反相器的輸出連接第二個反相器的輸入,第二個反相器的輸出連接第一個反相器的輸入。這實現了兩個反相器輸出狀態的鎖定、保存,即存儲了一個位元的狀態。

一般而言,每個基本單元的晶體管數量越少,其占用面積就會越小。由于硅晶圓生產成本相對固定,所以SRAM基本單元面積越小,在芯片上就可制造更多的位元存儲,每個位元存儲的成本就越低。

SRAM工作原理相對比較簡單,我們先看寫0和寫1操作。

寫0操作

寫0的時候,首先將BL輸入0電平,(~BL)輸入1電平。

然后,相應的Word Line(WL)選通,則M5和M6將會被打開。

0電平輸入到M1和M2的G極控制端

1電平輸入到M3和M4的G極控制端

因為M2是P型管,高電平截止,低電平導通。而M1則相反,高電平導通,低電平截止。

所以在0電平的作用下,M1將截止,M2將打開。(~Q)點將會穩定在高電平。

同樣,M3和M4的控制端將會輸入高電平,因NP管不同,M3將會導通,而M4將會截止。Q點將會穩定在低電平0。

最后,關閉M5和M6,內部M1,M2,M3和M4處在穩定狀態,一個bit為0的數據就被鎖存住了。

此時,在外部VDD不斷電的情況下,這個內容將會一直保持。

下面通過動畫來觀察一下寫0的過程。

寫1操作

這里不再重復,大家可以自己推演一下過程。這里仍然提供寫1過程動畫。

讀操作

讀操作相對比較簡單,只需要預充BL和(~BL)到某一高電平,然后打開M5和M6,再通過差分放大器就能夠讀出其中鎖存的內容。

**SRAM行業發展趨勢 **

隨著處理器日趨強大,尺寸越發精巧。然而更加強大的處理器需要緩存進行相應的改進。與此同時每一個新的工藝節點讓增加嵌入式緩存變得艱巨起來。SRAM的6晶體管架構(邏輯區通常包含4個晶體管/單元)意味著每平方厘米上的晶體管的數量將會非常多。這種極高的晶體管密度會造成很多問題,其中包括:

SER:軟錯誤率;Processnode:工藝節點soft:軟錯誤

更易出現軟錯誤:工藝節點從130nm縮小到22nm后,軟錯誤率預計將增加7倍。

更低的成品率:由于位單元隨著晶體管密度的增加而縮小,SRAM區域更容易因工藝變化出現缺陷。這些缺陷將降低處理器芯片的總成品率。

更高的功耗:如果SRAM的位單元必需與邏輯位單元的大小相同,那么SRAM的晶體管就必須小于邏輯晶體管。較小的晶體管會導致泄露電流升高,從而增加待機功耗。

另一個技術發展趨勢可穿戴電子產品的出現。對于智能手表、健身手環等可穿戴設備而言,尺寸和功耗是關鍵因素。由于電路板的空間有限,MCU必須做得很小,而且必須能夠使用便攜式電池提供的微小電量運行。

片上緩存難以滿足上述要求。未來的可穿戴設備將會擁有更多功能。因此片上緩存將無法滿足要求,對外置緩存的需求將會升高。在所有存儲器選項中,SRAM最適合被用作外置緩存,因為它們的待機電流小于DRAM,存取速度高于DRAM和閃存。

對于所有類型的系統設計者來說,新興存儲技術都變得極為關鍵。AI和物聯網IoT芯片開始將它們用作嵌入式存儲器。大型系統已經在改變其架構,以采用新興的存儲器來替代當今的標準存儲器技術。這種過渡將挑戰行業,但將帶來巨大的競爭優勢。

今天,業界仍在尋找通用存儲器,隨著SoC工藝進步設計復雜度增加,嵌入式 SRAM也越來越多。在40nm SoC產品SRAM一般在20Mbits左右,當工藝發展到28nm時SRAM就增加到100Mbits。如果考慮AI產品,SRAM估計更多。如何更好的測試SRAM就成為量產測試的重中之重。這也是推理芯片的最佳方案,也是芯片設計者在設計中應該努力追求的目標。

為了應對這一市場變化,新興存儲器PB的發貨量將比其它傳統存儲技術增長得更快,促使其營收增長到360億美元。之所以會發生這種情況,很大程度上是因為這些新興的存儲器將占領當今主流技術(NOR閃存,SRAM和DRAM)的既有市場份額。新存儲器將取代分立存儲芯片和SoC中的嵌入式存儲器:包括ASIC,微控制器,甚至是計算處理器中的緩存。

到2030年,3D XPoint存儲器收入將飆升至超過250億美元,這主要是因為該技術的售價低于它所取代的DRAM。這也解釋了為什么離散MRAM / STT-MRAM芯片收入將增長到超過100億美元,或者說是2019年MRAM收入的近300倍。此外,預計電阻RAM(ReRAM)和MRAM將競爭取代SoC中的大量嵌入式NOR和SRAM,從而推動更大規模的收入增長。

目前,尚不清楚哪種存儲技術將成為這場戰斗的贏家。相變存儲器(PCM),ReRAM,鐵電RAM(FRAM),MRAM和許多尚未成熟的技術,每種都有各自的競爭優勢和劣勢。目前處于競爭行列的有將近100家公司,這些公司包括芯片制造商、技術許可方、晶圓代工廠和工具和設備制造商,幾乎覆蓋了半導

-

存儲器

+關注

關注

38文章

7647瀏覽量

167179 -

cpu

+關注

關注

68文章

11074瀏覽量

216842 -

sram

+關注

關注

6文章

784瀏覽量

115882

發布評論請先 登錄

STM32的程序和數據在Flash和SRAM上到底是如何存儲的

IMXRT1064智能外部存儲器引腳多路復用器是什么意思?

SRAM,SRAM原理是什么?

SRAM模塊,SRAM模塊結構原理是什么?

sram是什么,sram信息詳解

單片機、桌面電腦/PC、嵌入式系統的啟動思路對比。

sram作用

如何對SRAM?進行分類

SRAM與DRAM究竟有何區別?誰能成為存儲技術殺手锏

SRAM和DRAM到底有什么區別和SRAM的發展趨勢說明

如何使用 QDR(TM) II SRAM 和 DDR II SRAM 用戶手冊

到底什么是SRAM

到底什么是SRAM

評論