CSP封裝及演進

芯片封裝是半導體產業中的一個重要環節,它是芯片與外界信號互連的通道,同時對裸芯片起到固定、密封、散熱、保護等多種功能。

CSP封裝(Chip Scale Package)指芯片級封裝,其封裝尺寸和芯片核心尺寸基本相同,一般芯片面積與封裝面積的比例約在1:1.2以內。CSP封裝廣泛應用于手機等消費電子的AP處理器,以及存儲器芯片、射頻模組等。

這些芯片或模組逐步向多功能低功耗演進,同時尺寸向輕、薄、短、小方向發展,要求封裝IO密度和高速高頻性能提升的同時,依然保持輕薄的特性。導致CSP封裝結構,芯片組裝方式從WB打線,向FC倒裝芯片或混裝方式演進;單芯片封裝也逐步向多芯片,甚至堆疊方式演進。按照組裝方式,業界常把CSP封裝分成WBCSP和FCCSP兩大類。

CSP封裝分類

CSP基板的技術趨勢

CSP基板做為CSP封裝的重要載體,承載著信號互連、機械支撐、以及底部散熱的功能。

對應前文所述的CSP封裝主流應用領域,CSP基板有兩個主流演進方向。其中存儲器和應用處理器,為支持更多的IO接口同時縮小封裝尺寸,FCCSP基板需要持續減薄同時增加線路密度,這樣需求更薄的基板和更精細的線路制程。射頻模組,為獲取更好的信號和集成性能,基板層數持續提升,同時高頻材料的應用越來越廣泛。

CSP基板演進方向

CSP基板關鍵工藝挑戰

概括起來,CSP基板有四大關鍵工藝挑戰:超薄、精細線路、多層數,同時需要自動化生產來保障其質量穩定性。除此之外,微孔、高頻高速高穩定的板材、多種表面處理、阻焊,也是CSP基板的關鍵技術。

CSP基板關鍵技術

· 精細線路工藝

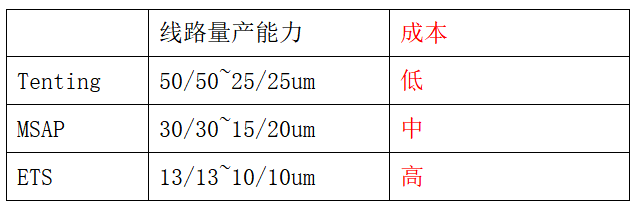

CSP基板精細線路的實現路徑,主要包括Tenting-減成法、MSAP-改良半加成法、ETS-埋線路三種制程。這三種制程的可實現的線路精細度不同,同時由于復雜度不同帶來的成本不同。其中,ETS屬于Coreless無芯基板制程,但制作的線路最精細。

興森同時具備這三種工藝能力,以匹配不同客戶從L/S 50/50~10/10μm各類產品需求。引進高解析度全自動LDI曝光機、垂直非接觸式MSAP顯影線等先進設備,ETS最小線寬/線距可做到10/10um。

· 超薄板

超薄板是存儲芯片、可穿戴設備的重要需求。興森科技具備最薄芯板0.035mm、無芯基板總厚70-90μm的加工能力。這需要工廠全線設備在設計上都具備對應能力。對于無芯基板,如圖4,制造過程中會使用一種叫Detach Core的支撐層材料。分離這層材料時,興森采用了自動分離機,分離速度快,精度高,可極大降低傳統手動分離導致的基板破損,折痕,翹曲等問題。

· 多層

CSP基板2-4層就能滿足大多數要求,但是射頻模塊等產品高頻信號、高集成,對基板層數也有更高要求,這在芯板很薄的前提下,挑戰很大。興森擁有成熟的層間對位和漲縮控制系統,高度自動化的疊合-壓合流程設備,可實現最高10層的CSP封裝基板量產。

· 多種表面處理

應對不同的應用場景,有不同的表面處理要求,為此,興森配備了完整的五種表面處理線體。

· 自動化

上述薄板精細線路和多層都是CSP封裝基板的關鍵技術挑戰,唯有高度自動化的產線,才能實現穩定高效的連續生產,保障產品高品質和快速交付。

審核編輯:劉清

-

處理器

+關注

關注

68文章

19833瀏覽量

233901 -

集成電路

+關注

關注

5420文章

11987瀏覽量

367542 -

存儲器

+關注

關注

38文章

7640瀏覽量

166639 -

CSP

+關注

關注

0文章

125瀏覽量

28652 -

芯片封裝

+關注

關注

11文章

576瀏覽量

31309

原文標題:硬干貨!深度剖析全球先進的集成電路CSP封裝基板

文章出處:【微信號:China_FASTPRINT,微信公眾號:興森科技】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

深度剖析全球先進的集成電路CSP封裝基板

深度剖析全球先進的集成電路CSP封裝基板

評論